# **External Memory Interface Handbook Volume 3**

# Section III. DDR2 and DDR3 SDRAM Controller with UniPHY User Guide

101 Innovation Drive San Jose, CA 95134 www.altera.com

EMI\_DDR3UP\_UG-2.0

Subscribe

## **Contents**

| Chapter 1. About This IP                 |     |

|------------------------------------------|-----|

| Release Information                      |     |

| Device Family Support                    |     |

| Features                                 |     |

| Unsupported Features                     |     |

| MegaCore Verification                    |     |

| Resource Utilization                     |     |

| System Requirements                      | 1–9 |

| Chapter 2. Getting Started               |     |

| Installation and Licensing               |     |

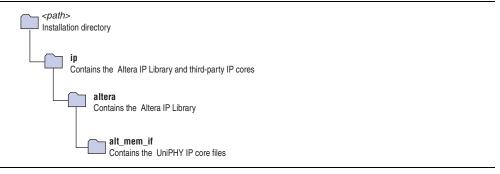

| Design Flows                             |     |

| MegaWizard Plug-In Manager Flow          |     |

| Specifying Parameters                    |     |

| Simulate the IP Core                     |     |

| SOPC Builder Design Flow                 |     |

| Specify Parameters                       |     |

| Complete the SOPC Builder System         |     |

| Qsys System Integration Tool Design Flow |     |

| Specify Parameters                       |     |

| Complete the Qsys System                 |     |

| Simulate the System                      |     |

| Qsys and SOPC Builder Interfaces         |     |

| Generated Files                          |     |

| MegaWizard Plug-in Manager Flow          |     |

| Synthesis                                |     |

| Simulation                               |     |

| Example Design Fileset                   |     |

| SOPC Builder Flow                        |     |

| Qsys Flow                                |     |

| Synthesis                                |     |

| Simulation                               |     |

| Chapter 3. Parameter Settings            |     |

| PHY Settings                             | 2 1 |

| O                                        |     |

| FPGA                                     |     |

| Clocks                                   |     |

| Advanced Settings                        |     |

| Memory Parameters                        |     |

| Memory Initialization Options—DDR2       |     |

| Mode Register 0                          |     |

| Mode Register 1                          |     |

| Mode Register 2                          |     |

| Memory Initialization Options—DDR3       |     |

| Mode Register 1                          |     |

| Mode Register 2                          |     |

| Mode Register 2                          |     |

| MEHIOLA HIMING                           |     |

Contents

| Board Settings                                   |      |

|--------------------------------------------------|------|

| Setup and Hold Derating                          |      |

| Intersymbol Interference                         |      |

| Board Skews                                      |      |

| Controller Settings                              |      |

| Avalon Interface                                 |      |

| Low Power Mode                                   | 3–10 |

| Efficiency                                       |      |

| Configuration, Status, and Error Handling        |      |

| Diagnostics                                      |      |

| Simulation Options                               |      |

| Efficiency Monitor and Protocol Checker Settings | 3–12 |

| Chapter 4. Constraining and Compiling            |      |

| Add Pin and DQ Group Assignments                 |      |

| Board Settings                                   |      |

| Compile the Design                               |      |

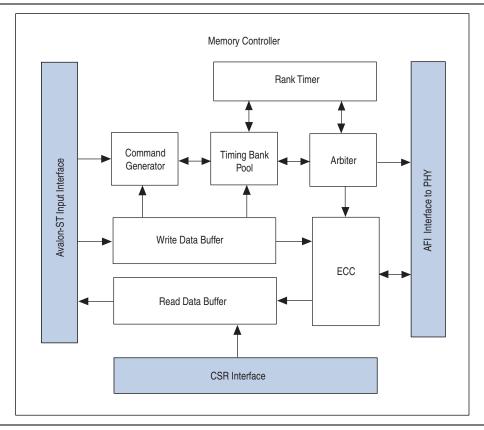

| Chapter 5. Functional Description—Controller     |      |

| Memory Controller Architecture                   | 5_1  |

| Avalon-ST Input Interface                        |      |

| Command Generator                                |      |

| Timing Bank Pool                                 |      |

| Arbiter                                          |      |

| Arbitration Rules                                |      |

| Rank Timer                                       |      |

| Read Data Buffer                                 |      |

| Write Data Buffer                                |      |

| ECC Block                                        |      |

| AFI Interface                                    |      |

| CSR Interface                                    |      |

| Controller Features Descriptions                 |      |

| Data Reordering                                  |      |

| Pre-emptive Bank Management                      |      |

| Quasi-1T and Quasi-2T                            |      |

| User Autoprecharge Commands                      |      |

| Address and Command Decoding Logic               |      |

| Low-Power Logic                                  |      |

| User-Controlled Self-Refresh                     |      |

| Automatic Power-Down with Programmable Time-Out  |      |

| ODT Generation Logic                             |      |

| DDR2 SDRAM                                       |      |

| DDR3 SDRAM                                       |      |

| ECC                                              |      |

| Partial Writes                                   |      |

| Partial Bursts                                   |      |

| External Interfaces                              |      |

| Clock and Reset Interface                        | 5–11 |

| Avalon-ST Data Slave Interface                   |      |

| Controller-PHY Interface                         | 5–11 |

| Memory Side-Band Signals                         | 5–11 |

| Self-Refresh (Low Power) Interface               | 5–11 |

| Usar Controlled Patroch Interface                | 5 12 |

| Configuration and Status Register (CSR) Interface                                                                                                                                                                                                                                                                                                                                                                      |                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Top-Level Signals Description                                                                                                                                                                                                                                                                                                                                                                                          | 5–13                                                                           |

| Sequence of Operations                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                |

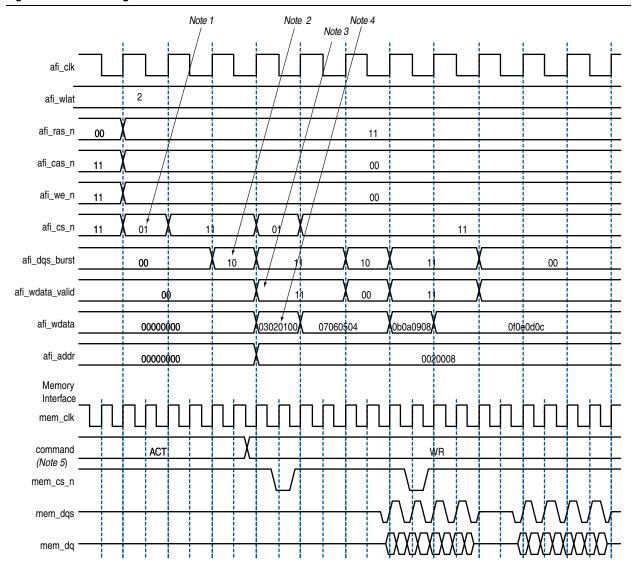

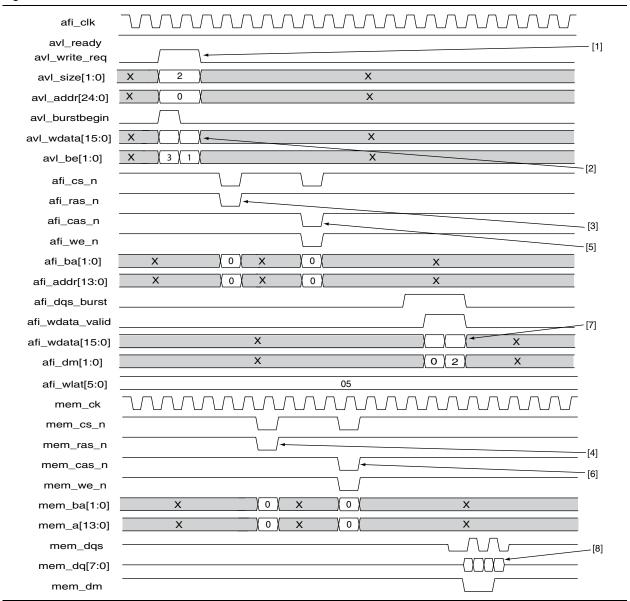

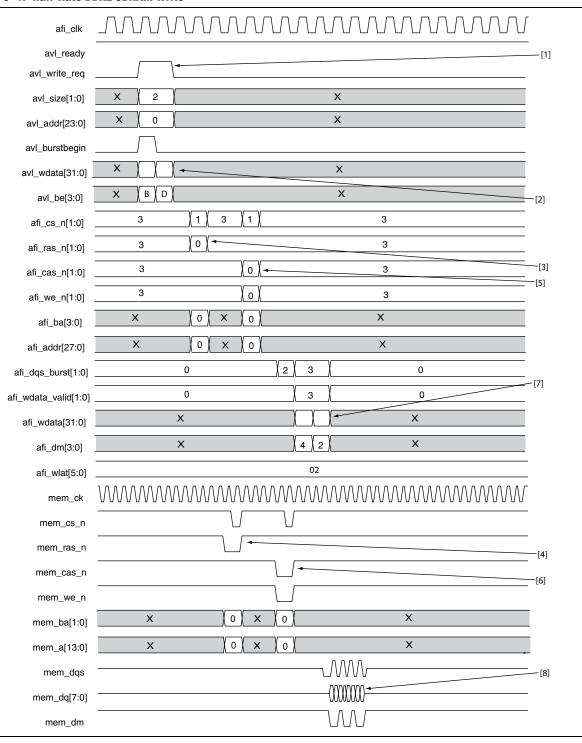

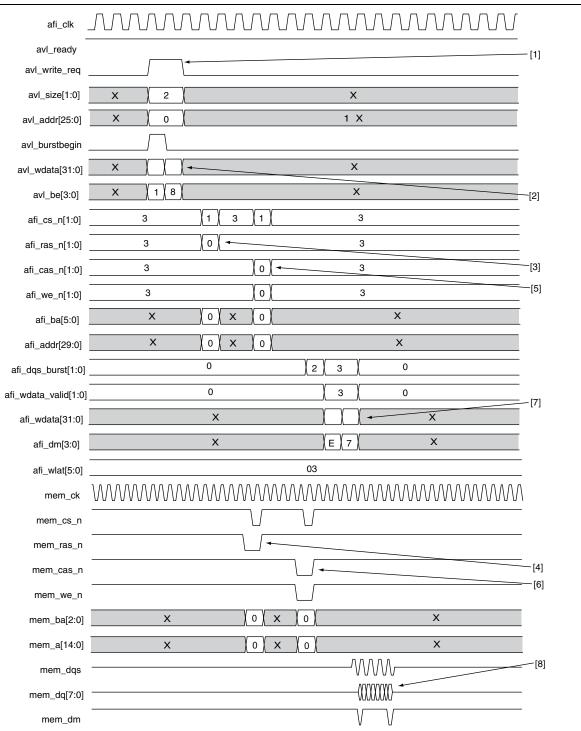

| Write Command                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |

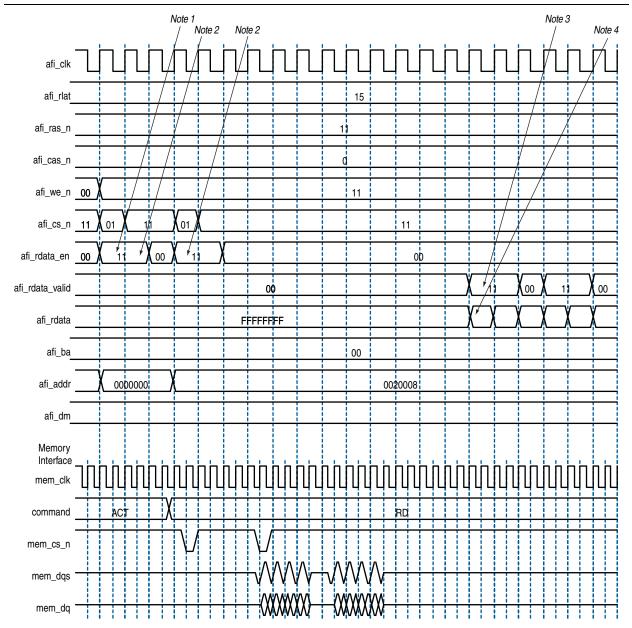

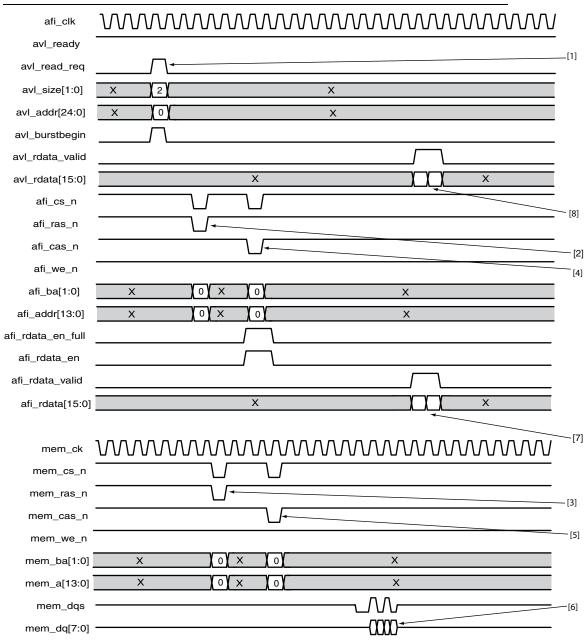

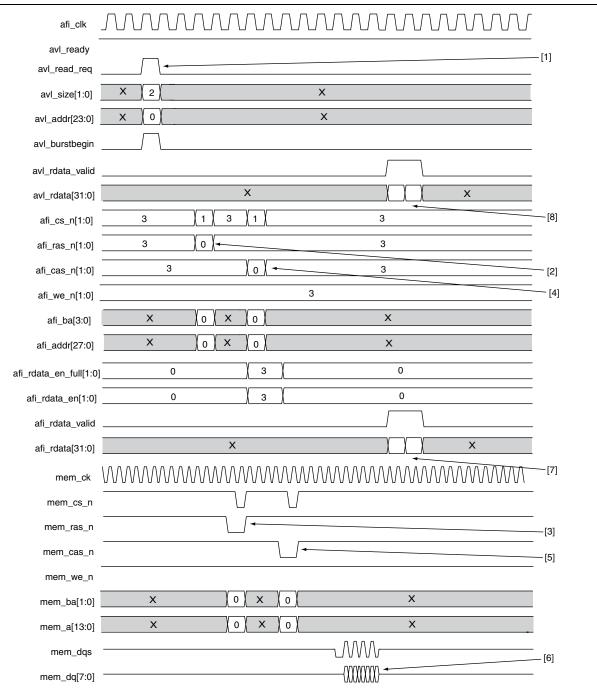

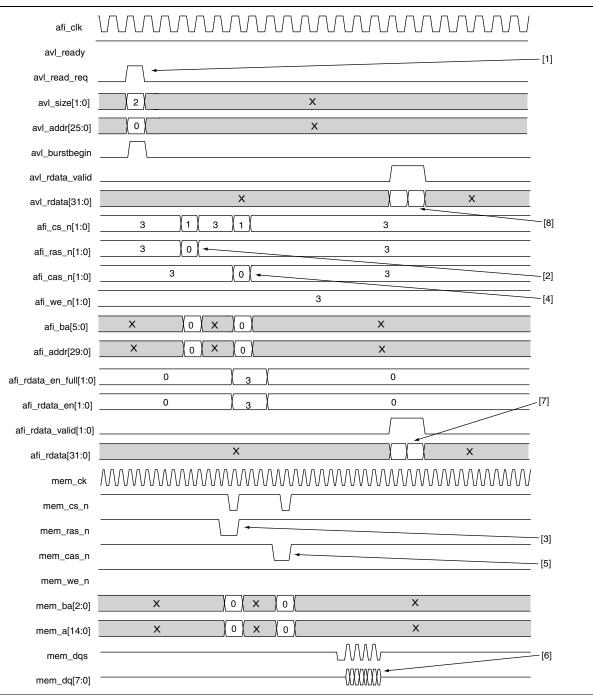

| Read Command                                                                                                                                                                                                                                                                                                                                                                                                           | 5–20                                                                           |

| Read-Modify-Write Command                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                |

| AFI 3.0 Specification                                                                                                                                                                                                                                                                                                                                                                                                  | 5–21                                                                           |

| Implementation                                                                                                                                                                                                                                                                                                                                                                                                         | 5–21                                                                           |

| Bus Width and AFI Ratio                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| AFI Parameters                                                                                                                                                                                                                                                                                                                                                                                                         | 5–22                                                                           |

| Parameters Affecting Bus Width                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                |

| AFI Signals                                                                                                                                                                                                                                                                                                                                                                                                            | 5–23                                                                           |

| Clock and Reset Signals                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| Address and Command Signals                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                |

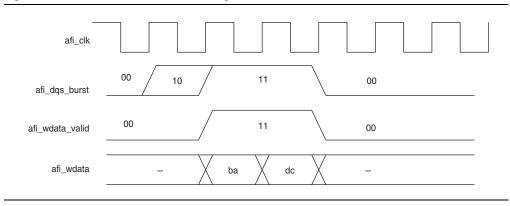

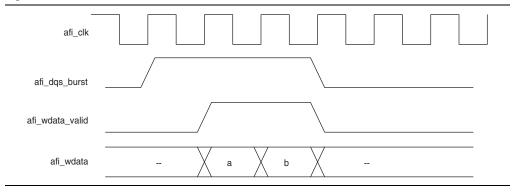

| Write Data Signals                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                |

| Read Data Signals                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                |

| Calibration Status Signals                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                |

| Tracking Management Signals                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                |

| Register Maps                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                |

| UniPHY Register Map                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                |

| Controller Register Map                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| Efficiency Monitor and Protocol Checker                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| Efficiency Monitor                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                |

| Protocol Checker                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                |

| Read Latency Counter                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| Using the Efficiency Monitor and Protocol Checker                                                                                                                                                                                                                                                                                                                                                                      |                                                                                |

| Avalon CSR Slave and JTAG Memory Map                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                |

| Chapter 6. Functional Description—UniPHY                                                                                                                                                                                                                                                                                                                                                                               |                                                                                |

| Chapter 6. Functional Description—UniPHY  Block Description                                                                                                                                                                                                                                                                                                                                                            | 6–1                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                |

| Block Description                                                                                                                                                                                                                                                                                                                                                                                                      | 6–1                                                                            |

| Block Description                                                                                                                                                                                                                                                                                                                                                                                                      | 6–1<br>6–2                                                                     |

| Block Description  I/O Pads  Reset and Clock Generation                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath                                                                                                                                                                                                                                                                                                                                  |                                                                                |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath                                                                                                                                                                                                                                                                                                                  |                                                                                |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath  Leveling Circuitry                                                                                                                                                                                                                                                                                              |                                                                                |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath                                                                                                                                                                                                                                                                                     | 6-1<br>6-2<br>6-3<br>6-4<br>6-6<br>6-6                                         |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function                                                                                                                                                                                                                                                                  | 6-1<br>6-2<br>6-3<br>6-4<br>6-4<br>6-6<br>6-7<br>6-7                           |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath  Leveling Circuitry  Read Datapath  Sequencer  Function  Architecture                                                                                                                                                                                                                                            |                                                                                |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath  Leveling Circuitry  Read Datapath  Sequencer  Function  Architecture  SCC Manager                                                                                                                                                                                                                               | 6-1<br>6-2<br>6-3<br>6-4<br>6-4<br>6-7<br>6-7<br>6-7<br>6-8                    |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager                                                                                                                                                                                                                              | 6-1 6-2 6-3 6-4 6-4 6-6 6-7 6-7 6-8                                            |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager                                                                                                                                                                                                                  | 6-1 6-2 6-3 6-4 6-4 6-6 6-7 6-7 6-8 6-9                                        |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager                                                                                                                                                                                                     | 6-1 6-2 6-3 6-4 6-4 6-5 6-7 6-7 6-8 6-9 6-9                                    |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Nios II Processor                                                                                                                                                                                   | 6-1 6-2 6-3 6-4 6-4 6-6 6-7 6-7 6-8 6-9 6-9                                    |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Nios II Processor DLL Offset Control Block                                                                                                                                                          | 6-1 6-2 6-3 6-4 6-4 6-4 6-7 6-7 6-8 6-9 6-9 6-10                               |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Nios II Processor DLL Offset Control Block Interfaces                                                                                                                                               | 6-1 6-2 6-3 6-4 6-4 6-4 6-5 6-7 6-7 6-9 6-9 6-10 6-11                          |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath  Leveling Circuitry  Read Datapath  Sequencer  Function  Architecture  SCC Manager  RW Manager  PHY Manager  Data Manager  Dota Manager  Nios II Processor  DLL Offset Control Block  Interfaces  AFI                                                                                                            | 6-1 6-2 6-3 6-4 6-4 6-4 6-6 6-7 6-7 6-8 6-9 6-9 6-10 6-11                      |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Dota Manager Nios II Processor DLL Offset Control Block Interfaces AFI The Memory Interface                                                                                                         | 6-1 6-2 6-3 6-4 6-4 6-4 6-6 6-7 6-7 6-8 6-9 6-9 6-10 6-12 6-12                 |

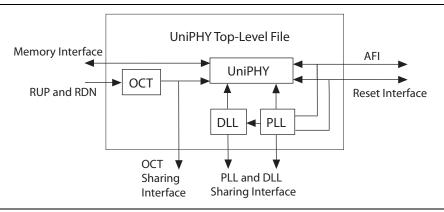

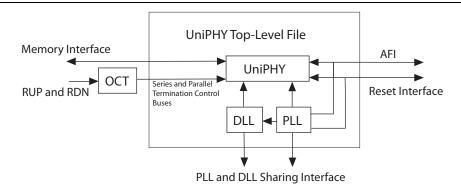

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Dota Manager Dota Manager Nios II Processor DLL Offset Control Block Interfaces AFI The Memory Interface The DLL and PLL Sharing Interface                                                          | 6-1 6-2 6-3 6-4 6-4 6-4 6-5 6-7 6-7 6-8 6-9 6-9 6-10 6-12 6-12                 |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Data Manager Dots More Control Block Interfaces AFI The Memory Interface The DLL and PLL Sharing Interface The OCT Sharing Interface                                                                | 6-1 6-2 6-3 6-4 6-4 6-4 6-6 6-7 6-7 6-8 6-9 6-10 6-12 6-14                     |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath  Leveling Circuitry  Read Datapath  Sequencer  Function  Architecture  SCC Manager  RW Manager  PHY Manager  Data Manager  Data Manager  Nios II Processor  DLL Offset Control Block  Interfaces  AFI  The Memory Interface  The DLL and PLL Sharing Interface  The OCT Sharing Interface  UniPHY Signals        | 6-1 6-2 6-3 6-4 6-4 6-4 6-6 6-7 6-7 6-7 6-9 6-10 6-12 6-14 6-15                |

| Block Description I/O Pads Reset and Clock Generation Address and Command Datapath Write Datapath Leveling Circuitry Read Datapath Sequencer Function Architecture SCC Manager RW Manager PHY Manager Data Manager Data Manager Nios II Processor DLL Offset Control Block Interfaces AFI The Memory Interface The DLL and PLL Sharing Interface The OCT Sharing Interface UniPHY Signals PHY-to-Controller Interfaces | 6-1 6-2 6-3 6-4 6-4 6-4 6-6 6-7 6-7 6-7 6-9 6-10 6-12 6-12 6-13 6-15           |

| Block Description  I/O Pads  Reset and Clock Generation  Address and Command Datapath  Write Datapath  Leveling Circuitry  Read Datapath  Sequencer  Function  Architecture  SCC Manager  RW Manager  PHY Manager  Data Manager  Data Manager  Nios II Processor  DLL Offset Control Block  Interfaces  AFI  The Memory Interface  The DLL and PLL Sharing Interface  The OCT Sharing Interface  UniPHY Signals        | 6-1 6-2 6-3 6-4 6-4 6-4 6-6 6-7 6-7 6-7 6-9 6-10 6-12 6-12 6-13 6-14 6-15 6-18 |

vi Contents

| Example Driver                                                                                                                                                                                                                                                                                                                                                              |                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

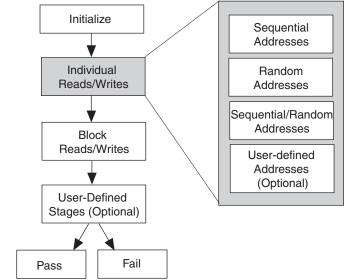

| Read and Write Generation                                                                                                                                                                                                                                                                                                                                                   |                                |

| Individual Read and Write Generation                                                                                                                                                                                                                                                                                                                                        |                                |

| Block Read and Write Generation                                                                                                                                                                                                                                                                                                                                             |                                |

| Address and Burst Length Generation                                                                                                                                                                                                                                                                                                                                         |                                |

| Sequential Addressing                                                                                                                                                                                                                                                                                                                                                       |                                |

| Random Addressing                                                                                                                                                                                                                                                                                                                                                           |                                |

| Sequential and Random Interleaved Addressing                                                                                                                                                                                                                                                                                                                                |                                |

| Example Driver Signals                                                                                                                                                                                                                                                                                                                                                      |                                |

| Example Driver Add-Ons                                                                                                                                                                                                                                                                                                                                                      |                                |

| User Refresh Generator                                                                                                                                                                                                                                                                                                                                                      |                                |

| Chapter 9. Timing Diagrams                                                                                                                                                                                                                                                                                                                                                  |                                |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v                                                                                                                                                                                                                                    |                                |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1                                                                                                                                                                                                                               | vith ALTMEMPHY Designs         |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1 Generating Equivalent Design                                                                                                                                                                                                  | vith ALTMEMPHY Designs10-1     |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base  Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1  Generating Equivalent Design                                                                                                                                                                                                | vith ALTMEMPHY Designs10–110–2 |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1 Generating Equivalent Design Replacing the ALTMEMPHY Datapath with UniPHY Datapath Resolving Port Name Differences                                                                                                            | vith ALTMEMPHY Designs         |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1 Generating Equivalent Design Replacing the ALTMEMPHY Datapath with UniPHY Datapath Resolving Port Name Differences Creating OCT Signals                                                                                       |                                |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1 Generating Equivalent Design Replacing the ALTMEMPHY Datapath with UniPHY Datapath Resolving Port Name Differences Creating OCT Signals Running Pin Assignments Script                                                        | vith ALTMEMPHY Designs         |

| 10–1 Generating Equivalent Design                                                                                                                                                                                                                                                                                                                                           | vith ALTMEMPHY Designs         |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base  Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1  Generating Equivalent Design  Replacing the ALTMEMPHY Datapath with UniPHY Datapath  Resolving Port Name Differences  Creating OCT Signals  Running Pin Assignments Script  Removing Obsolete Files  Simulating your Design | vith ALTMEMPHY Designs         |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1 Generating Equivalent Design Replacing the ALTMEMPHY Datapath with UniPHY Datapath Resolving Port Name Differences Creating OCT Signals Running Pin Assignments Script Removing Obsolete Files Simulating your Design         | vith ALTMEMPHY Designs         |

| Chapter 10. Upgrading to UniPHY-based Controllers from ALTMEMPHY-base Upgrading from DDR2 or DDR3 SDRAM High-Performance Controller II v 10–1 Generating Equivalent Design Replacing the ALTMEMPHY Datapath with UniPHY Datapath Resolving Port Name Differences Creating OCT Signals Running Pin Assignments Script Removing Obsolete Files                                | vith ALTMEMPHY Designs         |

The Altera® DDR2 and DDR3 SDRAM controllers with UniPHY provide low latency, high-performance, feature-rich controller interfaces to industry-standard DDR2 and DDR3 SDRAM memory. The DDR2 SDRAM controller with UniPHY offers full-rate and half-rate DDR2 interfaces, and the DDR3 SDRAM controller with UniPHY offers a half-rate DDR3 SDRAM interface.

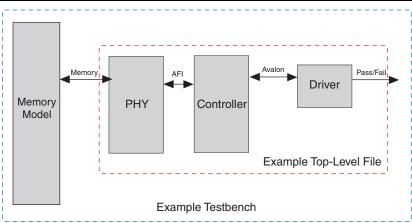

The MegaWizard™ interface generates an example top-level project, consisting of an example driver, and your DDR2 or DDR3 SDRAM controller custom variation. The controller instantiates an instance of the UniPHY datapath.

The example top-level project is a fully-functional design that you can simulate, synthesize, and use in hardware. The example driver is a self-test module that issues read and write commands to the controller and checks the read data to produce the pass, fail, and test-complete signals.

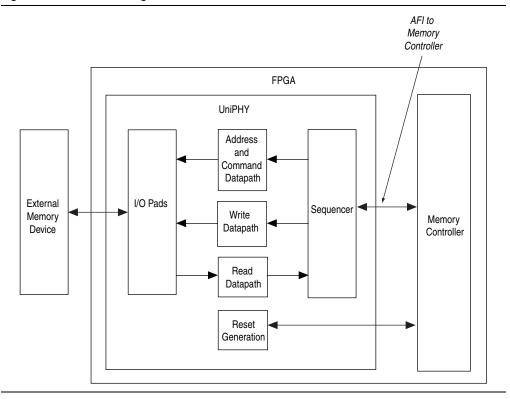

The UniPHY datapath is an interface between a memory controller and memory devices and performs read and write operations to the memory.

For device families not supported by the UniPHY-based designs, use the Altera ALTMEMPHY-based High Performance SDRAM Controller IP core.

If the UniPHY datapath does not match your requirements, you can create your own memory interface datapath using the ALTDLL, ALTDQ\_DQS, ALTDQ\_DQS2, ALTDQ, or ALTDQS megafunctions, available in the Quartus<sup>®</sup> II software, but you are then responsible for all aspects of the design including timing analysis and design constraints.

## **Release Information**

Table 1–1 provides information about this release of the DDR2 and DDR3 SDRAM controllers with UniPHY.

Table 1-1. Release Information

| Item           | Description |  |  |  |  |

|----------------|-------------|--|--|--|--|

| Version        | 11.0        |  |  |  |  |

| Release Date   | May 2011    |  |  |  |  |

| Ordaring Codes | IP-DDR2/UNI |  |  |  |  |

| Ordering Codes | IP-DDR3/UNI |  |  |  |  |

| Vendor ID      | 6AF7        |  |  |  |  |

Altera verifies that the current version of the Quartus II software compiles the previous version of each MegaCore function. The *MegaCore IP Library Release Notes and Errata* report any exceptions to this verification. Altera does not verify compilation with MegaCore function versions older than one release.

## **Device Family Support**

IP cores provide the following levels of support for target Altera device families:

- For FPGA device support:

- Preliminary—verified with preliminary timing models for this device

- Final—verified with final timing models for this device

- For ASIC devices (HardCopy families)

- HardCopy companion—verified with preliminary timing models for HardCopy companion device

- HardCopy compilation—verifed with final timing models for HardCopy device

For information about migrating your design to a HardCopy device, refer to "HardCopy Migration Design Guidelines", in section 6 of this volume.

Table 1–2 shows the level of support offered by the DDR2 and DDR3 SDRAM controllers to each of the Altera device families.

For information about features and supported clock rates for external memory interfaces, refer to the *External Memory Interface System Specifications* section in volume 1 of the *External Memory Interface Handbook* or use the *External Memory Specification Estimator*.

Table 1-2. Device Family Support

| Device Family                                                       | Support     |

|---------------------------------------------------------------------|-------------|

| Arria II GZ                                                         | Final       |

| HardCopy <sup>®</sup> III                                           | Companion   |

| HardCopy IV                                                         | Companion   |

| Stratix <sup>®</sup> III (For DDR3, only $V_{cc} = 1.1V$ supported) | Final       |

| Stratix IV                                                          | Final       |

| Stratix V                                                           | Preliminary |

| Other device families                                               | No support  |

## **Features**

Table 1–3 summarizes key feature support for the DDR2 and DDR3 SDRAM controllers with UniPHY.

Table 1-3. Key Feature Support for DDR2 and DDR3 SDRAM Controllers with UniPHY

| Key Feature                                                | DDR2 SDRAM UniPHY    | DDR3 SDRAM UniPHY        |

|------------------------------------------------------------|----------------------|--------------------------|

| High-performance controller II (HPC II)                    | ✓                    | ✓                        |

| Half-rate core logic and user interface                    | ✓                    | ✓                        |

| Full-rate core logic and user interface                    | ✓                    | _                        |

| Dynamically generated Nios II-based sequencer              | ✓                    | ✓                        |

| Available Efficiency Monitor and Protocol Checker          | ✓                    | ✓                        |

| Quarter-rate core logic and user interface (5)             | _                    | ✓                        |

| DDR3L support (5)                                          | _                    | ✓                        |

| UDIMM and RDIMM in any form factor (1) (2)                 | ✓                    | ✓                        |

| Multiple components in a single-rank UDIMM or RDIMM layout | ~                    | ~                        |

| Burst length in HPC II (half-rate)                         | 8                    | _                        |

| Burst length in HPC II (full-rate)                         | 4                    | _                        |

| Burst length of 8 and burst chop of 4 (on the fly)         | _                    | ✓                        |

| With leveling                                              | √(240 MHz and above) | √(240 MHz and above) (3) |

| Without leveling                                           | ✓(below 240 MHz)     | _                        |

| Maximum data width (4)                                     | 144 bits             | 144 bits                 |

#### Notes for Table 1-3:

- (1) For DDR3, the DIMM form is not supported in Arria II GX and Arria II GZ devices.

- (2) Arria II GZ uses leveling logic for discrete devices in DDR3 interfaces to achieve high speeds, but that leveling cannot be used to implement the DIMM form in DDR3 interfaces.

- (3) The leveling delay on the board between first and last DDR3 SDRAM component laid out as a DIMM must be less than 0.69 t<sub>CK</sub>.

- (4) For any interface with data width above 72 bits, you must use Quartus II software timing analysis of your complete design to determine the maximum clock rate.

- (5) For Stratix V devices only, beyond 533MHz.

## **Unsupported Features**

Table 1–4 summarizes unsupported features for the DDR2 and DDR3 SDRAM controllers with UniPHY.

Table 1–4. Unsupported Features for DDR2 and DDR3 SDRAM Controllers with UniPHY (Part 1 of 2)

| Memory Protocol Unsupported Feature |                     |  |  |

|-------------------------------------|---------------------|--|--|

|                                     | Timing simulation   |  |  |

| DDR2 SDRAM                          | Arria II GX support |  |  |

| DDRZ SDRAWI                         | Cyclone III support |  |  |

|                                     | Cyclone IV support  |  |  |

1–4 Chapter 1: About This IP

MegaCore Verification

Table 1–4. Unsupported Features for DDR2 and DDR3 SDRAM Controllers with UniPHY (Part 2 of 2)

| Memory Protocol | Unsupported Feature                  |  |  |  |

|-----------------|--------------------------------------|--|--|--|

|                 | Timing simulation                    |  |  |  |

|                 | Full-rate                            |  |  |  |

|                 | Arria II GZ DIMM in any form factor  |  |  |  |

| DDR3 SDRAM      | Stratix III (V <sub>cc</sub> = 0.9V) |  |  |  |

|                 | Arria II GX support                  |  |  |  |

|                 | Cyclone III support                  |  |  |  |

|                 | Cyclone IV support                   |  |  |  |

## **MegaCore Verification**

Altera has carried out extensive random, directed tests with functional test coverage using industry-standard models to ensure the functionality of the DDR2 and DDR3 SDRAM controllers with UniPHY. Altera's functional verification of DDR2 and DDR3 controllers with UniPHY use modified Denali models, with certain assertions disabled.

## **Resource Utilization**

This section lists resource utilization for the DDR2 and DDR3 SDRAM controllers with UniPHY for supported device families.

Table 1–5 shows the typical size of the DDR2 and DDR3 SDRAM controllers with UniPHY in the Quartus II software version 11.0 for Arria II GZ devices.

Table 1-5. Resource Utilization in Arria II GZ Devices (Part 1 of 2)

| Protocol            | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic<br>Registers | Mem<br>ALUTs | M9K<br>Blocks | M144K<br>Blocks | Memory<br>(Bits) |

|---------------------|---------------------------|------------------------|--------------------|--------------|---------------|-----------------|------------------|

| Controller          |                           |                        |                    |              |               |                 |                  |

|                     | 8                         | 1,781                  | 1,092              | 10           | 2             | 0               | 4,352            |

| DDR2                | 16                        | 1,784                  | 1,092              | 10           | 4             | 0               | 8,704            |

| (Half rate)         | 64                        | 1,818                  | 1,108              | 10           | 15            | 0               | 34,560           |

|                     | 72                        | 1,872                  | 1,092              | 10           | 17            | 0               | 39,168           |

|                     | 8                         | 1,851                  | 1,124              | 10           | 2             | 0               | 2,176            |

| DDR2                | 16                        | 1,847                  | 1,124              | 10           | 2             | 0               | 4,352            |

| (Full rate)         | 64                        | 1,848                  | 1,124              | 10           | 8             | 0               | 17,408           |

|                     | 72                        | 1,852                  | 1,124              | 10           | 9             | 0               | 19,574           |

|                     | 8                         | 1,869                  | 1,115              | 10           | 2             | 0               | 4,352            |

| DDR3<br>(Half rate) | 16                        | 1,868                  | 1,115              | 10           | 4             | 0               | 8,704            |

|                     | 64                        | 1,882                  | 1,131              | 10           | 15            | 0               | 34,560           |

|                     | 72                        | 1,888                  | 1,115              | 10           | 17            | 0               | 39,168           |

Table 1-5. Resource Utilization in Arria II GZ Devices (Part 2 of 2)

| Protocol            | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic<br>Registers | Mem<br>ALUTs | M9K<br>Blocks | M144K<br>Blocks | Memory<br>(Bits) |

|---------------------|---------------------------|------------------------|--------------------|--------------|---------------|-----------------|------------------|

| PHY                 |                           |                        |                    |              |               |                 | •                |

|                     | 8                         | 2,560                  | 2,042              | 183          | 22            | 0               | 157,696          |

| DDR2                | 16                        | 2,730                  | 2,262              | 183          | 22            | 0               | 157,696          |

| (Half rate)         | 64                        | 3,606                  | 3,581              | 183          | 22            | 0               | 157,696          |

|                     | 72                        | 3,743                  | 3,796              | 183          | 22            | 0               | 157,696          |

|                     | 8                         | 2,494                  | 1,934              | 169          | 22            | 0               | 157,696          |

| DDR2                | 16                        | 2,652                  | 2,149              | 169          | 22            | 0               | 157,696          |

| (Full rate)         | 64                        | 3,519                  | 3,428              | 169          | 22            | 0               | 157,696          |

|                     | 72                        | 3,646                  | 3,642              | 169          | 22            | 0               | 157,696          |

|                     | 8                         | 2,555                  | 2,032              | 187          | 22            | 0               | 157,696          |

| DDR3                | 16                        | 3,731                  | 2,251              | 187          | 22            | 0               | 157,696          |

| (Half rate)         | 64                        | 3,607                  | 3,572              | 187          | 22            | 0               | 157,696          |

|                     | 72                        | 3,749                  | 3,788              | 187          | 22            | 0               | 157,696          |

| Total               |                           |                        |                    |              | •             |                 |                  |

|                     | 8                         | 4,341                  | 3,134              | 193          | 24            | 0               | 4,374            |

| DDR2                | 16                        | 4,514                  | 3,354              | 193          | 26            | 0               | 166,400          |

| (Half rate)         | 64                        | 5,424                  | 4,689              | 193          | 37            | 0               | 192,256          |

|                     | 72                        | 5,615                  | 4,888              | 193          | 39            | 0               | 196,864          |

|                     | 8                         | 4,345                  | 3,058              | 179          | 24            | 0               | 159,872          |

| DDR2                | 16                        | 4,499                  | 3,273              | 179          | 24            | 0               | 162,048          |

| (Full rate)         | 64                        | 5,367                  | 4,552              | 179          | 30            | 0               | 175,104          |

|                     | 72                        | 5,498                  | 4,766              | 179          | 31            | 0               | 177,280          |

| DDR3<br>(Half rate) | 8                         | 4,424                  | 3,147              | 197          | 24            | 0               | 162,048          |

|                     | 16                        | 5,599                  | 3,366              | 197          | 26            | 0               | 166,400          |

|                     | 64                        | 5,489                  | 4,703              | 197          | 37            | 0               | 192,256          |

|                     | 72                        | 5,637                  | 4,903              | 197          | 39            | 0               | 196,864          |

Table 1–6 shows the typical size of the DDR2 and DDR3 SDRAM controllers with UniPHY in the Quartus II software version 11.0 for Stratix III devices.

Table 1–6. Resource Utilization in Stratix III Devices (Part 1 of 2)

| Protocol    | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic<br>Registers | Mem<br>ALUTs | M9K<br>Blocks | M144K<br>Blocks | Memory<br>(Bits) |

|-------------|---------------------------|------------------------|--------------------|--------------|---------------|-----------------|------------------|

| Controller  |                           |                        |                    |              |               |                 |                  |

|             | 8                         | 1,807                  | 1,058              | 0            | 4             | 0               | 4,464            |

| DDR2        | 16                        | 1,809                  | 1,058              | 0            | 6             | 0               | 8,816            |

| (Half rate) | 64                        | 1,810                  | 1,272              | 10           | 14            | 0               | 32,256           |

|             | 72                        | 1,842                  | 1,090              | 10           | 17            | 0               | 39,168           |

Table 1-6. Resource Utilization in Stratix III Devices (Part 2 of 2)

| Protocol    | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic<br>Registers | Mem<br>ALUTs | M9K<br>Blocks | M144K<br>Blocks | Memory<br>(Bits) |

|-------------|---------------------------|------------------------|--------------------|--------------|---------------|-----------------|------------------|

|             | 8                         | 1,856                  | 1,093              | 0            | 4             | 0               | 2,288            |

| DDR2        | 16                        | 1,855                  | 1,092              | 0            | 4             | 0               | 4,464            |

| (Full rate) | 64                        | 1,841                  | 1,092              | 0            | 10            | 0               | 17,520           |

|             | 72                        | 1,834                  | 1,092              | 0            | 11            | 0               | 19,696           |

|             | 8                         | 1,861                  | 1,083              | 0            | 4             | 0               | 4,464            |

| DDR3        | 16                        | 1,863                  | 1,083              | 0            | 6             | 0               | 8,816            |

| (Half rate) | 64                        | 1,878                  | 1,295              | 10           | 14            | 0               | 32,256           |

|             | 72                        | 1,895                  | 1,115              | 10           | 17            | 0               | 39,168           |

| PHY         |                           |                        |                    |              |               |                 |                  |

|             | 8                         | 2,591                  | 2,100              | 218          | 6             | 1               | 157,696          |

| DDR2        | 16                        | 2,762                  | 2,320              | 218          | 6             | 1               | 157,696          |

| (Half rate) | 64                        | 3,672                  | 3,658              | 242          | 6             | 1               | 157,696          |

|             | 72                        | 3,814                  | 3,877              | 242          | 6             | 1               | 157,696          |

|             | 8                         | 2,510                  | 1,986              | 200          | 6             | 1               | 157,696          |

| DDR2        | 16                        | 2,666                  | 2,200              | 200          | 6             | 1               | 157,696          |

| (Full rate) | 64                        | 3,571                  | 3,504              | 224          | 6             | 1               | 157,696          |

|             | 72                        | 3,731                  | 3,715              | 224          | 6             | 1               | 157,696          |

|             | 8                         | 2,591                  | 2,094              | 224          | 6             | 1               | 157,696          |

| DDR3        | 16                        | 2,765                  | 2,314              | 224          | 6             | 1               | 157,696          |

| (Half rate) | 64                        | 3,680                  | 3,653              | 248          | 6             | 1               | 157,696          |

|             | 72                        | 3,819                  | 3,871              | 248          | 6             | 1               | 157,696          |

| Total       |                           |                        |                    |              |               |                 |                  |

|             | 8                         | 4,398                  | 3,158              | 218          | 10            | 1               | 162,160          |

| DDR2        | 16                        | 4,571                  | 3,378              | 218          | 12            | 1               | 166,512          |

| (Half rate) | 64                        | 5,482                  | 4,930              | 252          | 20            | 1               | 189,952          |

|             | 72                        | 5,656                  | 4,967              | 252          | 23            | 1               | 196,864          |

|             | 8                         | 4,366                  | 3,079              | 200          | 10            | 1               | 159,984          |

| DDR2        | 16                        | 4,521                  | 3,292              | 200          | 10            | 1               | 162,160          |

| (Full rate) | 64                        | 5,412                  | 4,596              | 224          | 16            | 1               | 175,216          |

|             | 72                        | 5,565                  | 4,807              | 224          | 17            | 1               | 177,392          |

|             | 8                         | 4,452                  | 3,177              | 224          | 10            | 1               | 162,160          |

| DDR3        | 16                        | 4,628                  | 3,397              | 224          | 12            | 1               | 166,512          |

| (Half rate) | 64                        | 5,558                  | 4,948              | 258          | 20            | 1               | 189,952          |

|             | 72                        | 5,714                  | 4,986              | 258          | 23            | 1               | 196,864          |

Table 1–7 shows the typical size of the DDR2 and DDR3 SDRAM controllers with UniPHY in the Quartus II software version 11.0 for Stratix IV devices.

Table 1-7. Resource Utilization in Stratix IV Devices (Part 1 of 2)

| Protocol    | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic<br>Registers | Mem<br>ALUTs | M9K<br>Blocks | M144K<br>Blocks | Memory<br>(Bits) |

|-------------|---------------------------|------------------------|--------------------|--------------|---------------|-----------------|------------------|

| Controller  |                           |                        |                    |              |               |                 |                  |

|             | 8                         | 1,785                  | 1,090              | 10           | 2             | 0               | 4,352            |

| DDR2        | 16                        | 1,785                  | 1,090              | 10           | 4             | 0               | 8,704            |

| (Half rate) | 64                        | 1,796                  | 1,106              | 10           | 15            | 0               | 34,560           |

|             | 72                        | 1,798                  | 1,090              | 10           | 17            | 0               | 39,168           |

|             | 8                         | 1,843                  | 1,124              | 10           | 2             | 0               | 2,176            |

| DDR2        | 16                        | 1,845                  | 1,124              | 10           | 2             | 0               | 4,352            |

| (Full rate) | 64                        | 1,832                  | 1,124              | 10           | 8             | 0               | 17,408           |

|             | 72                        | 1,834                  | 1,124              | 10           | 9             | 0               | 19,584           |

|             | 8                         | 1,862                  | 1,115              | 10           | 2             | 0               | 4,352            |

| DDR3        | 16                        | 1,874                  | 1,115              | 10           | 4             | 0               | 8,704            |

| (Half rate) | 64                        | 1,880                  | 1,131              | 10           | 15            | 0               | 34,560           |

|             | 72                        | 1,886                  | 1,115              | 10           | 17            | 0               | 39,168           |

| PHY         |                           |                        |                    |              |               |                 | •                |

|             | 8                         | 2,558                  | 2,041              | 183          | 6             | 1               | 157,696          |

| DDR2        | 16                        | 2,728                  | 2,262              | 183          | 6             | 1               | 157,696          |

| (Half rate) | 64                        | 3,606                  | 3,581              | 183          | 6             | 1               | 157,696          |

|             | 72                        | 3,748                  | 3,800              | 183          | 6             | 1               | 157,696          |

|             | 8                         | 2,492                  | 1,934              | 169          | 6             | 1               | 157,696          |

| DDR2        | 16                        | 2,652                  | 2,148              | 169          | 6             | 1               | 157,696          |

| (Full rate) | 64                        | 3,522                  | 3,428              | 169          | 6             | 1               | 157,696          |

|             | 72                        | 3,646                  | 3,641              | 169          | 6             | 1               | 157,696          |

|             | 8                         | 2,575                  | 2,031              | 187          | 6             | 1               | 157,696          |

| DDR3        | 16                        | 2,732                  | 2,251              | 187          | 6             | 1               | 157,696          |

| (Half rate) | 64                        | 3,602                  | 3,568              | 187          | 6             | 1               | 157,696          |

|             | 72                        | 3,750                  | 3,791              | 187          | 6             | 1               | 157,696          |

| Total       |                           |                        |                    |              |               |                 | -1               |

|             | 8                         | 4,343                  | 3,131              | 193          | 8             | 1               | 162,048          |

| DDR2        | 16                        | 4,513                  | 3,352              | 193          | 10            | 1               | 166,400          |

| (Half rate) | 64                        | 5,402                  | 4,687              | 193          | 21            | 1               | 192,256          |

| ` '         | 72                        | 5,546                  | 4,890              | 193          | 23            | 1               | 196,864          |

|             | 8                         | 4,335                  | 3,058              | 179          | 8             | 1               | 159,872          |

| DDR2        | 16                        | 4,497                  | 3,272              | 179          | 8             | 1               | 162,048          |

| (Full rate) | 64                        | 5,354                  | 4,552              | 179          | 14            | 1               | 175,104          |

|             | 72                        | 5,480                  | 4,765              | 179          | 15            | 1               | 177,280          |

Chapter 1: About This IP

Resource Utilization

Table 1-7. Resource Utilization in Stratix IV Devices (Part 2 of 2)

1-8

| Protocol    | Memory<br>Width<br>(Bits) | Combinational<br>ALUTS | Logic<br>Registers | Mem<br>ALUTs | M9K<br>Blocks | M144K<br>Blocks | Memory<br>(Bits) |

|-------------|---------------------------|------------------------|--------------------|--------------|---------------|-----------------|------------------|

|             | 8                         | 4,437                  | 3,146              | 197          | 8             | 1               | 162,048          |

| DDR3        | 16                        | 4,606                  | 3,366              | 197          | 10            | 1               | 166,400          |

| (Half rate) | 64                        | 5,482                  | 4,699              | 197          | 21            | 1               | 192,256          |

|             | 72                        | 5,636                  | 4,906              | 197          | 23            | 1               | 196,864          |

Table 1–8 shows the typical size of the DDR2 and DDR3 SDRAM controllers with UniPHY in the Quartus II software version 11.0 for Stratix V devices.

Table 1-8. Resource Utilization in Stratix V Devices (Part 1 of 2)

| Protocol    | Memory<br>Width<br>(Bits) | Combinational<br>LCs | Logic<br>Registers | M20K<br>Blocks | Memory (Bits) |

|-------------|---------------------------|----------------------|--------------------|----------------|---------------|

| Controller  |                           |                      |                    |                |               |

|             | 8                         | 1,787                | 1,064              | 2              | 4,352         |

| DDR2        | 16                        | 1,794                | 1,064              | 4              | 8,704         |

| (Half rate) | 64                        | 1,830                | 1,070              | 14             | 34,304        |

|             | 72                        | 1,828                | 1,076              | 15             | 38,400        |

|             | 8                         | 2,099                | 1,290              | 2              | 2,176         |

| DDR2        | 16                        | 2,099                | 1,290              | 2              | 4,352         |

| (Full rate) | 64                        | 2,126                | 1,296              | 7              | 16,896        |

|             | 72                        | 2,117                | 1,296              | 8              | 19,456        |

|             | 8                         | 1,849                | 1,104              | 2              | 4,352         |

| DDR3        | 16                        | 1,851                | 1,104              | 4              | 8,704         |

| (Half rate) | 64                        | 1,853                | 1,112              | 14             | 34,304        |

|             | 72                        | 1,889                | 1,116              | 15             | 38,400        |

| PHY         |                           |                      |                    |                |               |

|             | 8                         | 2,567                | 1,757              | 13             | 157,696       |

| DDR2        | 16                        | 2,688                | 1,809              | 13             | 157,696       |

| (Half rate) | 64                        | 3,273                | 2,115              | 13             | 157,696       |

|             | 72                        | 3,377                | 2,166              | 13             | 157,696       |

|             | 8                         | 2,491                | 1,695              | 13             | 157,696       |

| DDR2        | 16                        | 2,578                | 1,759              | 13             | 157,696       |

| (Full rate) | 64                        | 3,062                | 2,137              | 13             | 157,696       |

|             | 72                        | 3,114                | 2,200              | 13             | 157,696       |

|             | 8                         | 2,573                | 1,791              | 13             | 157,696       |

| DDR3        | 16                        | 2,691                | 1,843              | 13             | 157,696       |

| (Half rate) | 64                        | 3,284                | 2,149              | 13             | 157,696       |

|             | 72                        | 3,378                | 2,200              | 13             | 157,696       |

Table 1–8. Resource Utilization in Stratix V Devices (Part 2 of 2)

| Protocol    | Memory<br>Width<br>(Bits) | Combinational<br>LCs | Logic<br>Registers | M20K<br>Blocks | Memory (Bits) |

|-------------|---------------------------|----------------------|--------------------|----------------|---------------|

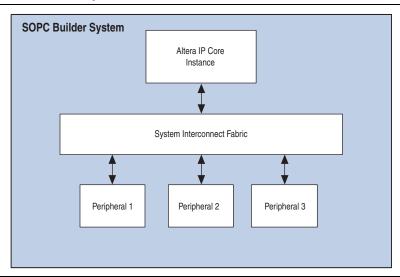

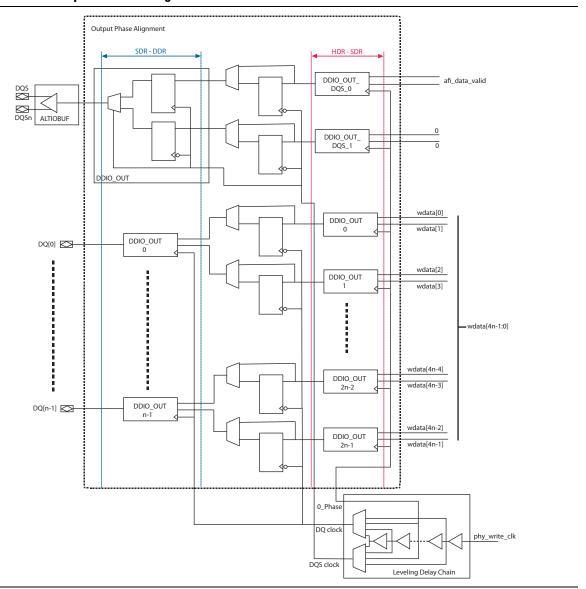

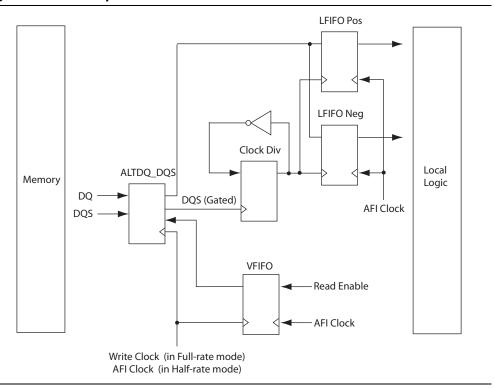

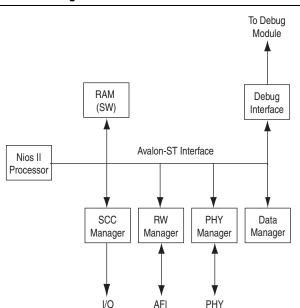

| Total       |                           |                      |                    |                |               |