# Intel Developer CORUM

## Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture

#### Steve Pawlowski

Intel Senior Fellow CTO, GM Architecture & Planning Digital Enterprise Group

#### Ofri Wechsler

Intel Fellow Director, CPU Architecture Mobility Group

Intel Developer FORUM

## Continuing From Last Fall's IDF...

Let's Take A Look Inside

# Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture The Energy Efficient Performance Leader

Source: Intel®

#### History

**XEON®** 2004

PENTIUM® M 2003

EM64T

XEONTM 2002

Power Management

Micro Fusion

POWEREFFICIENT

PENTIUM® III

1999

PENTIUM® 4 2000

**EPIC**

**PANTUM®**

2001

i486™ 1989

Integrated FPU

PENTIUM® 1993

Microarchitecture

and

Architecture

**Branch Prediction** Superscalar

PENTIUM® Pro

1995

Out Of Order Register Renaming

NetBurst™ SSE 2

SSE

PERFORMANCE

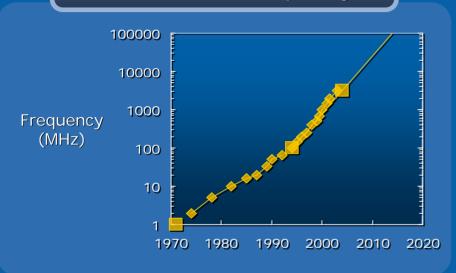

## **Historical Driving Forces**

**Increased Performance** via Increased Frequency

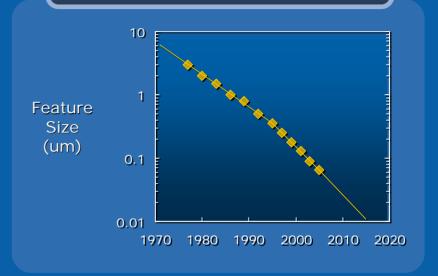

#### **Shrinking Geometry**

1946 20 Numbers in Main Memory

1971 14004 Processor 2300 Transistors

2005 65nm 1B+ Transistors

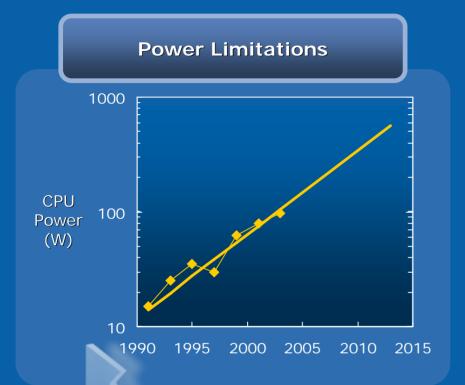

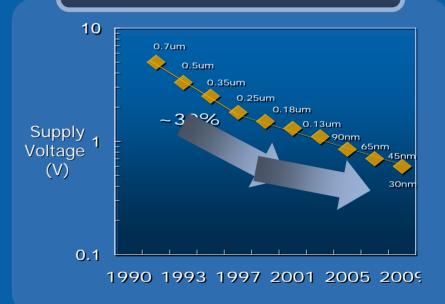

### The Challenges

#### **Diminishing Voltage Scaling**

Power = Capacitance x Voltage<sup>2</sup> x Frequency also

Power ~ Voltage<sup>3</sup>

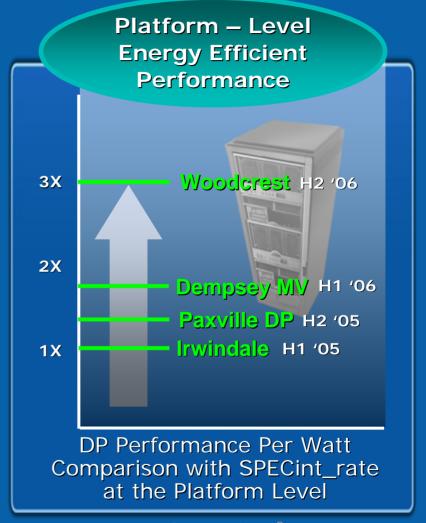

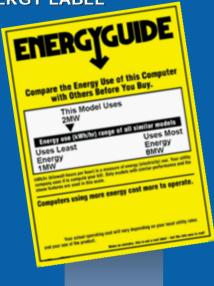

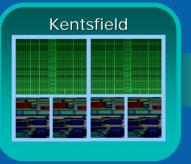

## **Energy Efficient Performance – High End**

DATACENTER

"ENERGY LABEL"

#### NASA Columbia

2 MWatt 60 TFlops goal 10,240 cpus – Itanium II **\$50M**

Source: NASA

30,720 Flops/Watt 1,288 Flops/Dollar

Computational Efficiency

17,066 Flops/Watt 467 Flops/Dollar

#### ASC Purple

6 MWatt 100 TFlops goal 12K+ cpus – Power5

\$230M

Source: LLNL

## A New Era...

THE NEW

THE OLD

Performance Equals Frequency

**Unconstrained Power**

**Voltage Scaling**

Performance Equals IPC Multi-Core

> Power Efficienc Microarchitecture Advancements

#### Intel<sup>®</sup> Core™ Microarchitecture

**Low Power** High Performance Scalable Woodcrest Intel® Wide **Dynamic** Server Execution **Optimized** Intel<sup>®</sup> Intelligent Power Conroe Capability Intel<sup>®</sup> Desktop Advanced **Optimized** 65nm **Smart Cache** Intel<sup>®</sup> Smart Memory Access Merom Intel<sup>®</sup> Mobile **Advanced Optimized Digital Media Boost**

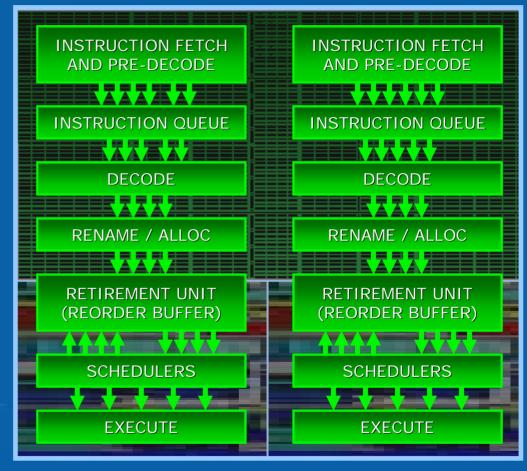

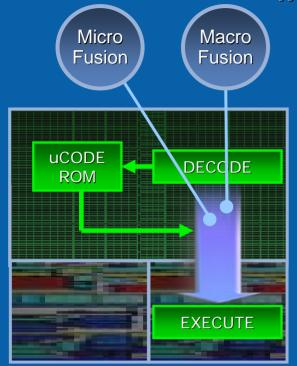

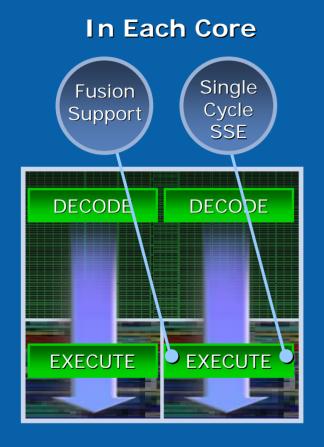

### Intel® Wide Dynamic Execution

**EACH CORE**

EFFICIENT 14 STAGE PIPELINE

DEEPER BUFFERS

> 4 WIDE -DECODE TO EXECUTE

4 WIDE -MICRO-OP EXECUTE

> MICRO and MACRO FUSION

ENHANCED ALUs CORE 1 CORE 2

**ADVANTAGE**

- 33% Wider Execution over Previous Gen

- Comprehensive Advancements

- Enabled In Each Core

## Intel® Wide Dynamic Execution

Micro and Macro Fusion

#### **MACRO FUSION EXAMPLE**

CMP+JMP IN 1 CLOCK

WITH MACRO FUSION

INSTRUCTION 3

INSTRUCTION 2

**INSTRUCTION 1**

**DECODE**

COMBINED INST 2 & 3

**INTERNAL INST 1**

**EXECUTE**

COMPLETED INST 3

**COMPLETED INST 2**

COMPLETED INST 1

WITHOUT MACRO FUSION

**INSTRUCTION 3**

**INSTRUCTION 2**

**INSTRUCTION 1**

**DECODE**

INTERNAL INST 3

**INTERNAL INST 2**

**INTERNAL INST 1**

**EXECUTE**

**COMPLETED INST 3**

**COMPLETED INST 2**

**COMPLETED INST 1**

Perf Energy

Intel Developer

**ADVANTAGE**

- Instruction Load Reduced ~ 15%\*\*

- Micro-Ops Reduced ~ 10%\*\*

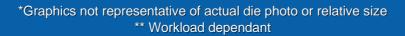

## Intel® Intelligent Power Capability

- 65nm

- Strained Silicon

- Low-K Dielectric

- More Metal Layers

- Aggressive

Clock Gating

- EnhancedSpeed-Step

- Low VCC Arrays

- Blocks Controlled Via Sleep Transistors

- Low Leakage Transistors

- SleepTransistors

ADVANTAGE

- Mobile-Level Power Management

- Energy Efficient Performance

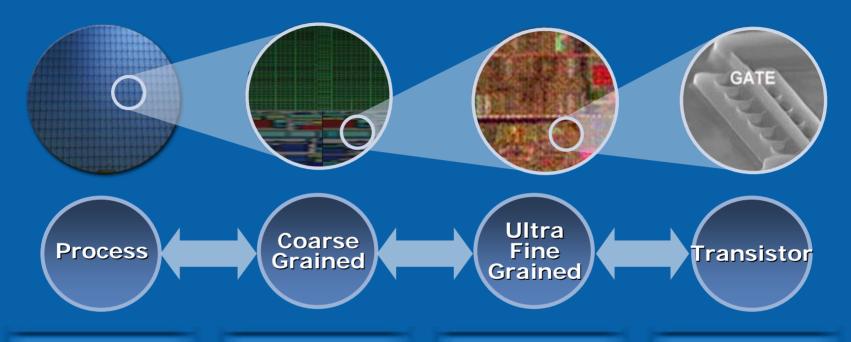

## Intel® Advanced Smart Cache

**Dynamic L2 Cache Usage**

Core<sup>™</sup> Microarchitecture **Shared L2** Decreased Traffic Dynamically, Bi-Directionally Available **CACHE** CACHE CORE 1 CORE 2

Independent L2

#### Intel® Smart Memory Access **Hardware-based Memory Disambiguation**

Core™ Microarchitecture Other INST 2 "LOAD [Y]" INST 2 "LOAD [Y]" IN **ORDER** INST 1 "STORE [X]" INST 1 "STORE [X]" **DECODE/SCHEDULE** DECODE/SCHEDULE INST 2 "LOAD [Y]" INST 2 "LOAD [Y]" INST 1 "STORE [X]" INST 1 "STORE [X]" OUT OF **HARDWARE ORDER** Mem. Dis. INST 2 "LOAD [Y]" Predictor **EXECUTE STALL** Inst. 2 Must INST 1 "STORE [X]" Wait For Inst. 1 "Store"

Inst. 2 "Load" Can Occur Before

Inst. 1 "Store"

• Higher Utilization of Pipeline

INST 1 "STORE [X]"

- Masks latency to data access

- Higher Performance

To Complete

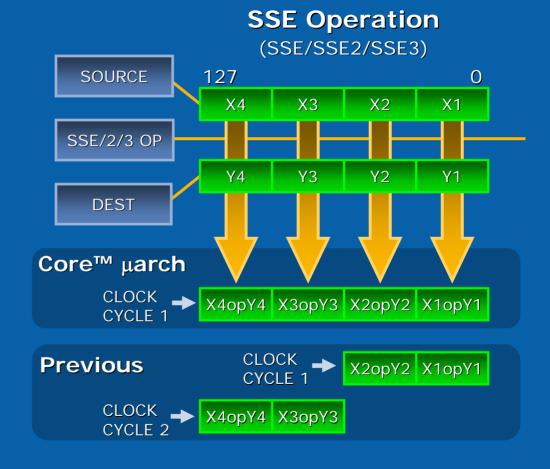

# Intel® Advanced Digital Media Boost Single Cycle SSE

- Increased Performance

- 128 bit Single Cycle in each core

- Improved Energy Efficiency

#### **Next Generation Platforms**

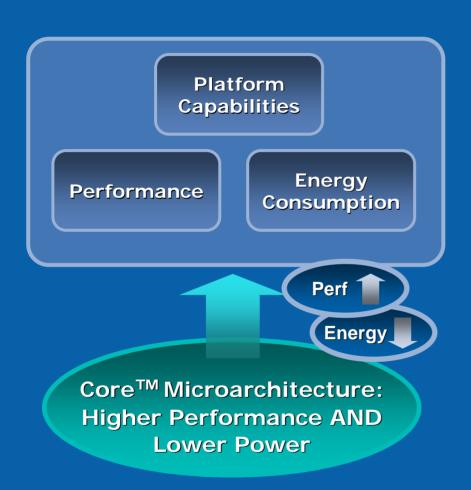

**Energy Efficient Performance**

#### Intel® Core™ Microarchitecture

Intel<sup>®</sup> Wide Dynamic Execution

Intel<sup>®</sup> Intelligent Power Capability

Intel<sup>®</sup> Advanced Smart Cache

Intel<sup>®</sup> Smart Memory Access

Intel<sup>®</sup>

Advanced

Digital Media

Boost

Server Optimized

Desktop Optimized

Mobile Optimized

- 80W Target TDP

- 40W LV Target TDP

- 2 Execution Cores

- 4MB L2 Cache

- Server Platform \*Ts

- DP Configurations

- 65W Mainstream TDP

- 2 Execution Cores

- 2MB & 4MB L2 Cache

- Desktop Platform \*Ts

- Mobile TDP

- 2 Execution Cores

- 2MB & 4MB L2 Cache

- Mobile Power Optimizations

- Mobile Platform \*Ts

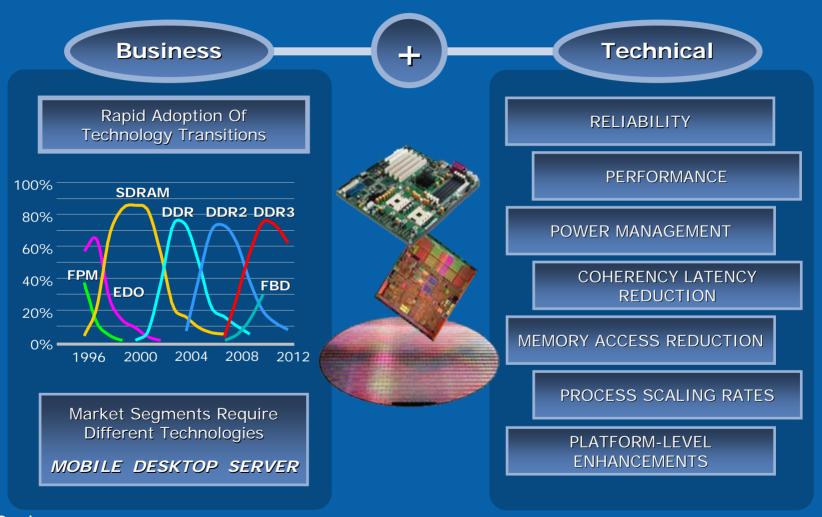

## Comprehensive Platform Architecture

Memory Controller Considerations

## **Comprehensive Platform Architecture**

#### MEMORY CONTROLLER CONSIDERATIONS

Memory Controller in Chipset

Extended RAS for Servers

Memory Closer to Integrated GFX, Smart Cache and Smart Memory Access

Centralized Coherency Control

CPU Power States w/ Memory Alive

MC vs Processor Device Scaling

IO Acceleration Technology

Technical

RELIABILITY

PERFORMANCE

MEMORY ACCESS REDUCTION

COHERENCY LATENCY REDUCTION

POWER MANAGEMENT

PROCESS SCALING RATES

PLATFORM-LEVEL ENHANCEMENTS

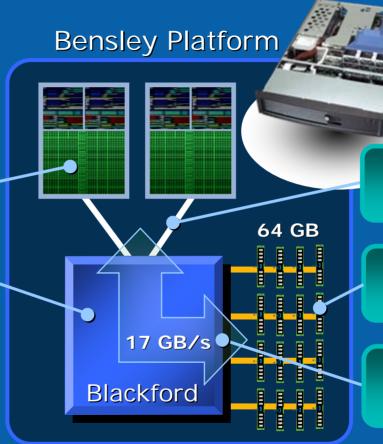

#### **DP Server Architecture**

FSB Scaling 800MHz 1067MHz 1333MHz

Large Shared Caches

Central Coherency Resolution

Local and Remote Memory Latencies Consistent

Platform

Performance:

It's all about

Bandwidth &

Latency

Point to Point Interconnect

Easy Capacity

Expansion

Sustained & Balanced Throughput

CONSTANTLY ANALYZING THE REQUIREMENTS, THE TECHNOLOGIES, AND THE TRADEOFFS

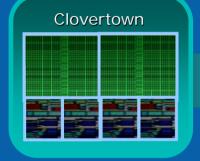

## Core™ Microarchitecture Advances With Quad Core

**Energy Efficient Performance**

Quad Core

Source: Intel®

# Developing for the Intel® Core™ Microarchitecture

# Further Insight Into Intel® Core<sup>TM</sup> Microarchitecture

- Core<sup>™</sup> Microarchitecture White Paper at rear of auditorium

- Intel®'s Core<sup>™</sup> Microarchitecture (Session, MATS001)

- Intel<sup>®</sup> Multi-Core Architecture and Implementations (Session, MATS002)

- Multi-Core and Core<sup>™</sup> Microarchitecture (Chalk Talk, MATC005)

- Shop Talk with Intel® Fellows tomorrow morning 8-9

- Technology Showcase

- Check out www.intel.com/multi-core