What is Intel® Dynamic Load Balancer (Intel® DLB)

Intel® DLB is a Peripheral Component Interconnect Express (PCIe) device that provides load-balanced, prioritized scheduling of events (packets) across CPU cores/threads enabling efficient core-to-core communication. It is a hardware accelerator located inside the latest Intel® Xeon® CPUs offered by Intel. Under the hood, Intel® DLB is a hardware managed system of queues and arbiters connecting producers and consumers. This article explores Intel® DLB and one exciting use case.

Why Intel® DLB

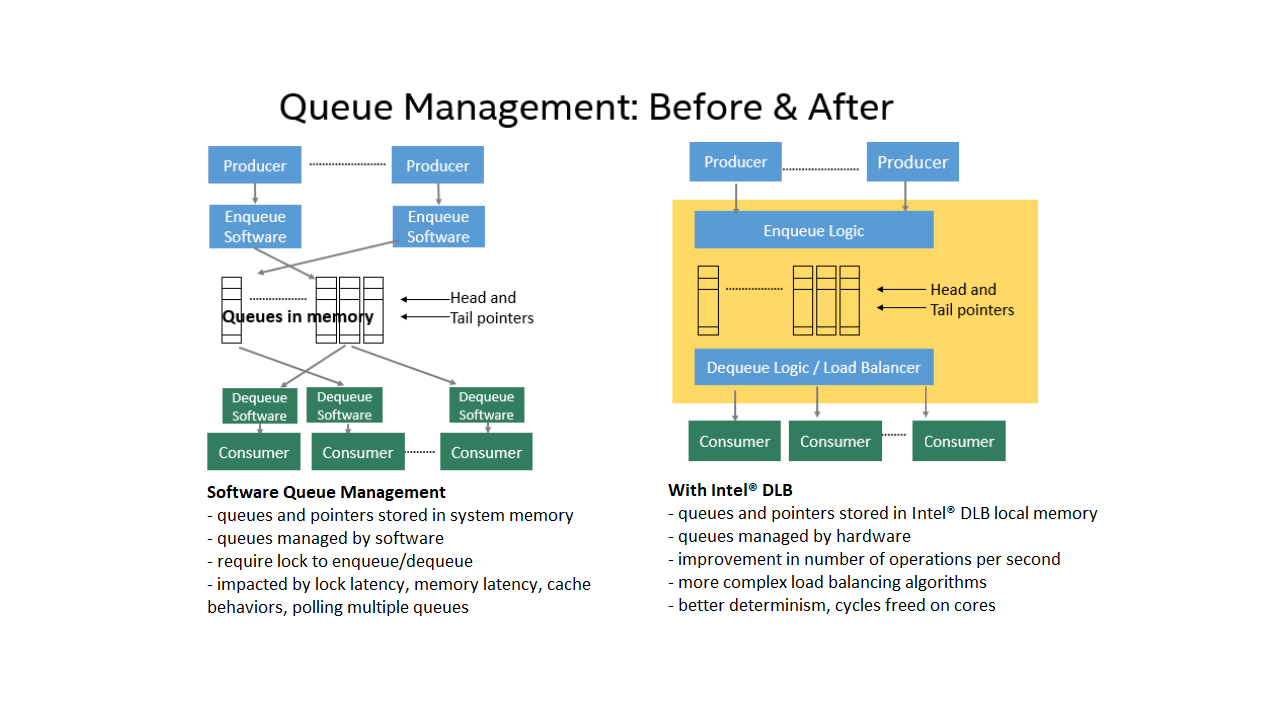

The following diagram shows a comparison of software vs Intel® DLB queueing implementation.

Intel® DLB value propositions is summarized below:

- Offloads Queue management from software - useful where there are significant queuing-based costs.

- Especially with Multi-Producer / Multi-Consumer scenarios & enqueue batching to multiple Destinations.

- Overhead of locks required to access shared queues in software. DLB implements lockless access to shared queues.

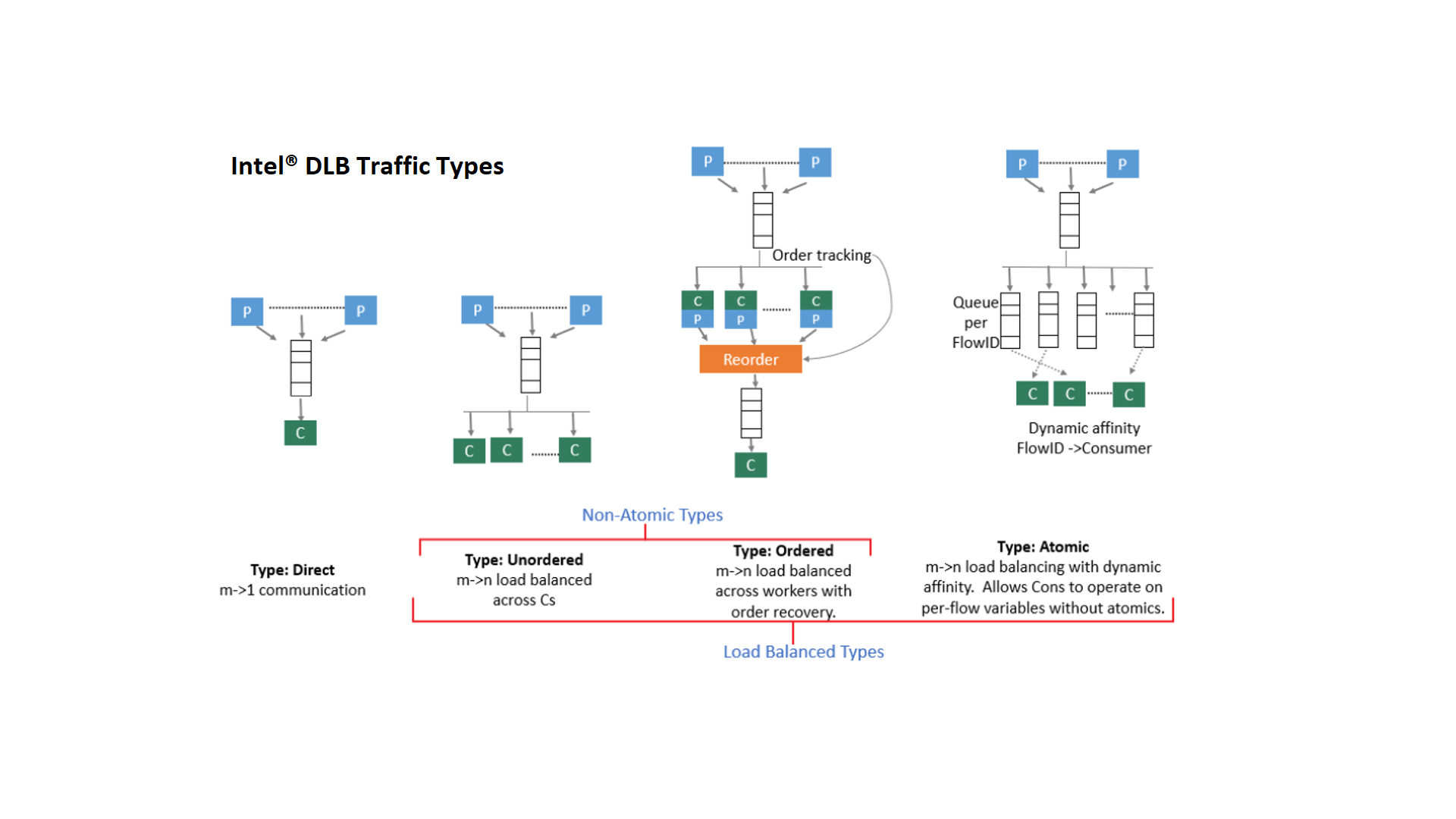

- Dynamic, flow aware load balancing & reordering.

- Ensures equal distribution of tasks and better CPU core utilization. Can provide flow based atomicity if required.

- Distributes high BW flows across many cores without loss of packet order

- Better determinism and avoids excessive Queuing latencies

- Lower IO memory footprint and saving of DDR BW

- Priority Queuing (up to 8 levels) - allows for QOS

- Lower latency for traffic that is latency sensitive

- Optional delay measurements in the packets

- Scalability

- Allows dynamic sizing of applications, seamless scale up/down.

- Power Aware: Application can drop workers to lower power state in cases of lighter load.

Data-plane software communicates with Intel® DLB using standard (PCI) memory mapped interfaces in a simple, low cycle-cost way that is enabled with Data Plane Development Kit (DPDK). DPDK is a collection of open-source software libraries originally developed by Intel. Intel® DLB supports the event-driven programming model of DPDK’s Event Device Library. DPDK includes performance-optimized implementations of software queue management and work distribution. Intel® DLB can also be accessed using Intel provided library and kernel driver without using DPDK.

Intel® DLB supports virtualization using industry-standard techniques and is exposed as part of the Virtual Network Function Infrastructure on an Intel® architecture platform. Intel® DLB further allows fine grained isolation between individual applications if necessary.

Different queue types supported by the Intel® DLB

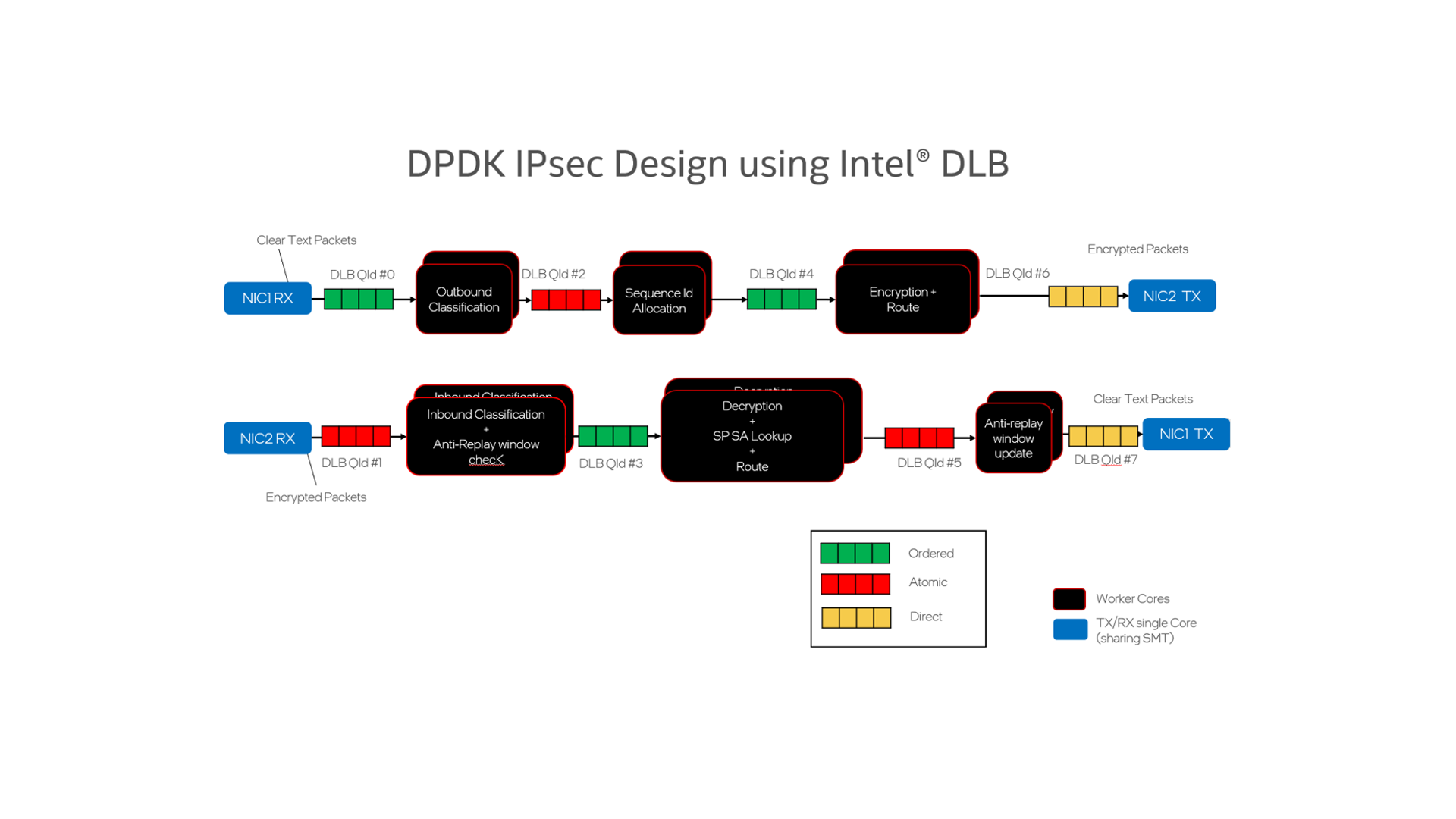

Intel® DLB IPSec Elephant flow application

Maximum supported bandwidth for an IPSec tunnel when processed in a Run-to-completion mode on a single core is limited by the capacity of single CPU core. To allow very high bandwidth tunnels, processing needs to be divided into multiple stages and these stages processed parallelly on multiple cores. This needs queuing between cores with atomic and reorder type support. Intel® DLB is most suitable in such cases as shown by following prototype.

Summary

Intel® DLB has the potential for very high-rate packet scheduling and queuing. It supports complex scheduling types such as reorder and atomic queues offloading CPU cycles. It offloads queue management, provides load balancing to handle elephant flows and reduces tail latencies, allowing scalability and saves memory bandwidth at the same time. It is best suited for high packet rate applications using pipelined architecture where queues are used to connect various software stages and load balancing and complex scheduling types are needed between stages. Use of Intel® DLB is not limited to such applications and Intel® DLB is finding its way in other areas as well.

Notices/Disclaimers

Performance varies by use, configuration and other factors. Learn more on the Performance Index site.

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Your costs and results may vary.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.