# High Endurance Technology in the Intel<sup>®</sup> Solid-State Drive 710 Series

Optimized solution for applications with high endurance requirements.

With solid-state drives (SSDs) becoming more prominent in data centers, there is an increased focus on SSD endurance – the ability of an SSD to withstand large amounts of data writes. The Intel® SSD 710 Series introduces a solution for these data center environments and endurance-focused applications: High Endurance Technology (HET). This technology, consisting of silicon-level and system- level optimizations, helps the Intel SSD 710 Series extend its endurance beyond what can be achieved using standard multi-level cell (MLC) NAND.

#### What is SSD endurance?

SSD endurance is the amount of data that can be written to an SSD during its lifetime. More specifically, it is the ability of an SSD to withstand multiple data writes within a set of criteria defined in the JEDEC *Solid State Drive (SSD) Requirements and Endurance Test Method* (JESD218) specification.

In JESD218, SSD endurance for data center applications is specified as the total amount of host data that can be written to an SSD, guaranteeing no greater than a specified error rate (1E-16) and data retention of no less than three months at 40  $^\circ$ C when the SSD is powered off.

#### What is High Endurance Technology?

After a large amount of program/erase (P/E) cycles on an SSD, data retention issues on individual NAND flash cells may occur. Additionally, increased read errors may happen when retrieving previously written data – wearing out the life of an SSD.

High Endurance Technology (HET), incorporated into the Intel SSD 710 Series, combines Intel<sup>®</sup> NAND Flash Memory silicon enhancements and SSD system management techniques to help extend the endurance of the SSD.

SSD endurance is dependent on the capacity of the SSD and the amount of P/E cycles its NAND flash cells can support. When a host issues a write command to an SSD, the SSD data management scheme may consume multiple P/E cycles on the NAND flash cell. The ratio of host writes to NAND writes during this operation is known as *write amplification*. For example, when writing 100 GB to an SSD, NAND flash cells may be written two times, resulting in 200 GB of NAND flash cell writes, which results in a write amplification of 2 (200 GB / 100 GB = 2). HET tries to extend inherent NAND flash cell P/E cycle capability while at the same time lowering write amplification, thereby increasing overall drive-level endurance.

#### Why is High Endurance Technology Needed?

Unlike typical client environments where a small amount of writes occur over the lifetime of an SSD, some data center applications have higher write requirements. An MLC NAND-based SSD without HET may be insufficient to meet these endurance needs of data center applications because standard MLC NAND flash cells without HET inherently contain less P/E cycle limits. Typical MLC NAND can fail to meet the data retention and bit error rate criteria specified in JESD218 at greater than its typical rated P/E cycle count.

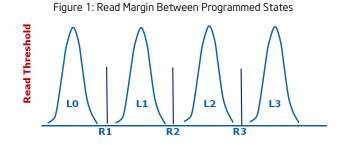

Based on different program pulses, a page of NAND flash cells is programmed at four different levels: L0, L1, L2 and L3. Figure 1 shows the probability distribution of each cell's threshold voltage level for a read after being programmed. The erased state of the cell is L0. The remaining levels are other programmed states. Read references (R1, R2, R3) are placed between these levels (L0, L1, L2, L3). The gap between each level is referred to as *read margin*.

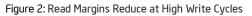

With more P/E cycles, read margin shrinks, resulting in both data retention problems and higher read errors beyond the limit specified by JESD218. This is caused by:

- Loss of charge due to flash cell oxide degradation

- Over-programming caused by erratic program steps

- Programming of adjacent erased cells due to heavy reads or writes in the locality of the NAND flash cell

An SSD targeted for client applications may try to overcome these issues using an on-board Error Correction Code (ECC) engine. However, once beyond a certain level of P/E cycles, these SSDs can fail to recover data near the end of life of the SSD. HET uses "beyond ECC" error recovery steps to cross this hurdle of ECC limitation and extend the MLC NAND capability to a higher P/E cycle count.

#### How is High Endurance Technology Achieved?

To extend the endurance of an SSD, the NAND P/E cycle limit needs to increase while system overhead during writes – which reflects on higher write amplification – needs to decrease. The Intel SSD 710 Series with HET contains NAND components that demonstrate high read margins and improved retention quality. At the SSD system level, special programming sequences are used to mitigate some of the program state disturb issues that may occur.

By using a scheme called *background data refresh*, the SSD moves data around during periods of inactivity to reallocate areas that have incurred heavy reads. This is in addition to the wear-leveling scheme that already exists in other Intel<sup>®</sup> SSDs.

NAND characterization and NAND program state disturb management schemes extend P/E cycle capability. Additionally, the SSD comes with extra spare area that lowers write amplification. The combined effect of these items allows the SSD to maintain endurance and retention required by data center applications.

## What Does High Endurance Technology Deliver?

Table 1 shows the endurance rating specifications for the Intel SSD 710 Series with HET.

|                        | 5 1                                                         |                                                                       |

|------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|

| 100 GB SSD             | 200 GB SSD                                                  | 300 GB SSD                                                            |

| 500/900 <sup>1</sup>   | 1,000/1,500 <sup>1</sup>                                    | 1,100/1,500 <sup>1</sup>                                              |

| terabytes              | terabytes                                                   | terabytes                                                             |

| 700/2,000 <sup>1</sup> | 1,000/1,900 <sup>1</sup>                                    | 1,500/3,000 <sup>1</sup>                                              |

| terabytes              | terabytes                                                   | terabytes                                                             |

|                        | 500/900 <sup>1</sup><br>terabytes<br>700/2,000 <sup>1</sup> | 500/9001 1,000/1,5001   terabytes terabytes   700/2,0001 1,000/1,9001 |

Table 1: Intel SSD 710 Series Endurance Rating Specifications

1. Value based on 20% over-provisioning

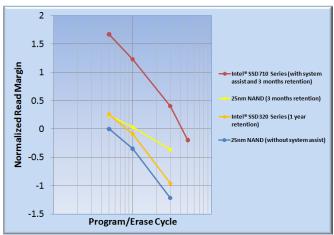

Figure 3 shows a plot of normalized read margin (the gap between levels) and terabytes written. To reach the uncorrectable bit error rate target and data retention target, normalized read margin needs to be at least above 0. Figure 3 shows how the Intel SSD 710 Series (with system assist and three months power-off retention) can extend the terabyte written limit. The figure also shows a clear distinction between the Intel<sup>®</sup> SSD 320 Series and Intel SSD 710 Series.

Figure 3: Normalized Read Margin for Intel® SSD 710 Series

### Measuring Estimated Life of Intel® SSD 710 Series

To monitor endurance on the Intel<sup>®</sup> SSD 710 Series, the SSD supports three SMART attributes: E2, E3, and E4. See the *Intel<sup>®</sup> Solid-State Drive 710 Series Product Specification* for more information on the SSD and these attributes.

Solid-State Computing Starts with Intel Inside.® For more information, visit www.intel.com/go/ssd

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2011 Intel Corporation. All rights reserved.

Printed in USA

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE POR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WAR-RANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked 'reserved' or 'undefined.' Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel. com/design/literature.htm