# Intel<sup>®</sup> X58 Express Chipset

**Specification Update**

May 2010

**Notice:** The Intel<sup>®</sup> X58 Express Chipset IOH may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Doc Number: 320839-013

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® X58 Express Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

Intel and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008-2009, Intel Corporation. All Rights Reserved.

### Contents

| Preface                      | 5  |

|------------------------------|----|

| Summary Tables of Changes    | 6  |

| Identification Information   |    |

| Errata                       |    |

| Specification Changes        |    |

| Specification Clarifications |    |

| Documentation Changes        | 30 |

| Revision | Description                                                                                                                                                                                            | Date          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| -001     | Initial Release.                                                                                                                                                                                       | November 2008 |

| -002     | Add errata 38-45                                                                                                                                                                                       | December 2008 |

| -003     | Added errata 46-49                                                                                                                                                                                     | January 2009  |

| -004     | Added B3 stepping and errata 51-60                                                                                                                                                                     | March 2009    |

| -005     | Updated Erratum 31                                                                                                                                                                                     | April 2009    |

| -006     | Added Errata 61-65                                                                                                                                                                                     | May 2009      |

| -007     | Removed Erratum 1<br>Added Errata 66 & 67                                                                                                                                                              | June 2009     |

| -008     | Added Errata 68 & 69                                                                                                                                                                                   | July 2009     |

| -009     | Added Erratum 70<br>Added Specification Clarification 1                                                                                                                                                | August 2009   |

| -010     | Added Specification Clarification 2                                                                                                                                                                    | October 2009  |

| -011     | Updated Erratum 61<br>Added C-2 Stepping Info<br>Added Figure 1: Top-Side Marking Example<br>Added Errata 71, 72, 73, 74, 75<br>Removed Documentation Changes 1, 2 (Included in<br>Datasheet Rev -004) | November 2009 |

| -012     | Updated Status for Erratum 5<br>Updated Workaround for Erratum 61                                                                                                                                      | December 2009 |

| -013     | Added Erratum 76<br>Added Documentation Change 1                                                                                                                                                       | May 2010      |

§

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device errata and documentation corrections, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

### **Affected Documents**

| Document Title                                   | Document Number/<br>Location |

|--------------------------------------------------|------------------------------|

| Intel <sup>®</sup> X58 Express Chipset Datasheet | 320838-004                   |

### Nomenclature

**Errata** are design defects or errors. These may cause the Intel® X58 Express Chipset IOH's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so forth).

# Summary Tables of Changes

The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the IOH product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables uses the following notations:

### **Codes Used in Summary Tables**

### Stepping

**Status**

| X:              | An erratum exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|-----------------|-------------------------------------------------------------------------------------------------------------------|

| (No mark)       |                                                                                                                   |

| or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.               |

| Doc:            | Document change or update will be implemented.                                                                    |

| Diana Elia      |                                                                                                                   |

| Plan Fix:This erratum may be fixed in a future stepping of the product.Fixed:This erratum has been previously fixed.No Fix:There are no plans to fix this erratum. | DOC.      | Document change of update will be implemented.                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------|

|                                                                                                                                                                    | Plan Fix: | This erratum may be fixed in a future stepping of the product. |

| No Fix: There are no plans to fix this erratum.                                                                                                                    | Fixed:    | This erratum has been previously fixed.                        |

|                                                                                                                                                                    | No Fix:   | There are no plans to fix this erratum.                        |

### Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### Errata (Sheet 1 of 3)

|        | Steppings B2 B3 C2 UP WS Only |   |       |        |                                                                                                           |  |

|--------|-------------------------------|---|-------|--------|-----------------------------------------------------------------------------------------------------------|--|

| Number |                               |   | UP WS | Status | Errata                                                                                                    |  |

| 1      | Х                             | х | Х     | No Fix | PCIe* Link bankwidth permanently set.                                                                     |  |

| 2      | Х                             | х | Х     | No Fix | CPURST bit does not get cleared by hardware                                                               |  |

| 3      |                               |   |       | Fixed  | PCIe RX LOs entry/exit issues.                                                                            |  |

| 4      | Х                             | Х | Х     | No Fix | V <sub>TX-RCV-DETECT</sub> pulse too large during receiver detection.                                     |  |

| 5      | х                             | х | х     | No Fix | PCIe Gen2 differential peak-to-peak transmit voltage swing is too low                                     |  |

| 6      | Х                             | Х | Х     | No Fix | Testlo[20] must be pulled high.                                                                           |  |

| 7      | Х                             | Х | Х     | No Fix | Surprise down error status not being flagged                                                              |  |

| 8      | х                             | х | х     | No Fix | Extended Error Detect Mask Registers of all PCIe root ports mask error logging by default.                |  |

| 9      | Х                             | Х | Х     | No Fix | Long XOR chain is broken                                                                                  |  |

| 10     | Х                             | Х | Х     | No Fix | PCIe Header of a malformed TLP is not logged                                                              |  |

| 11     | Х                             | Х | Х     | No Fix | PCIe PMCSR Power State fields allow writing D1 and D2                                                     |  |

| 12     | х                             | х | х     | No Fix | DEVCON2[3:0] and CTOCTRL not accurately set the completion timeout value.                                 |  |

| 13     |                               |   |       | Fixed  | In Intel® QuickPath Interconnect L1 Power management mode, Link layer sends retryable flits after L1.Ack. |  |

| 14     | х                             | Х | Х     | No Fix | PCIe Gen2 Tx Return loss fails spec                                                                       |  |

| 15     | х                             | х | Х     | No Fix | Persistent Jtag error reported at MIERRST register                                                        |  |

| 16     | Х                             | Х | Х     | No Fix | Interop issue of some PCIe Gen1 cards with Gen2 Devices                                                   |  |

| 17     |                               |   |       | Fixed  | PCIe ASPM L1 tests reporting lost credits                                                                 |  |

| 18     | х                             | х | х     | No Fix | Intel QuickPath Interconnect fails to retrain to L0 slow mode after 32 in-band resets                     |  |

| 19     |                               |   |       | Fixed  | ATS address field in the translation completion retuned in reversed byte order                            |  |

| 20     |                               |   |       | Fixed  | SLTCON bit 11 returning wrong value when read                                                             |  |

| 21     | Х                             |   |       | Fixed  | Boot-dependent Intel QuickPath Interconnect CRC errors                                                    |  |

| 22     | х                             | х | х     | No Fix | PCIe Inbound Msg that should be ignored is treated as Unsupported Request                                 |  |

| 23     | х                             | х | х     | Doc    | Memory writes to a certain address range are considered advisory non-fatal                                |  |

| 24     |                               |   |       | Fixed  | Inbound Write fetches may not make forward progress                                                       |  |

| 25     | Х                             | Х |       | Fixed  | PCIe lane-to-lane performance variation                                                                   |  |

| 26     | х                             | х | х     | No Fix | Transactions to addresses above TOCM are not setting the Master Abort                                     |  |

| 27     |                               |   |       | Fixed  | SERR_EN ignored during unsupported request error escalation                                               |  |

| 28     | х                             | х | х     | No Fix | Setting bits 24 and 25 of the MISCCTRLSTS does not result in expected behavior                            |  |

| 29     | Х                             | Х | Х     | No Fix | Timeout values much larger than specified                                                                 |  |

| 30     |                               |   |       | Fixed  | XPGLBERRPTR not accurately indicating first error in XPGLBERRSTS                                          |  |

| 31     | х                             | х | х     | No Fix | Failure during operation at PCI Express* L1 power management state                                        |  |

### Errata (Sheet 2 of 3)

|        | Steppings |    |                     |        |                                                                                                                   |  |

|--------|-----------|----|---------------------|--------|-------------------------------------------------------------------------------------------------------------------|--|

| Number | B2        | В3 | C2<br>UP WS<br>Only | Status | Errata                                                                                                            |  |

| 32     | Х         | Х  | х                   | No Fix | Bandwidth very low for write traffic with noSnoop attribute set                                                   |  |

| 33     | х         | х  | х                   | No Fix | Intel QuickPath Interconnect Queue/Table overflow or underflow error observed.                                    |  |

| 34     |           |    |                     | Fixed  | IOH Course Grained Clock Gating requires an ITP                                                                   |  |

| 35     | Х         |    |                     | Non-Si | Some Gen2 endpoints will not complete the training in Gen2 mode.                                                  |  |

| 36     |           |    |                     | Fixed  | Setting bit 10 of PCICMD register having effect on legacy interrupts                                              |  |

| 37     | х         | х  | x                   | No Fix | ACS Violation is not treated as Advisory when severity is set to Non-Fatal                                        |  |

| 38     | х         |    |                     | Fixed  | MIERRCNT does not properly count persistent SMBus retry failures and MINNERRST doesn't log the errors (HEDT only) |  |

| 39     | Х         | х  | Х                   | Х      | QPI L1 state is taking greater than 15 us from L1 exit to L0 state                                                |  |

| 40     | Х         |    |                     | Fixed  | EOI to the I/OxAPIC can be blocked                                                                                |  |

| 41     | Х         |    |                     | Fixed  | GTIME upper 32 bits can not be read or written.                                                                   |  |

| 42     | х         |    |                     | Fixed  | Intel® QuickPath Interconnect (QPI) LOs and L1 Power Management Link State Fails                                  |  |

| 43     | Х         |    |                     | Fixed  | PCI Express* 2.0 LOs Link Recovery Fails                                                                          |  |

| 44     | Х         |    |                     | Fixed  | IOH May Falsely Assert THERMTRIP_N Signal After a Reset Event                                                     |  |

| 45     | х         | х  | х                   | No Fix | Intel VT-d queue-based invalidation is enabled only when enabled on both channels (WS only)                       |  |

| 46     | х         | х  | х                   | No Fix | Intel VT-d does not support the draining of compatibility-format interrupts (WS only)                             |  |

| 47     | х         | х  | х                   | No Fix | Hardware applies HPA_LIMIT to upstream memory request when<br>Intel VT-d is disabled (WS only)                    |  |

| 48     | х         | х  | x                   | No Fix | Intel VT-d: Memory read request with AT=11 results in malformed TLP                                               |  |

| 49     |           |    |                     | Fixed  | Intel VT-d: IOTLB Domain-page-selective invalidation not working correctly.                                       |  |

| 50     | Х         | х  | Х                   | No Fix | Intel VT-d translated write transactions are blocked but not recorded.                                            |  |

| 51     | Х         |    |                     | Fixed  | The IOH Ignores Snoop Behavior Bit in VT-d Page Table.                                                            |  |

| 52     | х         | х  | х                   | No Fix | Intel QuickPath InterconnectLink Training failures in L0 when L0r enabled                                         |  |

| 53     | х         |    |                     | Fixed  | Intel VT-d reports an Invalidation Queue Error when the Queue size is 7 (HEDT only)                               |  |

| 54     | Х         | х  | Х                   | No Fix | ERRSID not logging ReqID for Inbound ERR_* messages                                                               |  |

| 55     | Х         | х  | х                   | No Fix | Intel QuickPath Interconnect PhyResets causing Intel QuickPath<br>Interconnect Errors to be flagged (HEDT only)   |  |

| 56     | Х         | х  | х                   | No Fix | Intel QuickPath Interconnect initialization abort failures logged during power-on resets                          |  |

| 57     | Х         | Х  | х                   | No Fix | Intel QuickPath Interconnect errors can occur on inband resets                                                    |  |

| 58     | х         | х  | x                   | No Fix | Data Mismatch on Inbound MemWrs after MSI with payload greater<br>than 1 DWORD payload                            |  |

| 59     | Х         | х  | х                   | No Fix | MSI with greater than 1DWord payload is not logged in XPUNCERRSTS bit 8                                           |  |

### Errata (Sheet 3 of 3)

|        | :  | Stepping | s                   |                                                                                                          |                                                                                                                                                                                                                 |  |

|--------|----|----------|---------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number | B2 | B3       | C2<br>UP WS<br>Only | Status                                                                                                   | Errata                                                                                                                                                                                                          |  |

| 60     | Х  | х        |                     | Fixed                                                                                                    | PFP Flag (due to Intel VT-d ISOCH fault) in Fault Status Register not being cleared                                                                                                                             |  |

| 61     | Х  | х        | Х                   | No Fix                                                                                                   | Lost interrupts when MSI used                                                                                                                                                                                   |  |

| 62     | х  | x        |                     | Fixed                                                                                                    | Intel VT-d: UP Workstation ONLY. Receiving two identical interrupt requests in back to back cycles may corrupt attributes of remapped interrupt, or hang subsequent interrupt-remap-cache invalidation command. |  |

| 63     | Х  | х        | Х                   | No Fix                                                                                                   | Intel QuickPath Interconnect Error Status D3 is observed                                                                                                                                                        |  |

| 64     | Х  | х        | Х                   | No Fix                                                                                                   | Unpredictable PCI behavior accessing non-existent memory space                                                                                                                                                  |  |

| 65     | х  | х        | Х                   | No Fix                                                                                                   | Bandwidth changed status errors being escalated to Global RAS                                                                                                                                                   |  |

| 66     | х  | Х        |                     | Fixed                                                                                                    | TXT writes may not complete as expected                                                                                                                                                                         |  |

| 67     | х  | х        |                     | Fixed                                                                                                    | IOTLB Invalidations not completing on Intel VT-d Isochronous unit<br>(UP WS ONLY)                                                                                                                               |  |

| 68     | х  | х        | х                   | No Fix                                                                                                   | Intel® VT-d: Address remapping error when DMA/interrupt remapping is active                                                                                                                                     |  |

| 69     | х  | х        | х                   | No Fix                                                                                                   | Intel® VT-d: In-flight remap-able interrupts not drained on interrupt invalidation command                                                                                                                      |  |

| 70     | х  | х        | х                   | No Fix                                                                                                   | Source ID for errors internally detected by PCIE root port 3 is not logged as expected                                                                                                                          |  |

| 71     | х  | х        | х                   | No Fix                                                                                                   | Device 0, Function 0's Revision ID (RID) is not reset to the Stepping Revision ID (SRID) by a CORERST_N Assertion                                                                                               |  |

| 72     | х  | х        | х                   | No Fix                                                                                                   | Header Log information may not be captured correctly when accessed via JTAG                                                                                                                                     |  |

| 73     | Х  | х        | х                   | No Fix                                                                                                   | Forwarded Clock Lane Detection status may not be indicated accurately                                                                                                                                           |  |

| 74     | Х  | х        | х                   | No Fix         Intel QuickPath Interconnect CRC errors experienced during entry could cause system hangs |                                                                                                                                                                                                                 |  |

| 75     | Х  | х        | х                   | No Fix                                                                                                   | ESI link cannot go to L1 state on the Intel® X58 Express Chipset Platform                                                                                                                                       |  |

### **Specification Changes**

| Number | SPECIFICATION CHANGES                                                           |  |  |  |  |

|--------|---------------------------------------------------------------------------------|--|--|--|--|

|        | There are no specification changes in this revision of the specification update |  |  |  |  |

### **Specification Clarifications**

| No. | SPECIFICATION CLARIFICATIONS                        |  |  |  |

|-----|-----------------------------------------------------|--|--|--|

| 1   | Non-Posted Peer-to-Peer Support between IOH and ICH |  |  |  |

### **Documentation Changes**

| No. | DOCUMENTATION CHANGES                                 |  |

|-----|-------------------------------------------------------|--|

| 1   | Table 7-4 Correction: Inbound Memory Address Decoding |  |

# **Identification Information**

### **Component Identification via Programming Interface**

The Intel X58 Express Chipset (IOH) stepping can be identified by the following register contents:

| Stepping | Features | Vendor ID | Device ID | Revision<br>Number | Notes |

|----------|----------|-----------|-----------|--------------------|-------|

| B2       | 36S      | 8086h     | 3405h     | 12h                |       |

| B3       | 36S      | 8086h     | 3405h     | 13h                |       |

| C2       | 36S      | 8086h     | 3405h     | 22h                | 1,2   |

Note:

1. This part supports  $Intel^{\ensuremath{\mathbb{R}}}$  Trusted Execution Technology (Intel<sup> $\ensuremath{\mathbb{R}}$ </sup> TXT) 2. C2 is for UP WS Only

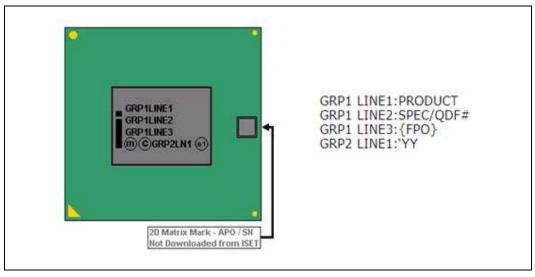

### **Component Marking Information**

The Intel $^{\ensuremath{\mathbb{R}}}$  X58 Express Chipset (IOH) production stepping can be identified by the following component markings:

| Stepping | S-Spec | Top Marking             | Notes            |

|----------|--------|-------------------------|------------------|

| B2       | SLGBT  | AC82X58                 | Production Units |

| В3       | SLGMX  | AC82X58<br>SLGMX 901076 | Production Units |

| C2       | SLH3M  | AC82X58<br>SLH3M 904727 | Production Units |

### Figure 1. Top-Side Marking Example

| 2.           | CPURST bit does not get cleared by hardware.                                                                                                                                                                                                                                                                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | SYRE: CPURST bit does not get cleared by hardware.                                                                                                                                                                                                                                                                |

|              | Background                                                                                                                                                                                                                                                                                                        |

|              | SYRE: System Reset - This register controls IOH reset behavior.                                                                                                                                                                                                                                                   |

|              | CPURESET (SYRE bit 10) - When this bit is set to "1", the IOH asserts RESETO_N. The IOH clears this bit when CPURESET timer elapses.                                                                                                                                                                              |

| Implication: | The IOH will not assert RESETO_N when CPURST is set if it has been set previously.                                                                                                                                                                                                                                |

| Workaround:  | The CPURST bit must be cleared prior to setting it.                                                                                                                                                                                                                                                               |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                    |

| 3.           | PCIe* RX LOs entry/exit issues.                                                                                                                                                                                                                                                                                   |

| Problem:     | If tx-L0s is enabled in Gen2 speed for endpoint devices directly connected to the Intel X58 Express Chipset ports, the IOH may fail to properly exit rx-L0s. Transitions to RECOVERY will occur and several types of errors including, but not limited to, receiver errors, bad TLPs and bad DLLPs may be logged. |

| Implication: | May cause unexpected correctable errors on PCIe links.                                                                                                                                                                                                                                                            |

| Workaround:  | Disable tx-L0s in endpoints directly attached to the Intel X58 Express Chipset ports.                                                                                                                                                                                                                             |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                    |

| 4.           | V <sub>TX-RCV-DETECT</sub> pulse too large during receiver detection.                                                                                                                                                                                                                                             |

| Problem:     | The VTX-RCV-DETECT pulse has been measured as high as 700 mV.                                                                                                                                                                                                                                                     |

|              | Background                                                                                                                                                                                                                                                                                                        |

|              | VTX-RCV-DETECT - The amount of voltage change allowed during Receiver Detection.<br>The maximum is 600 mV for both 2.5 GT/s and 5 GT/s.                                                                                                                                                                           |

| Implication: | This may overstress PCIe agents.                                                                                                                                                                                                                                                                                  |

| Workaround:  |                                                                                                                                                                                                                                                                                                                   |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                    |

| 5.           | PCIe Gen2 differential peak-to-peak transmit voltage swing is too low.                                                                                                                                                                                                                                            |

| Problem:     | The PCIe Gen2 transmit buffers are not generating a large enough peak-to-peak transmit voltage swing, thus violating the PCIe Gen2 specification.                                                                                                                                                                 |

| Implication: | The PCIe Gen2 specification is violated.                                                                                                                                                                                                                                                                          |

| Workaround:  | Fixed in B0. BIOS changes are required as part of the fix as outlined below:                                                                                                                                                                                                                                      |

|              | Dev 13: Func 3                                                                                                                                                                                                                                                                                                    |

|              | 1. Set Offset 330h [15:12] to 5, [11:8] to 3.                                                                                                                                                                                                                                                                     |

|              |                                                                                                                                                                                                                                                                                                                   |

|              | Dev 14:Func 0                                                                                                                                                                                                                                                                                                     |

|              | 1. Set Offset 330h [15:12] to 5, [11:8] to 3.                                                                                                                                                                                                                                                                     |

Dev 13: Func 0

- 1. Set Offset 1A0h [23:16] to 5, [7:0] to FFh.

- 2. Set Offset 11Ch [28:25] to n, (n = 0)

- 3. For each n setting in step 2, set Offset 1B4h [11:8] to 8, [7:4] to 6, [3:0] to 5.

Dev 13: Func 1

- 1. Set Offset 1A0h [23:16] to 5, [7:0] to FFh.

- 2. Set Offset 11Ch [28:25] to n, (n = 0, 1)

- 3. For each n setting in step 2, set Offset 1B4h [11:8] to 8, [7:4] to 6, [3:0] to 5.

### Dev 13: Func 3

- 1. Set Offset 1A0h [23:16] to 5, [7:0] to FFh.

- 2. Set Offset 11Ch [28:25] to n, (n = 0, 1, 2, 3)

- 3. For each n setting in step 2, set Offset 1B4h [11:8] to 8, [7:4] to 6, [3:0] to 5.

Dev 14: Func 0

- 1. Set Offset 1A0h [23:16] to 5, [7:0] to FFh.

- 2. Set Offset 11Ch [28:25] to n, (n = 0, 1, 2, 3)

- 3. For each n setting in step 2, set Offset 1B4h [11:8] to 8, [7:4] to 6, [3:0] to 5.

Note:The above configuration sequence needs to be repeated in the S3 state resume path.Status:For the steppings affected, see the Summary Tables of Changes.

### 6. Testlo[20] must be pulled high.

Problem:The Testlo[20] signal is inverted.Implication:If the workaround is not implemented, the IOH will not correctly function.Workaround:The Testlo[20] pin must be pulled to the VCCEPW rail via a 10K ohm ±1% resistor.Status:For the steppings affected, see the Summary Tables of Changes

### 7. Surprise down error status not being flagged.

Problem: The Surprise down error status is not being flagged during training failure or surprise removal.

Background

UNCSTS: Uncorrectable Error Status - This register identifies uncorrectable errors detected for PCI Express/DMI port.

Surprise Down Error Status (UNCSTS bit 5) - Flags the system when a training failure or surprise removal has occurred.

- Implication: The system will not be able to reliably detect if a PCIe card has not trained properly or been inadvertently removed unless the workaround is used.

- Workaround: BIOS fix

Status: For the steppings affected, see the Summary Tables of Changes.

- 8. Extended Error Detect Mask Registers of all PCI e root ports mask error logging by default.

- Problem: The mask fields of all PCIe root ports (devices 1 10) Extended PCIe Error Detect Mask Registers are set to 1 by default.

- Implication: All PCIe Advanced error status logging registers have a corresponding error detect mask register to control if error statuses will be logged. Below are the error status/ error detect mask pairs:

Uncorrectable Error Status (offset 104h) and Detect Status Mask (offset 218h).

Correctable Error Status (offset 110h) and Detect Status Mask (offset 21Ch).

Root Port Error Status (offset 130h) and Detect Status Mask (offset 220h).

XP Correctable Error Status (offset 200h) and Detect Mask (offset 228h).

XP Uncorrectable Error Status (offset 208h) and Detect Mask (offset 224h).

With the default values of these error detect mask registers, no PCIe advanced errors will be logged and reported.

- Workaround: BIOS must clear registers 218h, 21Ch, 220h, 228h, and 224h to zero in order to log and report corresponding errors.

- Status: For the steppings affected, see the Summary Tables of Changes.

### 9. Long XOR chain is broken.

- Problem: The long XOR chain used for high volume manufacturing test of the PCIe interface is not functional.

- Implication: Tests dependent on using the long XOR chain for high volume manufacturing test will not function

- Workaround: The individual XOR chains for each PCIe port are operable and can be used to cover those areas covered by the long XOR chain.

- Status: For the steppings affected, see the Summary Tables of Changes.

### 10. PCI e Header of a malformed TLP is not logged.

- Problem: A malformed Transaction Layer Packet (TLP) is logged in the UNCERRSTS register (Device:0-10, Function:0, Offset:0x104h) but the HDRLOG register (Header Log register, Device:0-10, Function:0, Offset 11Ch) do not log the header of the malformed TLP.

- Implication: Given that the PCIe specifies that the header of the malformed TLP must be logged, the PCIe specification is violated.

- Workaround: None

Status: For the steppings affected, see the Summary Tables of Changes.

#### 11. PCI e PMCSR Power State fields allow writing D1 and D2.

- Problem: The PMCSR (Devices: 0 to 10, Function: 0, Offset: E4h) bits 1:0 allow states D1 and D2 to be written.

- Implication: Given that the IOH does not support the D1 and D2 states, the IOH should not allow these values to be written. The IOH does not changes power state from D0 or D3hot when PMCSR bits 1:0 are written to D1 or D2, so there is no functional impact to the IOH when these states are written.

- Workaround: Do not write states D1 and D2 to the PMCSR bits 1:0.

- Status: For the steppings affected, see the Summary Tables of Changes.

- 12. DEVCON2[3:0] and CTOCTRL not accurately set the completion timeout value.

- Problem: The DEVCON2 (device: 0-10, function: 0, offset: B8h) bits 3:0 in conjunction with CTOCTRL (device: 0-10, function: 0, offset: 1E0h) bits 9:8 does not accurately set the completion timeout value.

- Implication: The duration of the PCIe timeout will differ from that programmed.

- Workaround: See the documentation change for 3319486.

- Status: For the steppings affected, see the Summary Tables of Changes.

- 13. In Intel® QuickPath Interconnect L1 Power management mode, Link layer sends retryable flits after L1.Ack.

- Problem: The Intel X58 Express Chipset Intel QuickPath Interconnect Link layer is sending packets during the window between the Intel X58 Express Chipset sending L1.Ack and the time it receives Inband Reset from Nehalem processor.

- Implication: This causes a system hang as these packets after L1.Ack will be dropped by Nahalem processor. As per Intel QuickPath Interconnect Spec, Link layer should not send any packets after L1.Ack.

- Workaround: Workaround is implemented in the Intel QuickPath Interconnect Initialization Reference Code (Intel QuickPath Interconnect RC) v0.75 and later. When BIOS enables Intel QuickPath Interconnect L1, it must also set the Intel QuickPath Interconnect RC L1\_workaround input parameter to invoke the workaround. Below is an example of adding this input parameter to the csiSetup.c file in the Intel QuickPath Interconnect RC.

- Status: For the steppings affected, see the Summary Tables of Changes.

### 14. PCIe Gen2 Tx Return loss fails spec

- Problem: The the differential and common mode transmit return loss fail to meet the PCIe Gen2 specification.

- Implication: Some Gen2 PCIe agents may have increased inter-symbol interference, ISI, due to signal reflection at the driver of Intel X58 Express Chipset. Gen1 return loss will meet specifications.

- Workaround: Following Intel X58 Express Chipset PDG PCIe Gen2 guidelines will result in no Gen2 performance or functional issues.

- Status: For the steppings affected, see the Summary Tables of Changes.

#### 15. Persistent Jtag error reported at MIERRST register

- Problem: The MIERRST register (Device: 20, Function: 2, Offset: 380h) bit 2 continuously gets set if the MIERRCTL register (Device: 20, Function: 2, Offset: 384h) bit 2 is set regardless of whether an error truly exists on the JTAG interface or not. Further, the MIERRCNT register (Device: 20, Function: 2, Offset 3C0h) will indicate an overflow via bit 7 as errors are continuously registered.

- Implication: The MIERRST and MIERRCNT registers are not dependable sources of information if the IOH is configured to record errors related to the JTAG interface.

- Workaround: None.

- Status: For the steppings affected, see the Summary Tables of Changes.

#### 16. Interop issue of some PCIe Gen1 cards with Gen2 Devices

- *Note:* Note: this is not a Intel X58 Express Chipset issue, and the workaround documented below is to resolve the interoperability issue certain PCIe Gen1 cards have with Gen2 capable Intel X58 Express Chipset PCIe root ports.

- Problem: During PCIe physical layer link initialization, Intel X58 Express Chipset Gen2 capable PCIe root ports will advertise 2.0 Specification defined capabilities such as 5.0 GT/s data rate support and link upconfigure in the Training Sequence (TS) Ordered Sets. Some downstream pre-2.0 PCIe Gen1 cards may have trouble dealing with these Gen1 reserved fields that are not reserved for PCIe Gen2.

- Implication: These PCIe Gen1 cards may fail to properly train with Intel X58 Express Chipset.

- Workaround: Below is the standard method to force Intel X58 Express Chipset PCIe root ports to Gen1 operation:

- 1. Set LNKCON2 (Dev 1-10: Func 0: Offset C0h) bits [3:0] to 0001b.

- 2. Clear LNKCON2 (Dev 1-10: Func 0: Offset C0h) bits [6] to 0b

- 3. Set LNKCON (Dev 1-10: Func 0: Offset A0h) bit [5] to 1b to retrain the link.

If some PCIe Gen1 cards fail to train with the standard method, BIOS should program the following registers to prevent Intel X58 Express Chipset PCIe root ports from advertising 2.0 Specification defined capabilities. There is one register control field for each Intel X58 Express Chipset PCIe root port.

Dev 13: Funcs 6 - 1: Offset 4B4h bit[23] for root ports 6 - 1.

Dev 14: Funcs 3 - 0: Offset 4B4h bit[23] for root ports 10 - 7.

Clear this bit to disable the corresponding root port from advertising upconfigure capability before doing Step 3 above.

Status: For the steppings affected, see the Summary Tables of Changes.

### 17. PCI e ASPM L1 tests reporting lost credits.

- Problem: The internal counter for flow control (FC) credit tracking is 8 bits wide. If the link is in a state where it cannot modify FC credits, but receives greater than 256 posted data credits to be updated, the credits can be lost. The most likely case for this to occur is when the link is in an ASPM L1 state.

- Implication: Performance is impacted due to loss of credits.

Workaround: None.

Status: For the steppings affected, see the Summary Tables of Changes.

## 18. Intel QuickPath Interconnect fails to retrain to L0 slow mode after 32 in-band resets.

- Problem: After 32 Intel QuickPath Interconnect inband resets from the CPU to an IOH port are executed when in slow mode the next inband reset will fail as the Intel QuickPath Interconnect will not retrain to L0 slow mode.

- Implication: The Intel QuickPath Interconnect link will fail when operating in slow mode after 32 Intel QuickPath Interconnect inband resets.

- Workaround: BIT 5 of device 13, functions 1-0, offset B4Ch must be set every time before an inband reset from the CPU to an IOH port.

- Status: For the steppings affected, see the Summary Tables of Changes.

- 19. ATS address field in the translation completion retuned in reversed byte order.

- Problem: A PCIe Translation Request returns a completion with the address, but the address is returned from LSB to MSB, when it should be returned MSB to LSB.

- Implication: The PCIe Address Translation Specification, version 1.0 is violated.

Workaround: None

Status: For the steppings affected, see the Summary Tables of Changes.

### 20. SLTCON bit 11 returning wrong value when read

- Problem: SLTCON (Device:1-10, Function:0, Offset:A8h) register bit 11 should always return zero when read even if this bit is written with one; however, the bit is not reloaded with 0 when a 1 is written.

- Implication: The bit 11 will not correctly reflect a value of 0 when read, but the functionality of the bit is not affected due to this. The EMIL is correctly pulses when bit 11 is written with a 1.

- Workaround: No work around required. But to reflect the correct value, write SLTCON register bit 11 with zero after writing 1 to it.

- Status: For the steppings affected, see the Summary Tables of Changes.

### 21. Boot-dependent Intel QuickPath Interconnect CRC errors

- Problem: Intel QuickPath Interconnect CRC errors may be observed as a function of bootdependent (probabilistic) phase alignment of internal clock domains

- Implication: Intel QuickPath Interconnect port may fail to train or may train with sustained non-zero CRC error rate

- Workaround: If CRC's are not user-tolerable, power cycle system.

- Status: For the steppings affected, see the Summary Tables of Changes.

### 22. PCI e Inbound Msg that should be ignored is treated as Unsupported Request.

- Problem: PCIe Inbound Messages with Message Codes between 0x40 and 0x48 (with the exception for x42 and 0x46) cause the root port to log errors as Unsupported Request when it should have ignored and discarded them.

- Implication: Unsupported Request Error will be logged under the circumstances outlined above. End Point devices are strongly encouraged by PCIe spec 2.0 not to send those messages.

Workaround: None

Status: For the steppings affected, see the Summary Tables of Changes.

### 23. Memory writes to a certain address range are considered advisory non-fatal.

Problem: Accesses above address range 2^51 (TOCM) are required to be Master Aborted

and error is to be logged in UNCERRSTS (Device:0-10, Function:0, Offset:104h). The accesses are aborted and logged; however, when severity of master-abort (UR) is set to non-fatal, memory write accesses are not to be considered advisory non-fatal, rather, they should be considered normal non-fatal. There is a range of address from 2^51 to 2^52-1 (0x8\_0000\_0000\_0000 to 0xF\_FFFF\_FFF\_FFFF) for which memory write accesses are logged as advisory non-fatal. In this case, CORERRSTS (Device:0-10, Function:0, Offset:110h) bit 13 is set. Note that this issue does not arise if UR severity is set to Fatal.

Implication: The status of transactions occurring as described above will not be correctly reflected.

Workaround: None

Status: For the steppings affected, see the Summary Tables of Changes.

#### 24. Inbound Write fetches may not make forward progress

- Problem: Stress traffic causes Outstanding Request Buffer (ORB) to fill up creating a corner condition where Inbound Write fetches that are supposed to make forward progress do not.

- Implication: This creates a deadlock situation since CPU is unable to respond to an IOH initiated StopReq (Lock Request) because it waiting on pending WB to complete which IOH cannot because it's unable to make forward progress

- Workaround: Reference the BIOS Update Specification.

Status: For the steppings affected, see the Summary Tables of Changes.

#### 25. PCIe lane-to-lane performance variation

- Problem: The lane-to-lane performance is inconsistent on the PCIe interface. Some lanes source/ sink more current than others leading to analog variations.

- Implication: Current compensation is compromised insomuch as not all of the lanes can be counted on to perform consistently. Optimizing the current compensation for one lane will not lead to optimized analog behavior in a neighboring lane. Ultimately, the overall analog behavior is limited by the lowest performing lane, thus overall channel analog behavior is compromised.

Workaround: Under Investigation.

Status: For the steppings affected, see the Summary Tables of Changes.

| 26.          | Transactions to addresses above TOCM are not setting the Master<br>Abort                                                                                                                                                                                         |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Problem:     | Inbound Transactions to addresses above TOCM are master aborted, but TBG does not set the C4 bit in the IOHERRST (Device: 20, Function: 2, Offset: 300h) register.                                                                                               |  |

| Implication: | Such cases of master aborts will not have status recorded. When Intel VT is enabled there is no workaround.                                                                                                                                                      |  |

| Workaround:  | When Intel VT is disabled, program the HPA_LIMT to the maximum value.                                                                                                                                                                                            |  |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                   |  |

| 27.          | SERR_EN ignored during unsupported request error escalation                                                                                                                                                                                                      |  |

| Problem:     | If DEVCON (Device: 0-10, Function: 0, Offset: 98h) Unsupported Request Reporting Enable bit (bit 3) is clear and PCICMD (Device: 0-10, Function: 0, Offset: 04h) SERR Enable bit (bit 8) is set then the unsupported request should be escalated.                |  |

| Implication: | If the DEVCON (Device: 0-10, Function: 0, Offset: 98h) Unsupported Request Reporting Enable bit (bit 3) is clear, then the unsupported request will not be escalated.                                                                                            |  |

| Workaround:  | Set DEVCON (Device: 0-10, Function: 0, Offset: 98h) Unsupported Request Reporting Enable bit (bit 3) and unsupported request will be escalated.                                                                                                                  |  |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                   |  |

| 28.          | Setting bits 24 and 25 of the MISCCTRLSTS does not result in expected behavior                                                                                                                                                                                   |  |

| Problem:     | Setting the bits 24 and 25 in the MISCCTRLSTS (Device: 0-10; Function: 0, Offset: 188h) register does not result in the peer-to-peer memory read/write transactions being disabled as expected.                                                                  |  |

| Implication: | Memory read/write transactions may still go through to the memory and the expected Completor Abort message may not be received.                                                                                                                                  |  |

| Workaround:  | None                                                                                                                                                                                                                                                             |  |

| Status:      | For the steppings affected, see the Summary Tables of Change.                                                                                                                                                                                                    |  |

| 29.          | Timeout values much larger than specified                                                                                                                                                                                                                        |  |

| Problem:     | When using the bits 51:48 of the CSIPCTRL register (Device: 16, Function: 1, Offset 0x4C) to set the configuration retry timeout values, it has been observed that the actual timeout values may be much longer than what is specified for each of the settings. |  |

| Implication: | The expected timeout signal for transactions exceeding the timelimit may not be observed.                                                                                                                                                                        |  |

| Workaround:  | None                                                                                                                                                                                                                                                             |  |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                   |  |

| 30.          | XPGLBERRPTR not accurately indicating first error in XPGLBERRSTS                                                                                                                                                                                                 |  |

| Problem:     | The XPGLBERRPTR register may not accurately point to which of the errors indicated by the by XPGLBERRSTS register occurred first.                                                                                                                                |  |

| Implication: | Due to this issue it may not be possible to detect which error occurred first in XPGLBERRSTS register when more than one bit is set in the XPGLBERRSTS register.                                                                                                 |  |

| Workaround:  | None                                                                                                                                                                                                                                                             |  |

| Status:      | For the steppings affected, see the Summary Tables of Changes                                                                                                                                                                                                    |  |

| 31.          | Failure during operation at PCI Express* L1 power management state                                                                                                                                                                                               |  |

| Problem:     | There may be intermittent failures observed when exiting from the L1 power management state back to the L0 power management state.                                                                                                                               |  |

| Implication: | Due to this issue, successful transition from the L1 state back to the L0 state may not be achieved.                                                                                                                                                                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Workaround:  | Set the bit 26 in the following registers: Device 14, Function 3-0, offset 390h and Device 13, Function 6-0, Offset 390h to 1. Also set bit 15 in the following registers: Device 14, Function 0, Offset 31Ch and Device 13, Function 3, Offset 31Ch to a 0.                                                                               |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                             |

| 32.          | Bandwidth very low for write traffic with noSnoop attribute set.                                                                                                                                                                                                                                                                           |

| Problem:     | 100% upstream posted write traffic (PCIe to memory) with the noSnoop attribute set is achieving lower than expected bandwidth. In comparison, the same test with snooped traffic achieves much higher bandwidths.                                                                                                                          |

| Implication: | Affected systems will achieve lower than expected performance.                                                                                                                                                                                                                                                                             |

| Workaround:  | The PERFCTRLSTS (Device:1-10, Function:0, Offset:180h) register, bits 3 and 2 should be set to 0.                                                                                                                                                                                                                                          |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                             |

| 33.          | Intel QuickPath Interconnect Queue/Table overflow or underflow error observed.                                                                                                                                                                                                                                                             |

| Problem:     | Intel QuickPath Interconnect Queue/Table overflow or underflow error status (Dev 20: Func 2: Offset 84h.[27:26]) is observed.                                                                                                                                                                                                              |

| Implication: | This spurious error status will cause false error reporting if enabled.                                                                                                                                                                                                                                                                    |

| Workaround:  | BIOS should program the following Intel X58 Express Chipset registers to mask off the spurious sub-state status and allow the Intel QuickPath Interconnect Queue/Table overflow or underflow error status to function. Set Dev 13:Func 0/1: Offset F90h (Dword) bit 14 to 1.                                                               |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                             |

| 34.          | IOH Course Grained Clock Gating requires an ITP.                                                                                                                                                                                                                                                                                           |

| Problem:     | Course Grained Clock Gating will only function if an ITP is connected to the IOH.                                                                                                                                                                                                                                                          |

| Implication: | Any testing involving Course Grained Clock Gating will require an ITP.                                                                                                                                                                                                                                                                     |

| Workaround:  | An ITP must be installed in the system on both the IOH and CPU with the ITP software running.                                                                                                                                                                                                                                              |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                             |

| 35.          | Some Gen2 endpoints will not complete the training in Gen2 mode.                                                                                                                                                                                                                                                                           |

| Problem:     | Some Gen2 endpoints will not complete training as expected when operating in Gen2 mode.                                                                                                                                                                                                                                                    |

|              | Note: Related to 3319126.                                                                                                                                                                                                                                                                                                                  |

| Implication: | Affected Gen2 endpoints will be unusable when operating in Gen2 mode without the workaround.                                                                                                                                                                                                                                               |

| Workaround:  | Please refer to the Intel X58 Express Chipset BIOS Sightings Update                                                                                                                                                                                                                                                                        |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                                             |

| 36.          | Setting bit 10 of PCICMD register having effect on legacy interrupts.                                                                                                                                                                                                                                                                      |

| Problem:     | PCICMD register Interrupt disable bit (bit 10) controls the generation of root port interrupts for internal events. If this bit is set to one, INTx status (bit 3) in PCISTS register PCISTS is cleared. This is incorrect as the INTx status (bit 3) should not be affected when the interrupt disable bit in the PCICMD register is set. |

| Implication: | When bit 10 of the PCICMD register is set, INTX status in PCISTS becomes zero. This is incorrect behavior.                                                                                                                                                                                                                                 |

| Workaround:  | None                                                                                                                                                                                                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                      |

| 37.          | ACS Violation is not treated as Advisory when severity is set to Non-<br>Fatal.                                                                                                                                                                                                                                     |

| Problem:     | If the severity of an Access Control Services (ACS) Violation is defined as non-fatal and the completer sends a completion with CA completion status then this case must be handled as an Advisory Non-Fatal Error as described in the PCI Express Spec.                                                            |

| Implication: | The ACS violations are treated as Non-Fatal errors instead of Advisory Non-Fatal errors.                                                                                                                                                                                                                            |

| Workaround:  | None                                                                                                                                                                                                                                                                                                                |

| Status:      | For the steppings affected, see the Summary Tables of Changes.                                                                                                                                                                                                                                                      |

| 38.          | MIERRCNT does not properly count persistent SMBus retry failures and MINNERRST doesn't log the errors.                                                                                                                                                                                                              |