# Intel<sup>®</sup> 5100 Memory Controller Hub Chipset

**Specification Update**

*April 2010* Revision 010US

**Notice:** The Intel<sup>®</sup> 5100 Memory Controller Hub Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Order Number: 318385-010US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's Web Site.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor\_number for details.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, IntelDX2, IntelDX4, IntelSX2, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Iogo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viv, Intel VPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium Inside, skool, Sound Mark, The Journey Inside, Viv Inside, VPro Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007-2010, Intel Corporation. All rights reserved.

### Contents

| Revision History                                 | 4  |

|--------------------------------------------------|----|

| Introduction                                     | 5  |

| Summary Tables of Current Product Issue Activity | 7  |

| General Product Information                      | 12 |

| Errata                                           |    |

| Specification Changes                            |    |

| Specification Clarifications                     | 30 |

| Document-Only Changes                            |    |

T

### **Revision History**

| Date           | Revision | Description                                                                                                                                                                                                            |

|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2010     | 010      | Added formerly reserved bits; updated Document-Only Changes.                                                                                                                                                           |

| February 2010  | 009      | Added Memory Address Translation Tables (Table 10 and Table 11).                                                                                                                                                       |

| August 2009    | 008      | Adde Erratum 46                                                                                                                                                                                                        |

| August 2009    | 007      | Add Erratum 45<br>Added Document titles to Table 9                                                                                                                                                                     |

| July 2008      | 006      | Clarified workaround information in Erratum 41 and problem statement in Erratum 6                                                                                                                                      |

| May 2008       | 005      | Added Erratum 44                                                                                                                                                                                                       |

| April 2008     | 004      | Added Erratum 43                                                                                                                                                                                                       |

| March 2008     | 003      | Clarified that Erratum 42 has no workaround                                                                                                                                                                            |

| January 2008   | 002      | Updated content for B0 silicon and DMA engine errata<br>Added Errata 35 through 42<br>Updated workarounds for Errata 28 and 29<br>Updated General Product Information<br>Added B0 stepping column to Table 5, "Errata" |

| September 2007 | 001      | Initial release                                                                                                                                                                                                        |

### Introduction

### Purpose/Scope/Audience

This document is an update to the specifications listed in the Parent Documents/ Related Documents table that follows. This document is a compilation of Errata, Specification Changes, Specification Clarifications, and Document-Only Changes. It is intended for hardware and software system designers and manufacturers as well as developers of applications, operating systems, or tools.

Information types defined in Conventions and Terminology are consolidated into the Specification Update and are no longer published in other documents.

This document may also contain information that was not previously published.

Table 1.

Parent Documents/Related Documents

| Title                                                                                                                                                                                                                                | Number                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Intel <sup>®</sup> 5100 Memory Controller Hub Chipset (embedded) – External Design Specification (EDS) Addendum                                                                                                                      | Note 1                         |

| Intel <sup>®</sup> 5100 Memory Controller Hub Chipset B0 Stepping (embedded) – Boundary Scan Description Language (BSDL) File                                                                                                        | Note 1                         |

| Intel <sup>®</sup> 5100 Memory Controller Hub Chipset Datasheet                                                                                                                                                                      | http://www.intel.com/ (318378) |

| Intel <sup>®</sup> 5100 Memory Controller Hub Chipset for Communications,<br>Embedded, and Storage Applications Thermal/Mechanical Design Guide                                                                                      | http://www.intel.com/ (318676) |

| Intel <sup>®</sup> Core <sup>™</sup> 2 Duo Processors T9400 and SL9400 and Intel <sup>®</sup> 5100<br>Memory Controller Hub Chipset for Communications and Embedded<br>Applications – Platform Design Guide                          | Note 1                         |

| Quad-Core and Dual-Core Intel <sup>®</sup> Xeon <sup>®</sup> Processor 5000 Sequence with<br>Intel <sup>®</sup> 5100 Memory Controller Hub Chipset for Communications,<br>Embedded, and Storage Applications – Platform Design Guide | Note 1                         |

| RS - Intel $^{\textcircled{B}}$ 5100 Memory Controller Hub Chipset BIOS Specification                                                                                                                                                | Note 1                         |

| Notes:                                                                                                                                                                                                                               | ·                              |

#### Notes:

1. Contact your Intel sales representative. Some documents may not be available at this time.

### **Conventions and Terminology**

*Note:* Errata remain in the Specification Update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the Specification Update are archived and available upon request. Specification Changes, Specification Clarifications and Document-Only Changes are removed from the Specification Update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

### Table 2. Conventions and Terminology

| Term                                        | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Document-<br>Only<br>Changes                | Document-Only Changes are changes to an Intel Parent Specification that result in changes only to an Intel customer document but no changes to a specification or to a parameter for an Intel product. An example of a document-only change is the correction of a typographical error.                                                                                                                                                                                                                                                                                                       |

| Errata<br>(plural)<br>Erratum<br>(singular) | Errata are design defects or errors. These may cause the Intel <sup>®</sup> 5100 Memory Controller Hub Chipset's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.                                                                                                                                                                                                                                                                    |

| Parent<br>Specification                     | A parent specification is a top-level specification from which other documents can be derived,<br>depending on the product or platform. Typically, a parent specification includes a product's<br>pinout, architectural overview, device operation, hardware interface, or electrical<br>specifications.<br>Examples of parent specifications include the following: Datasheet, External Design<br>Specification (EDS), Developer's Manual, Technical Product Specification.<br>The derived documents may be used for purposes other than that for which the parent<br>specification is used. |

| Specification<br>Changes                    | Specification Changes are the result of adding, removing, or changing a feature, after which an Intel product subsequently operates differently than specified in an Intel Parent Specification, but typically the customer does not have to do anything to achieve proper device functionality as a result of Intel adding, removing, or changing a feature.                                                                                                                                                                                                                                 |

| Specification<br>Clarifications             | Specification Clarifications are changes to a document that arise when an Intel Parent<br>Specification must be reworded so that the specification is either more clear or not in conflict<br>with another specification.                                                                                                                                                                                                                                                                                                                                                                     |

### Summary Tables of Current Product Issue Activity

Table 5 through Table 8 indicate the Errata, Specification Changes, Specification Clarifications, and Document-Only Changes that apply to the Intel<sup>®</sup> 5100 Memory Controller Hub Chipset product. Intel may fix some of the Errata in a future stepping of the component as noted in Table 3 or account for the other outstanding issues through Specification Changes, Specification Clarifications, or Document-Only Changes. Table 5 through Table 8 use the codes listed in Table 3.

#### Code Column Definition Indicates either that, for the stepping/revision listed, Х • an erratum eXists and is not yet fixed Stepping • a specification change or specification clarification applies Indicates either that, for the stepping/revision listed, No mark or blank Stepping an erratum is fixed a specification change or specification clarification does not apply Plan Fix Status This erratum may be fixed in a future stepping/revision. Fixed Status This erratum has been previously fixed. No Fix Status There are no plans to fix this erratum. A change bar to the left of a table row indicates an item that is either new or modified from the previous version of the Specification Update document.

#### Table 3.Codes Used in Summary Tables

The errata inherited from the Intel<sup>®</sup> 5000 Series Chipset include Errata 1 through 27, 35, 36, 38 through 40, and 43. The cross-references between the Errata are shown in Table 4, "Intel<sup>®</sup> 5100 Memory Controller Hub Chipset to Intel<sup>®</sup> 5000 Series Chipset Errata Cross-reference".

## Table 4.Intel<sup>®</sup> 5100 Memory Controller Hub Chipset to Intel<sup>®</sup> 5000 Series Chipset<br/>Errata Cross-reference (Sheet 1 of 3)

| Intel <sup>®</sup> 5100<br>Memory Controller<br>Hub Chipset<br>Erratum Number | Intel <sup>®</sup> 5000<br>Series Chipset<br>Erratum<br>Number <sup>1</sup> | Errata Title                                                                                                                                        |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                             | 1                                                                           | PCI Express* auto link negotiation occasionally fails to correctly detect link width                                                                |

| 2                                                                             | 2                                                                           | MCH B1Err errors logged incorrectly                                                                                                                 |

| 3                                                                             | 3                                                                           | PCI Express* IBIST on x8/x16 port will not stop testing of entire port if an error is detected on any lane other than lowest four lanes of the port |

| 4                                                                             | 6                                                                           | PCI Express* receiver error logged upon putting link in disable state                                                                               |

| 5                                                                             | 7                                                                           | PCI Hot Plug* ABP Bit Set While Attention Button is Pressed                                                                                         |

Notes:

Erratum, Compliance Issue, and Documentation Change reference numbers are based on the Intel(R) 5000 Series Chipset Memory Controller Hub (MCH) Specification Update NDA, July 2007.

2. N/A = Not Available

# Table 4.Intel<sup>®</sup> 5100 Memory Controller Hub Chipset to Intel<sup>®</sup> 5000 Series Chipset<br/>Errata Cross-reference (Sheet 2 of 3)

| Intel <sup>®</sup> 5100<br>Memory Controller<br>Hub Chipset<br>Erratum Number | Intel <sup>®</sup> 5000<br>Series Chipset<br>Erratum<br>Number <sup>1</sup> | Errata Title                                                                                                                                  |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 6                                                                             | 8                                                                           | Leakage from 1.5 V VCC to MCH VTT                                                                                                             |

| 7                                                                             | 9                                                                           | Surprise Link Down Error Reported When PCI Express* Slot Power is<br>Removed During Hot-plug Event                                            |

| 8                                                                             | 10                                                                          | System hang with large number of transaction retries                                                                                          |

| 9                                                                             | 11                                                                          | INTL[7:2] registers are not implemented as read/write                                                                                         |

| 10                                                                            | 13                                                                          | SMI escalation via ERR[2:0]# pins may result in IERR#                                                                                         |

| 11                                                                            | 15                                                                          | CPU may record signal glitches when MCH is being reset                                                                                        |

| 12                                                                            | 16                                                                          | Coalesce mode cannot be used with maximum payload size of 256 B                                                                               |

| 13                                                                            | 22                                                                          | MCH may log F2Err during shutdown special cycle initiated due to FSB timeout                                                                  |

| 14                                                                            | 25                                                                          | Header of malformed TLPs on a x16 port not always logged                                                                                      |

| 15                                                                            | 27                                                                          | RID=CRID is sticky across warm reset                                                                                                          |

| 16                                                                            | 28                                                                          | SLD could cause spurious completions                                                                                                          |

| 17                                                                            | 29                                                                          | IBIST does not capture failed lanes properly                                                                                                  |

| 18                                                                            | 30                                                                          | IBIST RX logic does not stop when IBISTR is reset                                                                                             |

| 19                                                                            | 33                                                                          | SLD on PCI Express* port during peer-to-peer posted requests can causes ESI to hang                                                           |

| 20 34                                                                         |                                                                             | PEXGCTRL.PME_TO_ACK may not be set when a turn off<br>acknowledge TLP has been received from all ports                                        |

| 21 35                                                                         |                                                                             | Masked completer abort status errors may be reported in the UNCERRSTS[0] register                                                             |

| 22 36                                                                         |                                                                             | SMBus TLOW: SEXT specification may be exceeded on SMBus 0 when the north bridge is clocked with a 266 MHz BUSCLK                              |

| 23                                                                            | 37                                                                          | First uncorrectable fatal bit of the root error status register may be<br>incorrectly set when a second uncorrectable fatal error is received |

| 24                                                                            | 38                                                                          | Bit [3], INTxST, of the PEXSTS register may be cleared when bit [10], INTxDisable, of the PEXCMD register is set                              |

| 25                                                                            | N/A <sup>2</sup>                                                            | Valid formatted TLP with invalid type may hang system                                                                                         |

| 26                                                                            | Compliance<br>Issue #1                                                      | PCI Express* Compliance Test Failure: CBDMA Interrupt Line Register                                                                           |

| 27                                                                            | Compliance<br>Issue #2                                                      | PCI Express* Compliance Test Failure: MSI Address Register                                                                                    |

| 35                                                                            | 41                                                                          | PCI Express* transaction I/O ordering queue overflow                                                                                          |

| 36                                                                            | Document<br>Change #2                                                       | PCI Express* device number assignment and header log                                                                                          |

| 38                                                                            | 5                                                                           | DMA engine channel completion address logged twice in<br>FERR_CHANCMP register                                                                |

| 39                                                                            | 26                                                                          | Illegal addresses within 40-bit address space in channel completion address register do not generate cmp_addr_err                             |

| 40                                                                            | 39                                                                          | DMA engine's next channel error register not updated when subsequent errors detected                                                          |

*Notes:* 1.

Erratum, Compliance Issue, and Documentation Change reference numbers are based on the Intel(R) 5000 Series Chipset Memory Controller Hub (MCH) Specification Update NDA, July 2007.

2. N/A = Not Available

### Intel<sup>®</sup> 5100 Memory Controller Hub Chipset to Intel<sup>®</sup> 5000 Series Chipset Errata Cross-reference (Sheet 3 of 3) Table 4.

| Intel <sup>®</sup> 5100<br>Memory Controller<br>Hub Chipset<br>Erratum Number | Intel <sup>®</sup> 5000<br>Series Chipset<br>Erratum<br>Number <sup>1</sup> | Errata Title                                                                                                                                                                |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43                                                                            | 43                                                                          | Read transactions may be delayed                                                                                                                                            |

| 45                                                                            | 45                                                                          | When MPS is set to 128B, Malformed TLP is not flagged for TLP packets that are exactly 256B in length.                                                                      |

| 46                                                                            | 46                                                                          | Error Source Identification (ID) is not properly reporting the<br>Requestor ID when the uncorrectable (Non-fatal/fatal) error is<br>detected in the PCI Express* Root Port. |

#### Notes:

Erratum, Compliance Issue, and Documentation Change reference numbers are based on the Intel(R) 5000 Series Chipset Memory Controller Hub (MCH) Specification Update NDA, July 2007. 1.

2. N/A = Not Available

#### Table 5. Errata (Sheet 1 of 2)

| No. | Stepp<br>Revi |    | Status | Errata Title                                                                                                                                        |

|-----|---------------|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|     | AO            | BO |        |                                                                                                                                                     |

| 1   | х             | х  | No Fix | PCI Express* auto link negotiation occasionally fails to correctly detect link width                                                                |

| 2   | Х             | Х  | No Fix | MCH B1Err errors logged incorrectly                                                                                                                 |

| 3   | х             | х  | No Fix | PCI Express* IBIST on x8/x16 port will not stop testing of entire port if an error is detected on any lane other than lowest four lanes of the port |

| 4   | Х             | Х  | No Fix | PCI Express* receiver error logged upon putting link in disable state                                                                               |

| 5   | Х             | Х  | No Fix | PCI Hot Plug* ABP Bit Set While Attention Button is Pressed                                                                                         |

| 6   | Х             | Х  | No Fix | Leakage from 1.5 V VCC to MCH VTT                                                                                                                   |

| 7   | х             | х  | No Fix | Surprise Link Down Error Reported When PCI Express* Slot Power is Removed During Hot-plug Event                                                     |

| 8   | Х             | Х  | No Fix | System hang with large number of transaction retries                                                                                                |

| 9   | Х             | Х  | No Fix | INTL[7:2] registers are not implemented as read/write                                                                                               |

| 10  | Х             | Х  | No Fix | SMI escalation via ERR[2:0]# pins may result in IERR#                                                                                               |

| 11  | Х             | Х  | No Fix | CPU may record signal glitches when MCH is being reset                                                                                              |

| 12  | Х             | Х  | No Fix | Coalesce mode cannot be used with maximum payload size of 256 B                                                                                     |

| 13  | Х             | Х  | No Fix | MCH may log F2Err during shutdown special cycle initiated due to FSB timeout                                                                        |

| 14  | Х             | Х  | No Fix | Header of malformed TLPs on a x16 port not always logged                                                                                            |

| 15  | Х             | Х  | No Fix | RID=CRID is sticky across warm reset                                                                                                                |

| 16  | Х             | Х  | No Fix | SLD could cause spurious completions                                                                                                                |

| 17  | Х             | Х  | No Fix | IBIST does not capture failed lanes properly                                                                                                        |

| 18  | Х             | Х  | No Fix | IBIST RX logic does not stop when IBISTR is reset                                                                                                   |

| 19  | х             | х  | No Fix | SLD on PCI Express* port during peer-to-peer posted requests can causes ESI to hang                                                                 |

| 20  | х             | х  | No Fix | PEXGCTRL.PME_TO_ACK may not be set when a turn off acknowledge TLP has been received from all ports                                                 |

| 21  | х             | х  | No Fix | Masked completer abort status errors may be reported in the UNCERRSTS[0] register                                                                   |

### Table 5.Errata (Sheet 2 of 2)

|    |    | ping/<br>ision Status | Errata Title |                                                                                                                                                                       |

|----|----|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | AO | BO                    |              |                                                                                                                                                                       |

| 22 | х  | х                     | No Fix       | SMBus TLOW: SEXT specification may be exceeded on SMBus 0 when the north bridge is clocked with a 266 MHz BUSCLK                                                      |

| 23 | х  | х                     | No Fix       | First uncorrectable fatal bit of the root error status register may be incorrectly set when a second uncorrectable fatal error is received                            |

| 24 | х  | х                     | No Fix       | Bit [3], INTxST, of the PEXSTS register may be cleared when bit [10],<br>INTxDisable, of the PEXCMD register is set                                                   |

| 25 | Х  | Х                     | No Fix       | Valid formatted TLP with invalid type may hang system                                                                                                                 |

| 26 | Х  | Х                     | No Fix       | PCI Express* Compliance Test Failure: CBDMA Interrupt Line Register                                                                                                   |

| 27 | Х  | Х                     | No Fix       | PCI Express* Compliance Test Failure: MSI Address Register                                                                                                            |

| 28 | Х  |                       | Fixed        | Unpopulated ranks may cause performance degradation                                                                                                                   |

| 29 | х  | х                     | No Fix       | Flushing of writes in Coherency Engine (CE) for Asynchronous Self-refresh mode entry                                                                                  |

| 30 | Х  | Х                     | No Fix       | CKE does not go low during Asynchronous Self-refresh mode                                                                                                             |

| 31 | х  |                       | Fixed        | Write commands stuck in WR Queue preventing S3 entry in Asynchronous Self-refresh mode                                                                                |

| 32 | Х  |                       | Fixed        | System failures while running memory sparing and patrol scrub                                                                                                         |

| 33 | Х  |                       | Fixed        | Asynchronous Self-refresh relative to Reset deassertion                                                                                                               |

| 34 | х  | х                     | No Fix       | Ports may be starved when both FSB buses are heavily loaded while PCI Express* agents are generating address conflicts                                                |

| 35 | Х  | Х                     | No Fix       | PCI Express* transaction I/O ordering queue overflow                                                                                                                  |

| 36 | Х  | Х                     | No Fix       | PCI Express* device number assignment and header log                                                                                                                  |

| 37 |    | х                     | No Fix       | Incorrect register default for proper DDR boundary scan board manufacturing testing                                                                                   |

| 38 | х  | х                     | No Fix       | DMA engine channel completion address logged twice in FERR_CHANCMP register                                                                                           |

| 39 | Х  | х                     | No Fix       | Illegal addresses within 40-bit address space in channel completion address register do not generate cmp_addr_err                                                     |

| 40 | Х  | х                     | No Fix       | DMA engine's next channel error register not updated when subsequent errors detected                                                                                  |

| 41 |    | Х                     | No Fix       | Incorrect CKE behavior during recovery from S3 suspend                                                                                                                |

| 42 | х  | х                     | No Fix       | Machine check error due to a rare livelock condition when only two logical processors are enabled                                                                     |

| 43 | Х  | Х                     | No Fix       | Read transactions may be delayed                                                                                                                                      |

| 44 | х  | х                     | No Fix       | Disabling of Front Side Bus (FSB) parity impacts some data poisoning capabilities                                                                                     |

| 45 | х  | х                     | No Fix       | When MPS is set to 128B, Malformed TLP is not flagged for TLP packets that are exactly 256B in length.                                                                |

| 46 | х  | х                     | No Fix       | Error Source Identification (ID) is not properly reporting the Requestor ID when the uncorrectable (Non-fatal/fatal) error is detected in the PCI Express* Root Port. |

### Table 6.Specification Changes

| No. | Stepping/Revision | Specification Changes                               |

|-----|-------------------|-----------------------------------------------------|

| NO. | A0/B0             | Specification onanges                               |

|     |                   | None for this revision of the Specification Update. |

### Table 7. Specification Clarifications

| No. | Stepping/<br>Revision | Specification Clarifications        |

|-----|-----------------------|-------------------------------------|

|     | A0/B0                 |                                     |

| 1   | Х                     | PCI Hot Plug* Capability Validation |

### Table 8.Document-Only Changes

| No. | Document Title                                                                                                                                                                    | Rev. | Document-Only Changes                                                                                                                                                                                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-4 | Intel <sup>®</sup> 5100<br>Memory<br>Controller Hub<br>Chipset External<br>Desig<br>Specification;<br>Intel <sup>®</sup> 5100<br>Memory<br>Controller Hub<br>Chipset<br>Datasheet | 009  | Added the following formally reserved bits to the 5100 MCH EDS and<br>Datasheet:<br>PEXLNKSTS bit 13 - DLLA: Data Link Layer Active<br>PEXLNKCAP bit 20 - DLLAEN: Data Link Layer Active Reporting Capable<br>PEXLNKCAP bit 19 - SLNKDEN: Surprise Link Down Error Reporting Capable |

1

### **General Product Information**

The Intel<sup>®</sup> 5100 MCH Chipset can be identified by the following register contents:

Table 9. Identification Information

| Part Number                              | Stepping | Vendor ID <sup>1</sup> | Device I D <sup>2</sup> | Revision Number <sup>3</sup> |

|------------------------------------------|----------|------------------------|-------------------------|------------------------------|

| Contact your Intel sales representative. | B0       | 8086h                  | 65C0h                   | 90h                          |

Notes:

The Vendor ID corresponds to bits [15:0] of the VID - Vendor Identification Register located at Offset 00–01h in the PCI Function 0 configuration space.

The Device ID corresponds to bits [15:0] of the DID - Device Identification Register located at Offset

The Device ID corresponds to bits [15:0] of the DID - Device Identification Register located at Offset 02–03h in the PCI Function 0 configuration space. The Revision Number corresponds to bits [7:0] of the RID - Revision Identification Register located at

The Revision Number corresponds to bits [7:0] of the RID - Revision Identification Register located at Offset 08h in the PCI Function 0 configuration space.

The Intel<sup>®</sup> 5100 MCH Chipset stepping can be identified by the following component markings:

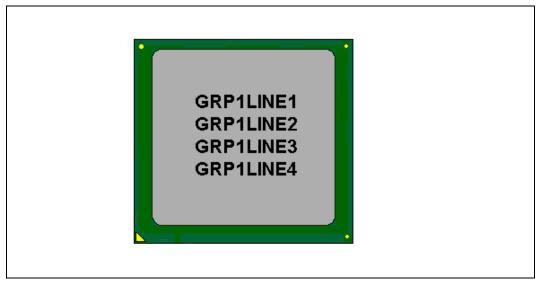

| мсн                                 | Stepping | Top Marking<br>(GRP1LINE1) | QDF-Spec<br>(GRP1LINE2)<br>or MM# | Top Marking<br>(GRP1LINE2) |

|-------------------------------------|----------|----------------------------|-----------------------------------|----------------------------|

| Intel <sup>®</sup> 5100 MCH Chipset | BO       | QG5100MCH                  | 894163                            | Production                 |

### Figure 1. Top-Side Marking Example

### **Errata**

The errata inherited from the Intel<sup>®</sup> 5000 Series Chipset include Errata 1 through 27, 35, 36, 38 through 40, and 43. The cross-references between the Errata are shown in Table 4, "Intel<sup>®</sup> 5100 Memory Controller Hub Chipset to Intel<sup>®</sup> 5000 Series Chipset Errata Cross-reference".

## 1. PCI Express\* auto link negotiation occasionally fails to correctly detect link width

- Problem: The MCH occasionally fails to correctly detect the width of a hot-plugged PCI Express\* card. This is restricted to the case where cards are "hot-plugged" with system power-on.

- Implication: The PCI Express\* auto link negotiation feature cannot be relied on to correctly detect the link width of a hot-plugged PCI Express\* card during a hot add operation.

- Workaround: Use the PEWIDTH[3:0] bits to set the width of the plugged in card. These bits are defined in the following table.

| PEWIDTH[3:0] | Port0<br>(ESI) | Port2 | Port3        | Port4                                                           | Port5 | Port6 | Port7 |  |  |  |  |

|--------------|----------------|-------|--------------|-----------------------------------------------------------------|-------|-------|-------|--|--|--|--|

| 0000         | x4             | x4    | x4           | x4                                                              | x4    | x4    | x4    |  |  |  |  |

| 0001         | x4             | x4    | x4           | x4                                                              | x4    | x     | 8     |  |  |  |  |

| 0010         | x4             | x4    | x4           | х                                                               | 8     | x4    | x4    |  |  |  |  |

| 0011         | x4             | x4    | x4           | х                                                               | 8     | х     | 8     |  |  |  |  |

| 0100         | x4             | x4    | x4           |                                                                 | x     | 16    |       |  |  |  |  |

| others       |                |       |              | Reserved                                                        |       |       |       |  |  |  |  |

| 1000         | x4             | х     | 8            | x4                                                              | x4    | x4    | x4    |  |  |  |  |

| 1001         | x4             | х     | 8            | x4                                                              | x4    | x     | 8     |  |  |  |  |

| 1010         | x4             | х     | 8            | х                                                               | 8     | x4    | x4    |  |  |  |  |

| 1011         | x4             | х     | 8            | х                                                               | 8     | x     | 8     |  |  |  |  |

| 1100         | x4             | х     | 8            |                                                                 | x     | 16    |       |  |  |  |  |

| others       |                |       |              | Reserved                                                        |       |       |       |  |  |  |  |

| 1111         | x4             |       | All port wid | x4 All port widths determined by link negotiation. <sup>1</sup> |       |       |       |  |  |  |  |

Notes:

No Fix

1. Link negotiation configuration is not recommended due to an erratum.

Status:

### 2. MCH B1Err errors logged incorrectly

Problem: B1Err logging does not operate correctly. In the event that an internal data manager parity error occurs B1Err may not be logged. In addition, B1Err may get logged if poisoned data is passed to the internal data manager from the FSB and PCI Express\* interfaces.

Implication: B1Err error reporting is unreliable.

Workaround: B1Err error logging should be disabled. The lack of B1Err error logging does not cause internal data manager errors to go undetected. An internal data manager parity error will be flagged at the destination interface.

Any parity error in the data manager will cause one of the following.

- A data parity error on the FSB if the destination is FSB

- A poisoned data pattern will be written to memory if the destination is system memory

- EP bit will be set on outbound PCI Express\* packets if the destination is one of the PCI Express\* ports.

Status: No Fix

#### 3. PCI Express\* IBIST on x8/x16 port will not stop testing of entire port if an error is detected on any lane other than lowest four lanes of the port

Problem: During PCI Express\* IBIST "stop on error" testing, if an error is detected on a x4 port, the test will stop for the entire port, and the error is logged. Likewise, if an error is detected on the lower four lanes of a x8 port, the test will stop for the entire port, and the error is logged. If an error is detected on the upper four lanes of a x8 port, the error is logged, the test stops running on the upper four lanes, but the test will continue on the lower four lanes of the port.

Likewise, if an error is detected on the lowest four lanes of a x16 port, the test will stop for the entire port, and the error is logged. If an error is detected on any of the upper 12 lanes of a x16 port, the error is logged, the test stops running on the 4-lane group that the error occurred on, but the test will continue on the other 12 lanes of the port.

- Implication: IBIST test will continue running in spite of errors if errors occur anywhere other than lowest four lanes of a x8/x16 port.

- Workaround: If "stop on error" functionality is desired, changes will have to be made to the IBIST scripts to enable this functionality by polling the global status registers. If an error occurred in only the upper lanes, halt IBIST (if in loop continuous mode) as the IBIST engine for that set of four lanes has stopped (if stop on error is enabled). If an error occurred in the lowest four lanes, all of the IBIST engines will be forced to stop (exit from Loopback). Check the loop count error status register to determine what set of four lanes failed first. One thing to note is that the upper lanes will likely record an error in all lanes whereas the lower four may or may not depending on the nature of the real error. Whether the ports are in x4, x8 or x16 mode, the DIOOIBSTAT and DIOOIBERR registers need to be checked to determine which set of four lanes had an error and which set of four lanes did not.

Status: No Fix

#### 4. PCI Express\* receiver error logged upon putting link in disable state

- Problem: When the link is told to go to Disable it is possible for the receive side to incorrectly log an error.

- Implication: Receiver error incorrectly logged.

- Workaround: To enter link disable, set the receiver error mask bit in EMASK\_COR\_PEX; then set the link disable bit. To exit link disable, clear the link disable bit; then clear the receiver error mask bit in EMASK\_COR\_PEX.

- Status: No Fix

### 5. PCI Hot Plug\* ABP Bit Set While Attention Button is Pressed

- Problem: The Attention Button Pressed (ABP) bit (bit 0) in the PEXSLOTSTS register (Device 0, 2–7, Function 0, Offset 86h) is asserted while the hot-plug attention button is pressed. Software is supposed to clear this bit after the field has been read and processed but this clear operation could happen before the button is released, causing it to be set again.

- Implication: Multiple attention button presses could be registered and processed during a single button press.

- Workaround: Hot-plug drivers in Operating Systems capable of supporting native PCI Hot Plug\* will not be supported. BIOS should use the \_OSC method to maintain control of hot-plug events thereby only allowing ACPI hot-plug support. BIOS should implement a wait of 200 ms after the interrupt is received if using attention button. If using attention jumper, implement a wait of 2200 ms. Please contact your Intel representative to get the latest revision of the *RS Intel*<sup>®</sup> *5100 Memory Controller Hub Chipset BIOS Specification* for more details on the workaround.

- Status: No Fix

### 6. Leakage from 1.5 V VCC to MCH VTT

Problem: The two *Platform Design Guides* listed in Table 1 specify that the MCH 1.5 V VCC power rail must ramp ahead of the MCH VTT power rail. During this power-up sequence, a leakage path exists within the MCH from the 1.5 V VCC pins to the VTT pins. This leakage path only exists while the MCH is powering up.

*Note:* There are various possible MCH VTT values (1.2 V, 1.1 V, or 1.05 V) depending on the platform/CPUs.)

- Implication: Higher than expected current seen on MCH VTT power rail while the 1.5 V VCC power rail is ramping. This leakage path does not impact the reliability or functionality of the MCH.

- Workaround: None

Status: No Fix

### 7. Surprise Link Down Error Reported When PCI Express\* Slot Power is Removed During Hot-plug Event

Problem: When power to a PCI Express\* slot is removed during a hot remove event, a surprise link down error is incorrectly logged.

Implication: Surprise link down error is incorrectly logged.

Workaround: Hot-plug drivers in operating systems capable of supporting native PCI Hot Plug\* will not be supported.

Perform the following.

1. When turning off the power to the slot:

- a. Set bit [5] on the EMASK\_UNCOR\_PEX register.

- b. Set bit [10] on the PEXSLOTCTRL register.

- 2. When turning *on* the power to the slot:

- a. Clear bit [5] on the EMASK\_UNCOR\_PEX register.

- b. Clear bit [10] on the PEXSLOTCTRL register.

BIOS should use the \_OSC method to maintain control of hot-plug events, thereby only allowing ACPI hot-plug support. Please contact your Intel representative to get the latest revision of the RS -  $Intel^{\ensuremath{\mathscr{B}}}$  5100 Memory Controller Hub Chipset BIOS Specification for more details on the workaround.

Status: No Fix

### 8. System hang with large number of transaction retries

- Problem: Platforms can experience a system hang. This hang is characterized by a large number of transaction retries and repeated code fetches, as well as conflicting writes to the same address. No commercially available software has been observed to cause this condition in Intel's validation environment.

- Implication: Possible system hang.

- Workaround: The Memory Reference Code (MRC) includes a BIOS workaround that resolves the known instances of this erratum.

- Status: No Fix

### 9. INTL[7:2] registers are not implemented as read/write

- Problem: The INTL[7:2] registers are implemented as Read Only (RO) when they should be implemented as Read/Write (RW) as specified in the *PCI Local Bus Specification*, Rev. 2.3.

- Implication: PCI compliance tests may report errors.

- Workaround: None

- Status: No Fix. See also Erratum 26.

### 10. SMI escalation via ERR[2:0]# pins may result in IERR#

- Problem: Any condition routed to MCH ERR[2:0]# output pins for SMI# escalation that would result in data poisoning on FSB will result in a CPU IERR# assertion due to race condition. The race condition exists between poisoned data presented to the FSB by the MCH and the uncorrectable error escalated to SMI# via ERR[2:0]# pins. If the CPU observes an SMI# assertion before the poisoned data is presented to the FSB, the CPU asserts MCERR# followed by IERR#. The CPU expects the SMI# assertion to occur at least ten BCLKs after the associated MCERR# assertion. Conditions that result in data poisoning on the FSB are uncorrectable memory ECC errors or poisoned TLPs received from any PCI Express\* port.

- Implication: CPU may assert IERR# and cause a system hang before the error may be logged in SMM.

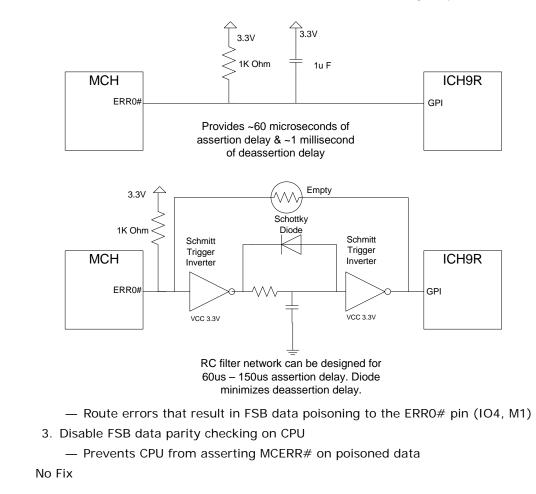

- Workaround: Any one of the three workarounds that have been identified may be selected.

- 1. Log errors upon reboot

- System components (MCH, CPU, ICH9R) preserve errors across warm resets via sticky error registers

- Requires a mechanism to reset system upon IERR# (server management controller, depress system reset button, and so forth)

- 2. Delay SMI# assertion by inserting a 60–150  $\mu s$  delay on the ERRO# pin

- Two recommended circuit solutions (other solutions may be possible):

Status:

### 11. CPU may record signal glitches when MCH is being reset

- Problem: When the MCH is reset via RESETI# the CPU may record any one or more of the following errors: address strobe glitch (MSR IA32\_MCi\_STATUS bit [23]), data strobe glitch (MSR IA32\_MCi\_STATUS bit [22]), P/N data strobes out of sync (MSR IA32\_MCi\_STATUS bit [21]), PIC and FSB data parity (MSR IA32\_MCi\_STATUS bit [19]), RSP parity (MSR IA32\_MCi\_STATUS bit [18]), or FSB address parity (MSR IA32\_MCi\_STATUS bit [16]). This can happen when the MCH asserts CPURST# just after the MCH drives an FSB transaction. This may happen because RESETI# and CPURST# maintain an asynchronous relationship with each other.

- Workaround: None

Status: No Fix

### 12. Coalesce mode cannot be used with maximum payload size of 256 B

- Problem: When maximum payload size is set to 256 B (PEXDEVCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 74h, bits [7:5] set to '001'), and read completion coalescing is enabled (PEXCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 48h, bit [10] set to '1'), the system may hang. If MPS of 256 B is used, coalescing must be disabled. If coalescing is desired, MPS must be set to 128 B.

- Implication: A system hang may occur.

- Workaround: If an MPS of 256 B is desired, use the following settings.

- 1. Set maximum payload size to 256 B (PEXDEVCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 74h, bits [7:5] set to '001')

- Disable coalescing (PEXCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 48h, bit [10] set to '0')

If coalescing is desired, use the following settings.

- 1. Enable coalescing (PEXCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 48h, bit [10] set to '1')

- 2. Set maximum payload size to 128 B (PEXDEVCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 74h, bits [7:5] set to '000')

In all cases, the following coalesce settings should be used.

- 1. Set COALESCE\_MODE to 00 (PEXCTRL[7:2,0] register, Device 0, 2–7, Function 0, Offset 48h, bits [25:24])

- Use Max\_rdcmp\_Imt\_EN default setting of 0 (PEXCTRL[7:2,0] register, Device 0, 2– 7, Function 0, Offset 48h, bit [12])

- 3. Use COALESCE\_FORCE default setting of 0 (PEXCTRL[7:2,0] register, Device 0, 2-7, Function 0, Offset 48h, bit [11])

- *Note:* Microsoft Server 2008\* forces the maximum payload size to 256 B in the PEXDEVCTRL register; therefore, the workaround with coalescing disabled must be used for Microsoft Server 2008\*.

- Status: No Fix

# 13. MCH may log F2Err during shutdown special cycle initiated due to FSB timeout

Problem: The Intel<sup>®</sup> 5100 MCH Chipset will flag a FSB F2Err when a CPU issues a Shutdown Special Cycle due to FSB timeout with the deferred response enable (DEN#) not asserted. The CPU cycle is valid per FSB protocol.

Implication: An invalid FSB F2Err error is logged.

Workaround: There are two possible workarounds.

- BIOS may disable error logging for FSB F2Err by setting bit [1] of EMASK\_FSB[1:0] registers (Device 16, Function 0, Offset 492h, 192h = 0n).

- Upon reboot error management software can check the CPU machine check registers for a FSB timeout status. If the FSB timeout status is asserted and the MCH is flagging F2Err, the F2Err assertion can be ignored.

Status: No Fix

### 14. Header of malformed TLPs on a x16 port not always logged

- Problem: The system platform may not log header information for an illegal length malformed TLP on a x16 port. This happens when the STP and END occur in the same symbol time - H H H E/IL - where H means Header DW, and E/IL is an END symbol with illegal length. Symbol time means the same clock cycle from the transaction layers point of view. For example, a x16 port will see four DWs of information in a single cycle.

- Implication: HDRLOG registers may not contain the header of malformed TLP.

Workaround: None

Status: No Fix

### 15. **RID=CRID** is sticky across warm reset

- Problem: The Revision Identification Register (RID) is keeping the value of Compatibility Revision ID (CRID) across a warm reset (RID=CRID) if RID is set to CRID prior to the warm reset. After a warm reset, RID should have the value of Stepping Revision ID (SRID) (RID=SRID).

- Implication: When RID is set to show CRID's value and a warm reset occurs, RID will not be set to show SRID's value. RID will continue to show CRID's value. After a warm reset, it is expected that RID will show SRID's value.

- Workaround: Prior to setting RID=CRID BIOS/ Software can store a copy of RID=SRID in a Sticky Scratch Pad Register, SPADS3[7:0] for example. After a warm reset BIOS/ Software can get the value of SRID from the Sticky Scratch Pad Register.

Status: No Fix

#### 16. SLD could cause spurious completions

- Problem: When a link goes down due to surprise link-down (SLD), the Intel<sup>®</sup> 5100 MCH Chipset may not drain all transaction layer packets (TLPs) before allowing the link to come back up.

- Implication: In cases, where the Intel<sup>®</sup> 5100 MCH Chipset has not fully drained all downstream completions, a downstream device coming out of reset will see spurious completions.

- Workaround: After an SLD, it is recommended that software clear the downstream device and root port of all errors.

Status: No Fix

| 17.                         | IBIST does not capture failed lanes properly                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:                    | The register that holds lane statistics is not sticky.                                                                                                                                                                                                                                                                                                                                               |

| Implication:                | This means that only those lanes that detect an error last will be remembered. For example, if lanes 1 and 2 failed in IBIST cycle N and lanes 3 and 4 failed in cycle N+M, the error status register will only reflect lanes 3 and 4 as failed and will not show lanes 1 and 2.                                                                                                                     |

| Workaround:                 | None                                                                                                                                                                                                                                                                                                                                                                                                 |

| Status:                     | No Fix                                                                                                                                                                                                                                                                                                                                                                                               |

| 18.                         | IBIST RX logic does not stop when IBISTR is reset                                                                                                                                                                                                                                                                                                                                                    |

| Problem:                    | When IBIST is started in continuous mode and the IBISTR bit is cleared, the IBIST rx logic does not stop.                                                                                                                                                                                                                                                                                            |

| Implication:                | IBIST rx logic will continue comparing whatever data shows up at the input, even after the IBISTR bit is cleared.                                                                                                                                                                                                                                                                                    |

| Workaround:                 | Clear the continuous mode bit before or along with the start bit.                                                                                                                                                                                                                                                                                                                                    |

| Status:                     | No Fix                                                                                                                                                                                                                                                                                                                                                                                               |

| 19.                         | SLD on PCI Express* port during peer-to-peer posted requests can<br>causes ESI to hang                                                                                                                                                                                                                                                                                                               |

| Problem:                    | Under specific conditions a Surprise Link-down (SLD) could cause the ESI port to hang. For this to happen, a peer-to-peer write, with the source connected to the south bridge and destination connected to the north bridge, must be in progress. If an SLD occurs on the target link during certain phases of the MCH processing the request the ESI port may hang.                                |

| Implication:                | This bug causes the ESI port to hang which will hang the system.                                                                                                                                                                                                                                                                                                                                     |

| Workaround:                 | None                                                                                                                                                                                                                                                                                                                                                                                                 |

| Status:                     | No Fix                                                                                                                                                                                                                                                                                                                                                                                               |

| 20.                         | PEXGCTRL.PME_TO_ACK may not be set when a turn off acknowledge TLP has been received from all ports                                                                                                                                                                                                                                                                                                  |

| Problem:                    | When commanded to send PME Turn Off messages by setting bit [1], PME_TURN_OFF, of the PEXGCTRL register (Device 19, Function 0, Offset 17Ch) and a PME_TO_ACK TLP is received from a port before another port has sent its PME Turn Off message then bit [0], PME_TO_ACK, of the PEXGCTRL register (Device 19, Function 0, Offset 17Ch) may not be set when all the acknowledges have been received. |

| Implication:                | When a system is transitioning from S0 to S3, S4 or S5 a system hang may occur if the PCI Express* Global Control Registers Completion Timeout value has been set too low.                                                                                                                                                                                                                           |

| Workaround:                 | Set bits [31:18], Completion Timeout, of the PEXGCTRL register (Device 19, Function 0, Offset 17Ch) to a value greater than 10 ms.                                                                                                                                                                                                                                                                   |

| Status:                     | No Fix                                                                                                                                                                                                                                                                                                                                                                                               |

| 21.                         | Masked completer abort status errors may be reported in the UNCERRSTS[0] register                                                                                                                                                                                                                                                                                                                    |

| Problem:                    | When bit [15], IO7MSK, of the UNCERRMSK[0] register (Device 0, Function 0, Offset 108h) is set to mask Completer Abort status errors, uncorrectable Completer Abort status errors may still be logged in bit [15], IO7ERR, of the UNCERRSTS[0] register (Device 0, Function 0, Offset 104h) register.                                                                                                |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Implication:                | A masked Completer Abort status error may be reported.                                                                                                                                                                                                                                                                                                                                               |

| Implication:<br>Workaround: | A masked Completer Abort status error may be reported.                                                                                                                                                                                                                                                                                                                                               |

### 22. SMBus TLOW:SEXT specification may be exceeded on SMBus 0 when the north bridge is clocked with a 266 MHz BUSCLK

- Problem: The System Management Bus (SMBus) Specification, Version 2.0 TLOW: SEXT specification of 25 ms maximum, which applies only to Slave ports, may be exceeded on SMBus 0 by devices with a BUSCLK of 266 MHz.

- Implication: A TLOW of ~31 ms may occur on SMBus 0. A Master is allowed to abort the transaction in progress to any slave that violates the TLOW: SEXT specification.

Workaround: None

Status: No Fix

# 23. First uncorrectable fatal bit of the root error status register may be incorrectly set when a second uncorrectable fatal error is received

- Problem: Bit [4], FRST\_UNCOR\_FATAL, of the RPERRSTS register (Device 0, 2–3, 4–7, Function 0, Offset 130h) may be incorrectly set if an Uncorrectable Fatal Error is received and bit [2], ERR\_FAT\_NOFAT\_RCVD, of the RPERRSTS register (Device 0, 2–3, 4–7, Function 0, Offset 130h) is set.

- Implication: An Uncorrectable Fatal Error which was not the first error received may be incorrectly indicated as the type of error that was first received.

- Workaround: None

- Status: No Fix

# 24. Bit [3], INTxST, of the PEXSTS register may be cleared when bit [10], INTxDisable, of the PEXCMD register is set

- Problem: When bit [10], INTxDisable, of the PEXCMD register (Device 0, 2–3, 4–8, Function 0, Offset 04h) is set to disable interrupts then bit [3], INTxST, of the PEXSTS register (Device 0, 2–3, 4–8, Function 0, Offset 06h) register may be cleared.

- Implication: An interrupt status that is pending may be incorrectly cleared.

Workaround: None

Status: No Fix

### 25. Valid formatted TLP with invalid type may hang system

- Problem: When a valid formatted TLP read is received, but it has an invalid type, it is incorrectly logged as a Master Abort Read transaction, updates the flow class status, and returns credit when it is supposed to ignore the transaction.

- Implication: Returning the Credits creates a discrepancy between the MCH and PCI Express\* partner. Eventually, the discrepancy in credits will cause a system hang. Receiving a valid formatted TLP with an invalid type is not expected to occur in a realistic system environment.

Workaround: None

Status: No Fix

### 26. PCI Express\* Compliance Test Failure: CBDMA Interrupt Line Register

Problem: The PCI Express\* compliance test TD\_1\_13 Interrupt Pin - Interrupt Line Register Test reports a RW failure for the interrupt Line Register bits [7:0] in Intel<sup>®</sup> 5100 MCH Chipsets. According to the *PCI Express\* Base Specification*, Rev. 1.0a, Section 7.5.1.5, the Interrupt Line Register bits [7:0] should be RW. The INTL register is implemented as Read/Write Once (RWO) in Intel<sup>®</sup> 5100 MCH Chipsets. The register becomes RO after BIOS initializes it, violating the *PCI Express\* Base Specification*, Rev. 1.0a. This is a minor violation because the DMA device does not have interrupt lines and INTL is not used by the Intel<sup>®</sup> 5100 MCH Chipset.

Implication: N/A

Workaround: N/A

Status: No Fix. Microsoft\* Certification has decided not to make this a requirement for any OS WHQL. See also Erratum 9 in this document.

### 27. PCI Express\* Compliance Test Failure: MSI Address Register

- Problem: The PCI Express\* compliance test TD\_1\_06 MSI Capability Structure Test reports a RO failure for the MSIAR bits [31:20] in Intel<sup>®</sup> 5100 MCH Chipsets. According to the *PCI Local Bus Specification*, Rev. 2.3, Section 6.8.1.4, Message Address for MSI, the Message Address Register bits [31:2] should be RW. The MSIAR in the Intel<sup>®</sup> 5100 MCH Chipset is a root port and is fixed to the Intel-specific IO\_APIC range of FEExh to route the MSI ensuring proper functionality of the MSI architecture.

- Implication: N/A

Workaround: N/A

Status: No Fix

### 28. Unpopulated ranks may cause performance degradation

- Problem: Refresh cycles to unpopulated ranks may cause performance degradation depending upon data pattern and number of unpopulated ranks.

- Implication: Performance degradation is possible up to approximately 5% on systems where less than all four ranks are populated. No degradation occurs if all four ranks are populated.

- Workaround: The BIOS includes a workaround to resolve the known instances of this erratum.

- Status: Fixed