# 82578 Layout Checklist (Version 2.2)

| <b>Project Name</b>  |                                                                                                                                                                                              |                                            |             |                 |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------|-----------------|

| <b>Fab Revision</b>  |                                                                                                                                                                                              |                                            |             |                 |

| <b>Date</b>          |                                                                                                                                                                                              |                                            |             |                 |

| <b>Designer</b>      |                                                                                                                                                                                              |                                            |             |                 |

| <b>Intel Contact</b> |                                                                                                                                                                                              |                                            |             |                 |

| <u>SECTION</u>       | <u>CHECK ITEMS</u>                                                                                                                                                                           | <u>REMARKS</u>                             | <u>DONE</u> | <u>COMMENTS</u> |

|                      | Completed by:                                                                                                                                                                                | Design Engineer Name:                      |             |                 |

| <b>General</b>       | Obtain the most recent documentation and specification updates.                                                                                                                              | Documents are subject to frequent change.  |             |                 |

|                      | Route the transmit and receive differential traces before routing the digital traces.                                                                                                        | Layout of differential traces is critical. |             |                 |

|                      | <b>IMPORTANT:</b> Recommend that all signals are routed in reference to a solid plane. If signals cross planes, stitching caps are required between the planes within 40 mils of the signal. |                                            |             |                 |

|                      | If the differential signals transition from a ground referenced layer to a power referenced layer, place a decoupling capacitor on the power and ground within 40 mils of the signal vias.   |                                            |             |                 |

| <u>SECTION</u>                       | <u>CHECK ITEMS</u>                                                                        | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                | <u>DONE</u> | <u>COMMENTS</u> |

|--------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>General</b>                       | Obtain the most recent stack-up information from your Printed Circuit Board (PCB) vendor. |                                                                                                                                                                                                                                                                                                               |             |                 |

|                                      | Refer to the <i>Intel® 5 Series Family PDGs</i> for detailed routing requirements.        |                                                                                                                                                                                                                                                                                                               |             |                 |

| <b>Placement of the 82578</b>        | Place the 82578 at least one inch from the edge of the board.                             | With closer spacing, fields can follow the surface of the magnetics module or wrap past edge of the board. As a result, EMI might increase.                                                                                                                                                                   |             |                 |

|                                      | Place the 82578 at least one inch from the magnetics module but less than four inches.    | Keep trace length under four inches from the 82578 through the magnetics to the RJ-45 connector. Signal attenuation can cause problems for traces longer than four inches. However, due to near field EMI and common mode noise, the 82578 should be placed at least one inch away from the magnetics module. |             |                 |

|                                      | Place the RBIAS compensation resistor less than one inch from the silicon.                |                                                                                                                                                                                                                                                                                                               |             |                 |

| <b>Clock Source (Crystal Option)</b> | Place crystal within 0.75 inches of the 82578.                                            | This reduces EMI.                                                                                                                                                                                                                                                                                             |             |                 |

|                                      | Place the crystal load capacitors within 0.09 inches of the crystal.                      |                                                                                                                                                                                                                                                                                                               |             |                 |

| <u>SECTION</u>                              | <u>CHECK ITEMS</u>                                                                                                                                                                                                                                                              | <u>REMARKS</u>                                                                                                                                                                           | <u>DONE</u> | <u>COMMENTS</u> |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>Clock Source<br/>(Crystal Option)</b>    | Keep clock lines away from other digital traces (especially reset signals), I/O ports, board edge, transformers and differential pairs.                                                                                                                                         | This helps reduce EMI. Do not route the crystal traces as differential pairs.                                                                                                            |             |                 |

| <b>Clock Source<br/>(Oscillator Option)</b> | Make sure that the oscillator has its own local power supply decoupling capacitors. Make sure the decoupling capacitors are within 0.25 inches of the oscillator.                                                                                                               | Helps oscillator stability.                                                                                                                                                              |             |                 |

|                                             | If the oscillator is shared or is more than two inches away from the 82578, a back-termination resistor should be placed near the oscillator. Note that it is better to not share this clock source. If it is shared keep the traces for the two clock lines matched in length. | This enables tuning to ensure that reflections do not distort the clock waveform. Matching shared clock lines keeps the reflections from one spur of the clock from affecting the other. |             |                 |

|                                             | Keep clock lines at least five times the dielectric thickness away from other digital traces (especially reset signals), I/O ports, board edge, transformers and differential pairs.                                                                                            | Helps reduce EMI.                                                                                                                                                                        |             |                 |

| <u>SECTION</u>                              | <u>CHECK ITEMS</u>                                                                                                                                                                                    | <u>REMARKS</u>                                                                                                                                                                                          | <u>DONE</u> | <u>COMMENTS</u> |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>Clock Source<br/>(Oscillator Option)</b> | Use a $50 \Omega$ transmission line for the trace between the oscillator and the 82578.                                                                                                               | This is a single-ended transmission line. Make sure the transmission line does not cross any plane cuts. Also use stitching capacitors as needed when transferring from one reference plane to another. |             |                 |

|                                             | If the oscillator is powered through a ferrite bead, make sure that the local decoupling capacitor is connected close to oscillator package power input pin. Use a pore for the isolated power input. | A local power well provides a way to isolate system noise from the main time base of the Ethernet. This improves jitter and Bit Error Rate (BER) results.                                               |             |                 |

| <b>General Power Supply Guidance</b>        | Use planes to deliver 3.3 Vdc, 2.5 Vdc, and 1.2 Vdc.                                                                                                                                                  | Narrow finger-like planes and very wide traces are allowed. If traces are used, 100 mils is the minimum.                                                                                                |             |                 |

| <u>SECTION</u>                       | <u>CHECK ITEMS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                              | <u>DONE</u> | <u>COMMENTS</u> |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>General Power Supply Guidance</b> | <p>Place decoupling and bulk capacitors close to 82578, with some along every side, using short, wide traces and large vias.</p> <p>Place these to minimize the inductance from each power pin to the nearest decoupling capacitor.</p> <p>The 3.3 Vdc, 1.2 Vdc, and 2.5 Vdc rails should have decoupler capacitors placed near the 82578.</p> <p>The 1.8 Vdc rail should have 1 <math>\mu</math>F of capacitance placed at the center tap of the transformer.</p> | If power is distributed on traces, bulk capacitors should be used at both ends. If power is distributed on cards, bulk capacitors should be used at the connector.                                                                                                                                                                          |             |                 |

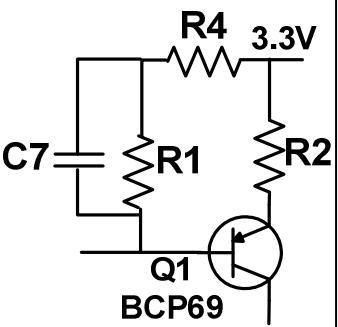

| <b>1.2 Vdc Power</b>                 | When using the internal regulator control circuit of the 82578 with an external PNP transistor, keep the trace length from the CTRL1P2 output ball to the transistor very short (less one inch) and use 15 mil (minimum) wide trace.                                                                                                                                                                                                                               | A low inductive loop should be kept from the regulator control pin, through the PNP transistor, and back to the 82578 from the transistor's collector output. The power pins should connect to the collector of the transistor through a power plane to reduce the inductive path. This reduces oscillation and ripple in the power supply. |             |                 |

|                                      | The 1.2 Vdc regulating circuit requires 1/2 inch x 1/2 inch thermal relief pads for each PNP.                                                                                                                                                                                                                                                                                                                                                                      | The pads should be placed on the top layer, under the PNP. Refer to BCP69 vendor documentation for additional guidance.                                                                                                                                                                                                                     |             |                 |

| <u>SECTION</u>              | <u>CHECK ITEMS</u>                                                                                                                                  | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>DONE</u> | <u>COMMENTS</u> |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

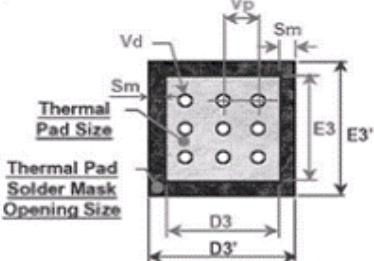

| <b>Epad</b>                 | Use appropriate number of vias to connect Epad to ground.                                                                                           | <p>Refer to the <i>Intel® 5 Series Family PDG</i> for additional details.</p> <p>Note that the Epad connection is the only source for ground and is used for both electrical and thermal.</p>  <p>Thermal pad size = <math>D_3 * E_3 = D_2 * E_2</math>.<br/> Solder mask opening size = <math>D_3' * E_3' = (D_3 + 2*Sm) * (E_3 + 2*Sm) = (D_2 + 0.1) * E_2 + 0.1</math><br/> where <math>Sm = 0.05</math> mm (machine capability)</p> <p><math>D_2, E_2</math> are exposed die attach pad size</p> <p>Thermal via diameter <math>V_d</math> (circled hole)<br/> <math>V_d = 0.3 \sim 0.33</math> mm (general drilling machine capability)<br/> where thermal via is a Plated Through Hole (PTH) and plugged in solder mask from top-side of PCB.</p> <p>The thermal via pitch <math>V_p</math><br/> <math>V_p = 1.0 \sim 1.25</math> mm</p> |             |                 |

| <b>PCIe-Based Interface</b> | Place the AC coupling capacitors on the PCI-based Tx traces as close as possible to the 82578 but not further than 250 mils (PCIe 1.0 requirement). | Size 0402, X7R is recommended. The AC coupling capacitors should be placed near the transmitter for the PCIe-based interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                 |

| <u>SECTION</u>              | <u>CHECK ITEMS</u>                                                                                                             | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>DONE</u> | <u>COMMENTS</u> |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>PCIe-Based Interface</b> | Make sure the trace impedance for the PCIe-based differential pairs is $85 \Omega \pm 15\%$ .                                  | <p>Simulation shows <math>85 \Omega</math> differential trace impedances meets Intel's PCIe-based minimum receive eye requirements when using the Customer Reference Board (CRB) design stack up.</p> <p>When using the CRB design stack up, Intel recommends that board designers use a <math>85 \Omega</math> differential trace impedance for PCIe-based I/O with the expectation that the center of the impedance is always targeted at <math>85 \Omega</math>. The <math>\pm 15\%</math> tolerance is provided to allow for board manufacturing process variations and not lower target impedances.</p> |             |                 |

|                             | Match trace lengths within each PCIe-based pair on a segment-by-segment basis. Match trace lengths within a pair to five mils. | <p>A PCIe segment is defined as any trace within the same layer. For example, transitioning from one layer to another through a via is considered as two separate PCIe segments. The differential pairs within each segment needs to be matched to 5 mils.</p> <p>Refer to the Intel® 5 Series Family PDGs for additional placement and routing requirements.</p>                                                                                                                                                                                                                                            |             |                 |

| <u>SECTION</u>              | <u>CHECK ITEMS</u>                                                                                                                                                                                                                 | <u>REMARKS</u>                                                                                                                                                          | <u>DONE</u> | <u>COMMENTS</u> |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>PCIe-Based Interface</b> | Use a minimum of 15 mil (0.381 mm) pair-to-pair spacing for board designs that use approximately 3 mil dielectric thickness in the design stack up.                                                                                | Pair-to-pair spacing is five times the thickness of the material.                                                                                                       |             |                 |

|                             | Make sure the PCIe clock differential pair is routed using $100 \Omega$ characteristic impedance. Keep a spacing of three times the dielectric thickness between the PCIe clock and any other traces (digital, analog, and power). |                                                                                                                                                                         |             |                 |

|                             | If any of the PCIe signals cross a plane or transfers from one plane to another, add stitching capacitors to provide a return path for the common mode currents.                                                                   | This reduces EMI.                                                                                                                                                       |             |                 |

| <b>SMBus</b>                | Connect the SMBus using little or no stubs at the pull-up resistor.                                                                                                                                                                |                                                                                                                                                                         |             |                 |

| <b>MDI Interface</b>        | Design traces for $100 \Omega$ differential impedance ( $\pm 15\%$ ). Refer to the <i>Intel® 5 Series Family PDG</i> for spacing guidance between any signal and the MDI channels.                                                 | Primary requirement for 10/100/1000 Mb/s Ethernet. Paired $50 \Omega$ traces do not make $100 \Omega$ differential. An impedance calculator can be used to verify this. |             |                 |

| <u>SECTION</u>       | <u>CHECK ITEMS</u>                                                                                                                                                   | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                 | <u>DONE</u> | <u>COMMENTS</u> |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>MDI Interface</b> | Design traces for 100 W differential impedance ( $\pm 15\%$ ). Refer to the Intelâ 5 Series Family PDG for spacing guidance between any signal and the MDI channels. | Please use the 82578 Trace Length Calculator available from Intel. Trace width and separation of the MDI pairs is determined by the board stack up in order to achieve the correct impedance. For applications that require a longer MDI trace lengths, Intel recommends that thicker dielectric or lower Er materials be used. This permits higher differential trace impedance and wider, lower loss traces. |             |                 |

|                      |                                                                                                                                                                      | Target differential impedance is $100 \Omega \pm/15\%$ . If a stack up does not allow for $100 \Omega \pm/15\%$ differential trace impedance, consider trying a stack up that allows $95 \Omega \pm/10\%$ .                                                                                                                                                                                                    |             |                 |

|                      |                                                                                                                                                                      | Stripline is NOT recommended due to thinner more resistive signal layers.                                                                                                                                                                                                                                                                                                                                      |             |                 |

|                      | Maximum MDI trace length is four inches.                                                                                                                             | For applications that require a longer MDI trace length of more than four inches, Intel recommends that thicker dielectric or lower Er materials be used. This permits higher differential trace impedance and wider, lower loss traces.                                                                                                                                                                       |             |                 |

|                      | Place the MDI termination within 250 mils of the 82578. Keep the trace stub lengths to a minimum. Make sure that the matching or the pair lengths is maintained.     |                                                                                                                                                                                                                                                                                                                                                                                                                |             |                 |

| <u>SECTION</u>       | <u>CHECK ITEMS</u>                                                                                                                                              | <u>REMARKS</u>                                                                                                                                                           | <u>DONE</u> | <u>COMMENTS</u> |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>MDI Interface</b> | Do not make 90° bends.                                                                                                                                          | Bevel corners with turns based on 45° angles.                                                                                                                            |             |                 |

|                      | Minimize through holes (vias).                                                                                                                                  | If using through holes (vias), the budget is two 10 mil finished hole size vias per trace.                                                                               |             |                 |

|                      | Keep traces close together inside a differential pair.                                                                                                          |                                                                                                                                                                          |             |                 |

|                      | Pair-to-pair trace length does not have to be matched as differences are not critical.                                                                          | The difference between the length of longest pair and the length of the shortest pair should be kept below two inches.                                                   |             |                 |

|                      | Keep differential pairs more than seven times the dielectric thickness away from each other and other traces, including NVM traces and parallel digital traces. | This minimizes crosstalk and noise injection. Tighter spacing is allowed for the first 200 mils of trace near of the components.                                         |             |                 |

|                      | Ensure that the MDI traces (including Bob Smith termination) between the magnetics and the RJ-45 connector are at least 80 mils from all other traces.          | This is to ensure the system can survive a high voltage on the MDI cable. (Hi-POT) Refer to the <i>Intel® 5 Series Family PDGs</i> for routing and placement guidelines. |             |                 |

|                      | Keep traces at least 0.1 inches away from the board edge.                                                                                                       | This reduces EMI.                                                                                                                                                        |             |                 |

|                      | Do not have stubs along the traces.                                                                                                                             | Stubs cause discontinuities.                                                                                                                                             |             |                 |

| <u>SECTION</u>       | <u>CHECK ITEMS</u>                                                                 | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>DONE</u> | <u>COMMENTS</u> |

|----------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>MDI Interface</b> | Route traces on appropriate layers.                                                | <p>Run pairs on outer layers to improve routing. Make sure the adjacent layer is a ground layer. There must be no splits in the GND planes under the MDI channel.</p> <p>When differential signals transition from one board layer to another, place ground vias within 40 mils of the signal vias.</p> <p>Avoid broadside coupling to traces on other layers. The broadside effect significantly increases the insertion loss and reduce signal quality.</p> <p>Make sure digital signals on adjacent layers cross at 90° angles.</p> <p><b>Note:</b> Refer to the general section of the layout checklist for guidance on routing signals over reference planes.</p> |             |                 |

|                      | Total trace resistance from the 82578 to the LAN magnetics should not exceed 10 Ω. | The trace resistance includes the series resistance of any components that might be present such as inductors or resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                 |

| <u>SECTION</u>          | <u>CHECK ITEMS</u>                                                                                                                                                                                       | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>DONE</u> | <u>COMMENTS</u> |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>Chassis Ground</b>   | Consider using a separate chassis ground for the LAN connector.                                                                                                                                          | <p>If using a discrete magnetics module, provide a separate chassis ground "island" to ground the shroud of the RJ-45 connector and to terminate the line side of the magnetics module. This design improves EMI behavior.</p> <p>Split in ground plane should be at least 50 mils wide. Split should run under center of magnetics module. Differential pairs never cross the split.</p> <p>If using an integrated magnetics module without USB, provide a separate chassis ground "island" to ground around the RJ-45 connector. Split in ground plane should be at least 50 mils wide.</p> <p>If using an integrated magnetics module with USB, do not use a separate chassis ground.</p> <p>Refer to the <i>Intel® 5 Series Family PDGs</i> for more details.</p> |             |                 |

| <b>Magnetics Module</b> | Capacitors connected to center taps should be placed very close (less than 0.1 inch recommended) to the integrated magnetics module. Connect a 1 $\mu$ F capacitor near the magnetics module (1/4 inch). | <p>This improves BER.</p> <p>Note that the 0.1 <math>\mu</math>F capacitors are only needed for discrete magnetics that don't have them integrated internally.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                 |

| <u>SECTION</u>          | <u>CHECK ITEMS</u>                                                                                                                       | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                              | <u>DONE</u> | <u>COMMENTS</u> |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>Magnetics Module</b> | The system side center tap on the transformer should be connected to the VCT power supply through a 100 mil trace or a power plane pore. | The center tap voltage is critical to performance of MDI interface. Any voltage drop can cause violations to the specification. Assure that adequate trace width is provided and that the feed is low inductance and low resistance. Refer to the VCT copper loss calculator to determine VCT trace geometry. Contact your Intel representative for access. |             |                 |

|                         | Place the magnetics module (closer to RJ-45) between the 82578 and the RJ-45.                                                            | Applies to designs using discrete magnetics modules only.                                                                                                                                                                                                                                                                                                   |             |                 |

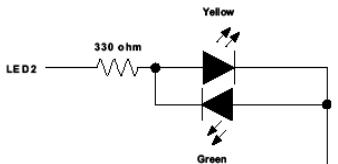

| <b>LED Circuits</b>     | Keep LED traces away from sources of noise, for example, high speed digital traces running in parallel.                                  | LED traces can carry noise into integrated magnetics modules, RJ-45 connectors, or out to the edge of the board, increasing EMI.                                                                                                                                                                                                                            |             |                 |

|                         | If using decoupling capacitors on LED lines, place them carefully.                                                                       | Capacitors on LED lines should be placed near the LEDs (typically adjacent to integrated magnetics module).                                                                                                                                                                                                                                                 |             |                 |

| <u>SECTION</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>CHECK ITEMS</u> | <u>REMARKS</u> | <u>DONE</u> | <u>COMMENTS</u> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-------------|-----------------|

| INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications. |                    |                |             |                 |

| Intel may make changes to specifications and product descriptions at any time, without notice.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                |             |                 |

| This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                |             |                 |

| The 82578 GbE Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                |             |                 |

| *Other names and brands may be claimed as the property of others.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |                |             |                 |

| Copyright © Intel Corporation 2004, 2005, 2006, 2007, 2008, 2009, 2010.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                |             |                 |

## 82578 Schematic Checklist (Version 2.2)

| <b>Project Name</b>  |                                                                                                                                                                                              |                                           |             |                 |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------|-----------------|

| <b>Fab Revision</b>  |                                                                                                                                                                                              |                                           |             |                 |

| <b>Date</b>          |                                                                                                                                                                                              |                                           |             |                 |

| <b>Designer</b>      |                                                                                                                                                                                              |                                           |             |                 |

| <b>Intel Contact</b> |                                                                                                                                                                                              |                                           |             |                 |

| <b>Reviewer</b>      |                                                                                                                                                                                              |                                           |             |                 |

| <b>SECTION</b>       | <b>CHECK ITEMS</b>                                                                                                                                                                           | <b>REMARKS</b>                            | <b>DONE</b> | <b>COMMENTS</b> |

|                      | Completed by:                                                                                                                                                                                | Design Engineer Name:                     |             |                 |

| <b>General</b>       | Obtain the most recent documentation and specification updates.                                                                                                                              | Documents are subject to frequent change. |             |                 |

|                      | Use this checklist in conjunction with the Customer Reference Board (CRB) reference schematics.                                                                                              |                                           |             |                 |

|                      | Observe instructions for special pins needing pull-up or pull-down resistors.                                                                                                                |                                           |             |                 |

|                      | Refer to the <i>Intel® 5 Series Family Platform Design Guide (PDG)</i> , the <i>Intel® 5 Series Express Chipset EDS</i> , and the Specification Update for integrated GbE LAN (MAC) details. |                                           |             |                 |

| <b>Support Pins</b>  | Connect TEST_EN (pin 30) through a 1 KΩ pull-down resistor.                                                                                                                                  |                                           |             |                 |

| <u>SECTION</u>        | <u>CHECK ITEMS</u>                                                                                                                                                                                                     | <u>REMARKS</u>                                                                                                                                                          | <u>DONE</u> | <u>COMMENTS</u> |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>Support Pins</b>   | Connect LAN_DISABLE_N (pin 3) to a 10 KΩ pull-up resistor to 3.3 Vdc and a 10 KΩ no-stuff pull-down resistor to ground. Connect to Intel® 5 Series Express Chipset LAN_PHY_PWR_CTRL (pin AU34) through a 0 Ω resistor. |                                                                                                                                                                         |             |                 |

|                       | Connect RBIAS (pin 12) to a 2.37 KΩ 1% pull-down resistor.                                                                                                                                                             |                                                                                                                                                                         |             |                 |

|                       | Connect RSVD_VCC3P3 (pin 1) and RSVD_VCC3P3 (pin 2) to a 2.37 KΩ 5% pull-up resistors to 3.3 Vdc.                                                                                                                      | A value of 3.01 KΩ is suggested. A range of 2.37 KΩ to 10 KΩ can also be used.                                                                                          |             |                 |

|                       | Connect the Epad (pin 49) to ground plane.                                                                                                                                                                             | Refer to <i>Intel® 5 Series Family PDG</i> for more information.                                                                                                        |             |                 |

| <b>PCIe Interface</b> | Connect PCIe interface pins to corresponding pins on the Intel® 5 Series Express Chipset.                                                                                                                              | Recommend that the default connection be lane six of the Intel® 5 Series Express Chipset. However, the PCIe interface pins can be connected to any available PCIe port. |             |                 |

|                       | Connect PETn (pin 39) and PETp (pin 38) to Intel® 5 Series Express Chipset PERn6 (pin D8) and PERp6 (pin C9), respectively.                                                                                            |                                                                                                                                                                         |             |                 |

|                       | Connect PERn (pin 42) and PERp (pin 41) to Intel® 5 Series Express Chipset PETn6 (pin G11) and PETp6 (pin H11), respectively.                                                                                          |                                                                                                                                                                         |             |                 |

| <u>SECTION</u>        | <u>CHECK ITEMS</u>                                                                                                                                                                      | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>DONE</u> | <u>COMMENTS</u> |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>PCIe Interface</b> | Place AC coupling capacitors (0.1 $\mu$ F) near the PCIe transmitter (PCIe 1.0 requirement).                                                                                            | Size 0402, X7R is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                 |

|                       | Connect PE_CLKn (pin 45) and PE_CLKp (pin 44) to Intel® 5 Series Express Chipset CLKOUT_PCIE5N (pin Y8) and CLKOUT_PCIE5P (pin Y9), respectively.                                       | The PCIe clock buffer can be connected to any clock port. It does not have to be port 5. This connection should match the CLK_REQ_N port number.                                                                                                                                                                                                                                                                                                                                               |             |                 |

|                       | Connect CLK_REQ_N (pin 48) through a 10 K $\Omega$ pull-up resistor to 3.3 Vdc and then through a series 0 $\Omega$ resistor to Intel® 5 Series Express Chipset PCIECLKRQ5# (pin AW38). | <p>CLK_REQ_N can be connected to one of the eight Intel® 5 Series Express Chipset inputs (PCIECLKRQ[7:0]#). This connection should match the PCIe clock output port number.</p> <p>If connecting this PHY output to the PCIECLKRQ1# or PCIECLKRQ2# pins (powered by the core well), the pull-up resistor needs to be connected to the +V3.3S rail. If connecting to any of the other PCIECLKRQ# pins (powered by Sus well), the pull-up resistor needs to be connected to the +V3.3A rail.</p> |             |                 |

| <u>SECTION</u>        | <u>CHECK ITEMS</u>                                                                                                                                                                      | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>DONE</u> | <u>COMMENTS</u> |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>PCIe Interface</b> | Connect CLK_REQ_N (pin 48) through a 10 K $\Omega$ pull-up resistor to 3.3 Vdc and then through a series 0 $\Omega$ resistor to Intel® 5 Series Express Chipset PCIECLKRQ5# (pin AW38). | <p>When the PHY is powered down, connecting to the +V3.3A rail results in a small amount of current leakage (~300 <math>\mu</math>A) through the PHY CLK_REQ_N buffer. This results in a small residual voltage (~0.6 Vdc) on the PHY +V3.3 power rail. The power impact is less than 1 mW and does not affect PHY functionality or reliability. Designers can avoid this leakage by connecting the PHY CLK_REQ_N output to the PCIECLKREQ#1 or PCIECLKREQ#2 pins or by adding a blocking FET.</p> <p><b>Note:</b> Additional guidance is available in the <i>Intel® 5 Series Family PDGs</i>.</p> |             |                 |

|                       | Connect PE_RST_N (pin 36) through a series 0 $\Omega$ resistor to Intel® 5 Series Express Chipset PLTRST# (pin AV34).                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                 |

| <b>SMBus</b>          | Connect pull-up resistors to SMB_CLK (pin 28) and SMB_DATA (pin 31).                                                                                                                    | <p>Use 2.2 K<math>\Omega</math> 5% pull-up resistors. Ensure pull-ups are connected to the power rail that is present while in Sx states and while transitioning from G3 to S5.</p>                                                                                                                                                                                                                                                                                                                                                                                                                |             |                 |

|                       |                                                                                                                                                                                         | <p>Note that the PHY SMBus address is 0xC8 and default MAC SMBus address is 0xE0.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                 |

| <u>SECTION</u>                       | <u>CHECK ITEMS</u>                                                                                                                                                                               | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                       | <u>DONE</u> | <u>COMMENTS</u> |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>SMBus</b>                         | Connect SMB_CLK (pin28) and SMB_DATA (pin31) to Intel® 5 Series Express Chipset SML0CLK (pin AW33) and SML0DATA (pin AT34), respectively.                                                        | The Intel® 5 Series Express Chipset has a dedicated SMBus for the PHY (SMBus channel 0). No other device (such as an external BMC) can be connected to SML0CLK or SML0DATA.                                                                                                                                                          |             |                 |

| <b>Clock Source (Crystal Option)</b> | Use a 25 MHz 30 ppm accuracy @ 25 °C crystal. Avoid components that introduce jitter.                                                                                                            | Parallel resonant crystals are required. The calibration load should be 18 pF. Specify Equivalent Series Resistance (ESR) to be 50 Ω or less. Avoid PLL clock buffers.                                                                                                                                                               |             |                 |

|                                      | Connect two load capacitors to the crystal; one on XTAL_OUT (pin 9) and one on XTAL_IN (pin 10). Use 27 pF capacitors as a starting point, but be prepared to change the value based on testing. | Capacitance affects accuracy of the frequency and must be matched to crystal specifications, including estimated trace capacitance in calculation.<br><br>Use capacitors with low ESR (types C0G or NPO, for example). Refer to the Datasheet and the Intel Ethernet Controllers Timing Device Selection Guide for more information. |             |                 |

|                                      | Connect XTAL_IN (pin 10) and XTAL_OUT (pin 9) to the appropriate crystal pins.                                                                                                                   |                                                                                                                                                                                                                                                                                                                                      |             |                 |

| <u>SECTION</u>                                  | <u>CHECK ITEMS</u>                                                                                                                                                                 | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                                 | <u>DONE</u> | <u>COMMENTS</u> |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|

| <b>Clock Source<br/>(Oscillator<br/>Option)</b> | Connect the output of the clock oscillator to pin XTAL_IN (pin 10) through appropriate signal conditioning (capacitance-coupled voltage divider). Do not connect XTAL_OUT (pin 9). | Use a 25 MHz 50 ppm oscillator. The oscillator needs to maintain 50 ppm under all applicable temperature and voltage conditions. Avoid PLL clock buffers. Place voltage divider near the XTAL_IN of the PHY (less than 325 mils).                                                                                                              |             |                 |

|                                                 | Use a local decoupling capacitor on the oscillator power supply. Include a bulk 1 $\mu$ f capacitor as well as a high frequency 0.1 $\mu$ f decoupling capacitor.                  | If isolated with a ferrite bead, include a bulk decoupling capacitor next to the oscillator. Refer to the <i>Intel® 5 Series Family PDG</i> for more details.                                                                                                                                                                                  |             |                 |

|                                                 | The signal from the oscillator must be AC coupled into the 82578.                                                                                                                  | The 82578 has internal circuitry to set the input common mode voltage.                                                                                                                                                                                                                                                                         |             |                 |

|                                                 | The amplitude of the clock signal going into the 82578 should be within the maximum input clock amplitude specification for the 82578.                                             | The clock oscillator has an internal voltage regulator to isolate it from the external noise of other circuits to minimize jitter. For example, if a 3.3 Vdc oscillator is used, its output signal should be attenuated to a maximum value with a resistive divider circuit. Refer to the <i>Intel® 5 Series Family PDGs</i> for more details. |             |                 |

|                                                 | If the oscillator driver is further away than two inches then add a 33 $\Omega$ series resistor directly at the output.                                                            |                                                                                                                                                                                                                                                                                                                                                |             |                 |

| <u>SECTION</u>               | <u>CHECK ITEMS</u>                                                                                                                                                    | <u>REMARKS</u>                                                                                                                                                                                                                                                                                                                         | <u>DONE</u> | <u>COMMENTS</u> |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|