# **Gate Dielectric Scaling for High-Performance CMOS: from SiO<sub>2</sub>/PolySi to High-K/Metal-Gate**

**Robert Chau**

**Intel Fellow**

**Technology and Manufacturing Group

Intel Corporation**

**November 06 2003**

# Content

- **Introduction**

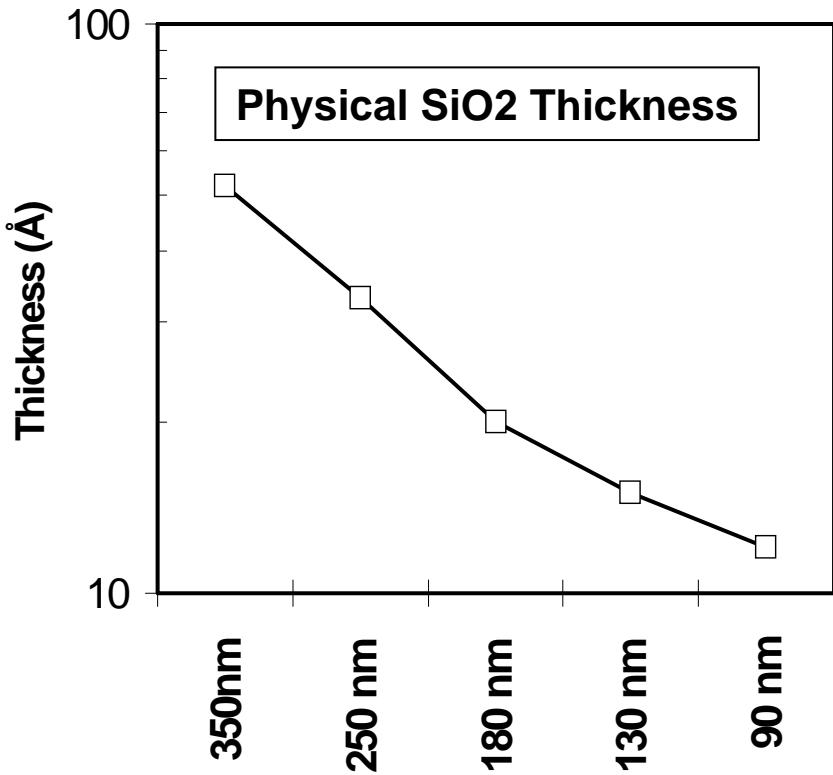

- **SiO<sub>2</sub> Scaling**

- **Review on High-K Problems**

- **Significant Breakthroughs in High-K/Metal-Gate**

- **High-K/Metal-gate NMOS & PMOS Transistors with Record-Setting Drive Performance**

- **Summary**

# Introduction

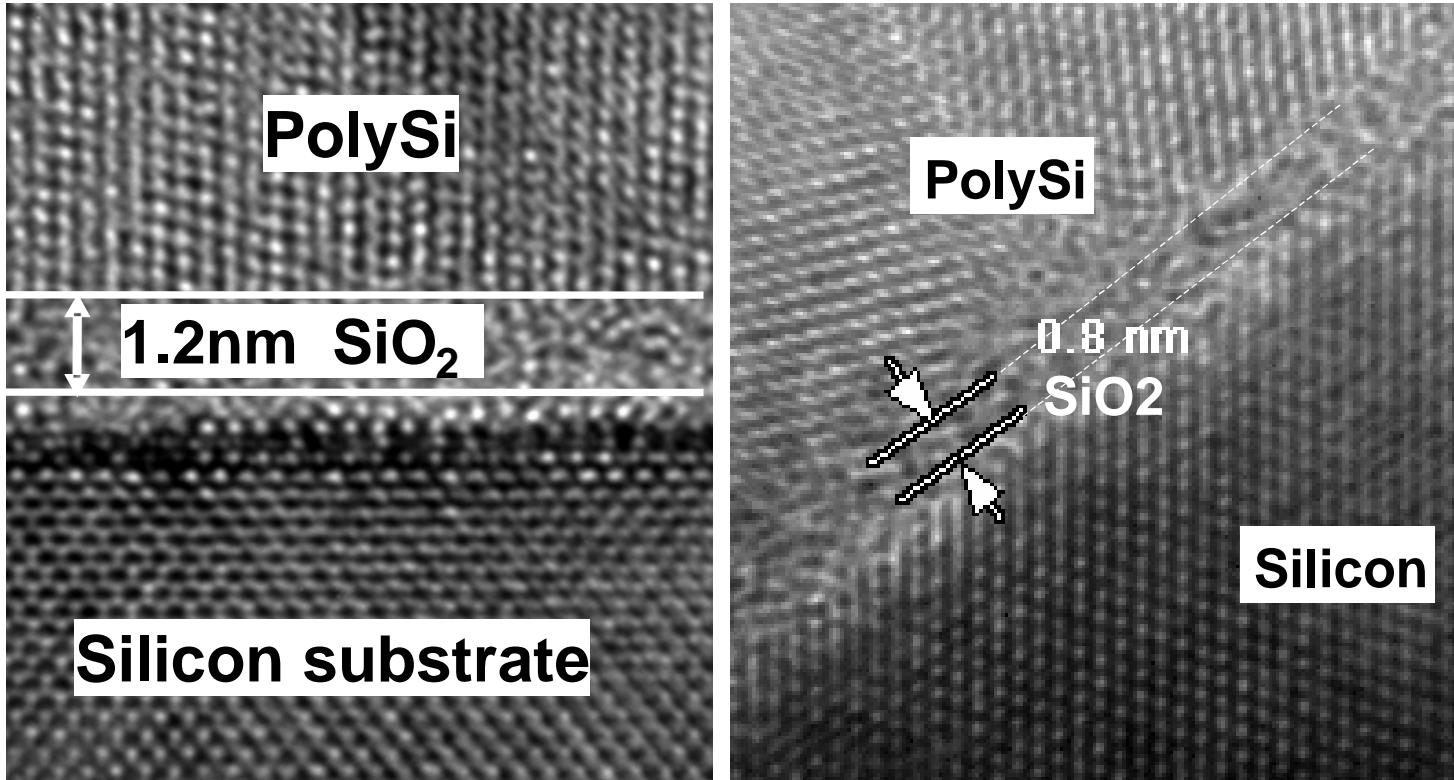

- **1.2nm physical  $\text{SiO}_2$  in production in our 90nm logic technology node**

- **0.8nm physical  $\text{SiO}_2$  in our research transistors with 15nm physical  $L_g$**

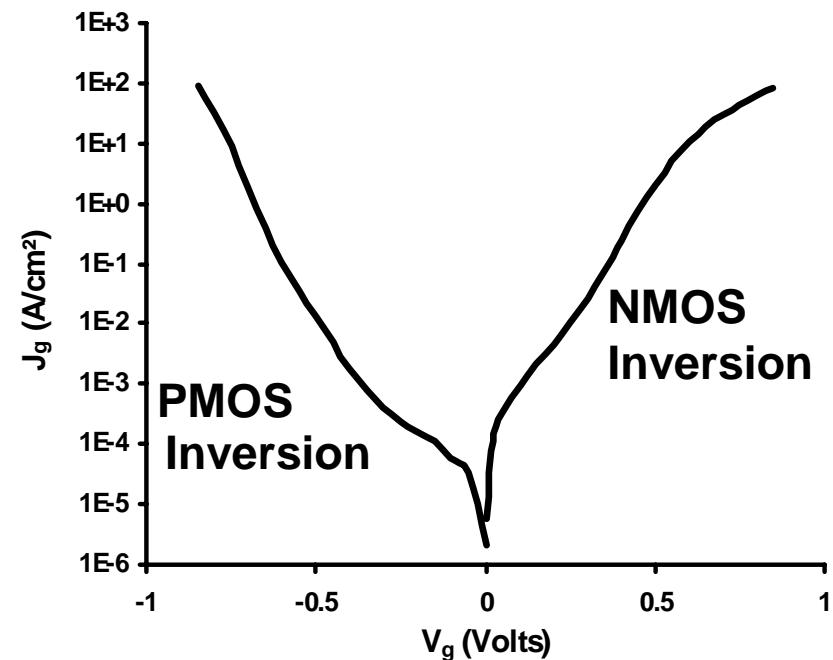

- **Gate leakage is increasing with reducing physical  $\text{SiO}_2$  thickness**

- **$\text{SiO}_2$  running out of atoms for further scaling**

- **Will eventually need high-K**

# SiO<sub>2</sub> Scaling

- 1.2nm physical SiO<sub>2</sub> in production (90nm logic node)

- 0.8nm physical SiO<sub>2</sub> in research transistors

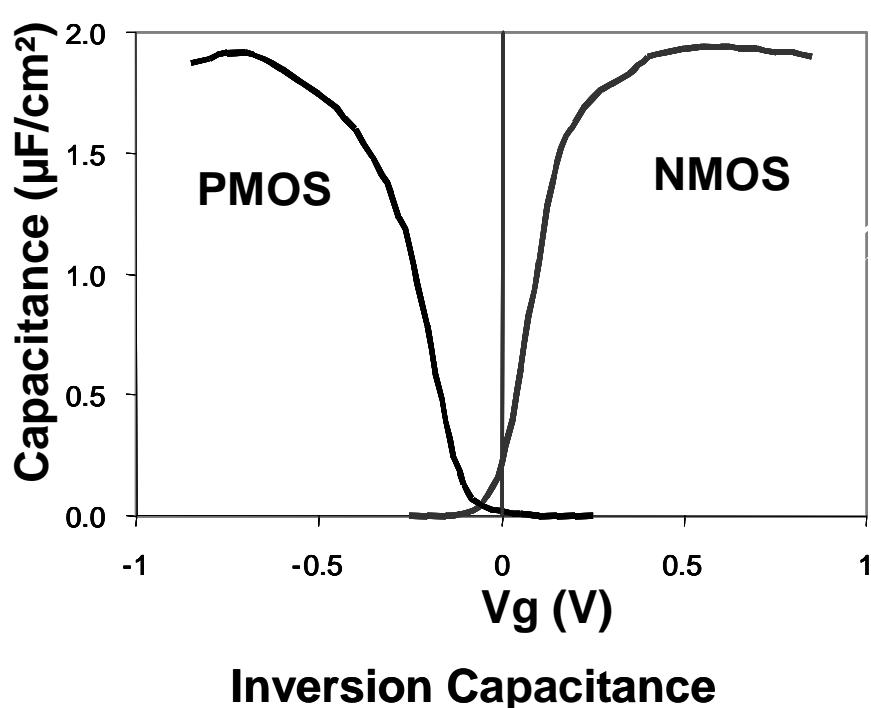

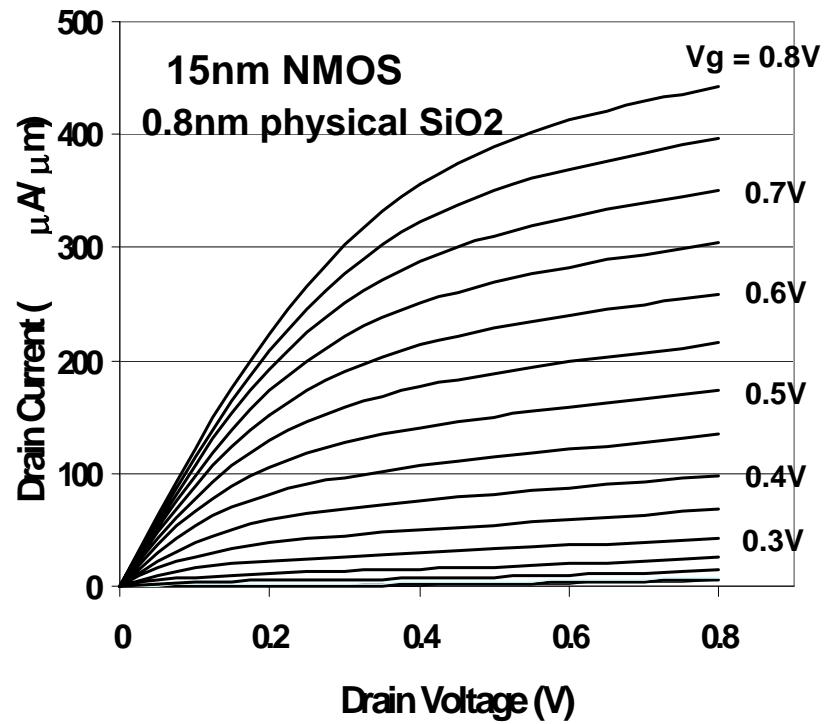

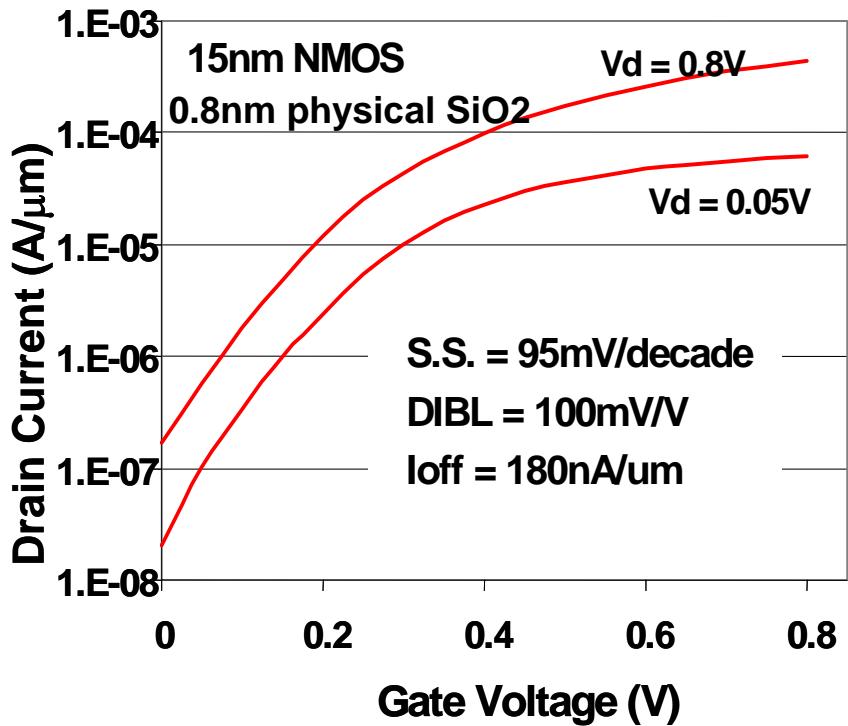

# Electrical Characteristics of 0.8nm Physical SiO<sub>2</sub> & PolySi Gate

# Research Transistor with 15nm Physical Lg and 0.8nm Physical SiO<sub>2</sub> and PolySi Gate

- Well-controlled short-channel characteristics

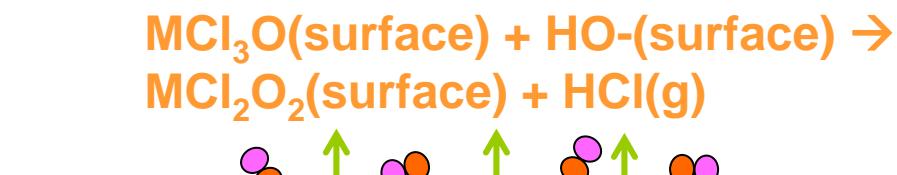

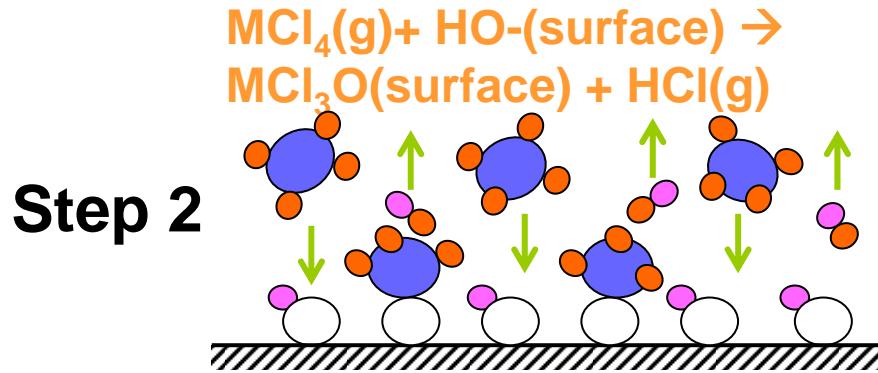

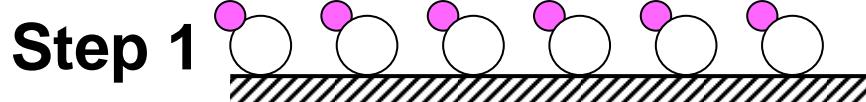

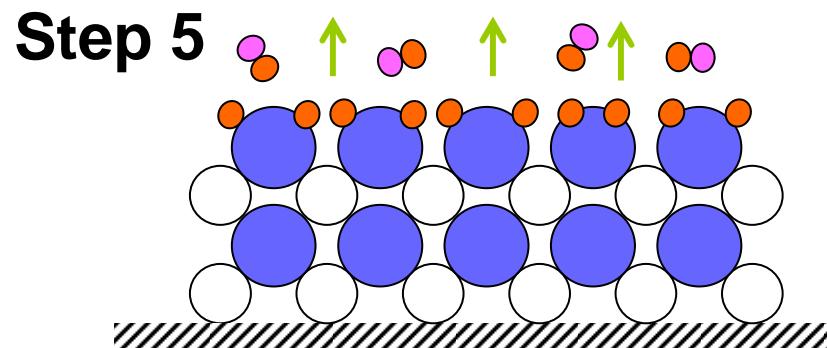

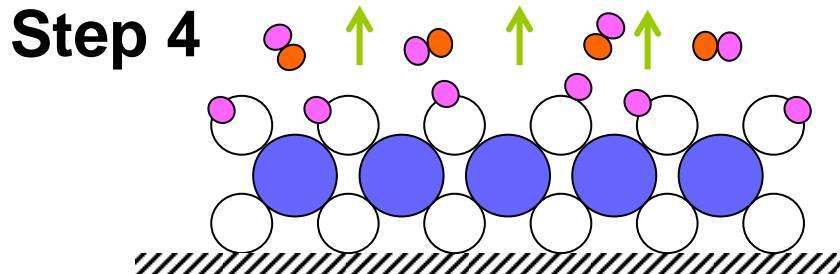

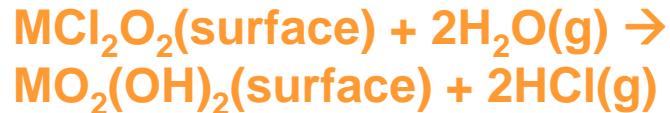

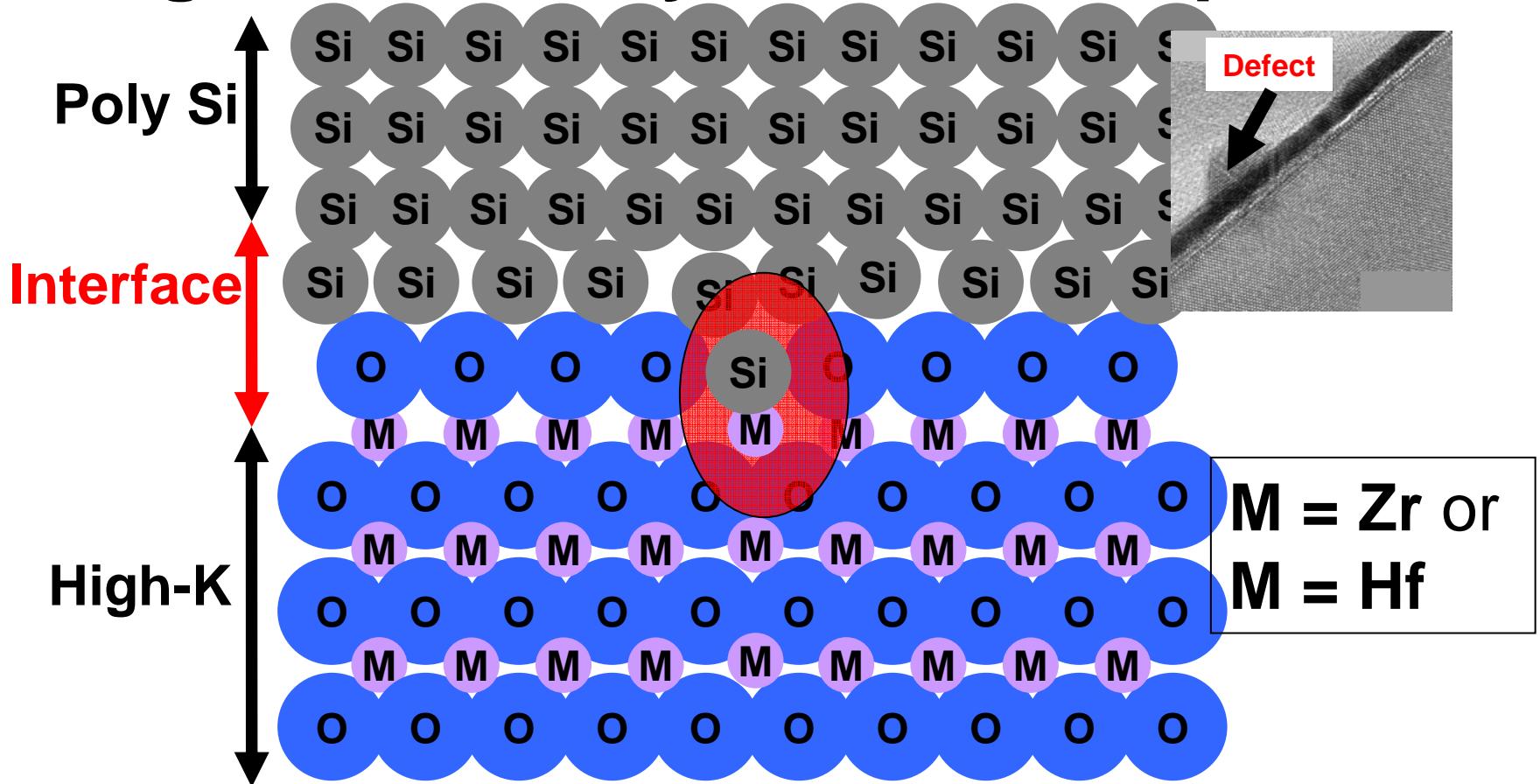

# Formation of High-K: Atomic Layer Deposition

Hydroxyl surface formed in preclean

- Sequential introduction of precursor molecules  $\text{MCl}_4(\text{g})$  and  $\text{H}_2\text{O}(\text{g})$ ;  $\text{M} = \text{Zr}$  or  $\text{M} = \text{Hf}$

# Review on High-K Problems

## (High-K/PolySi-Gate)

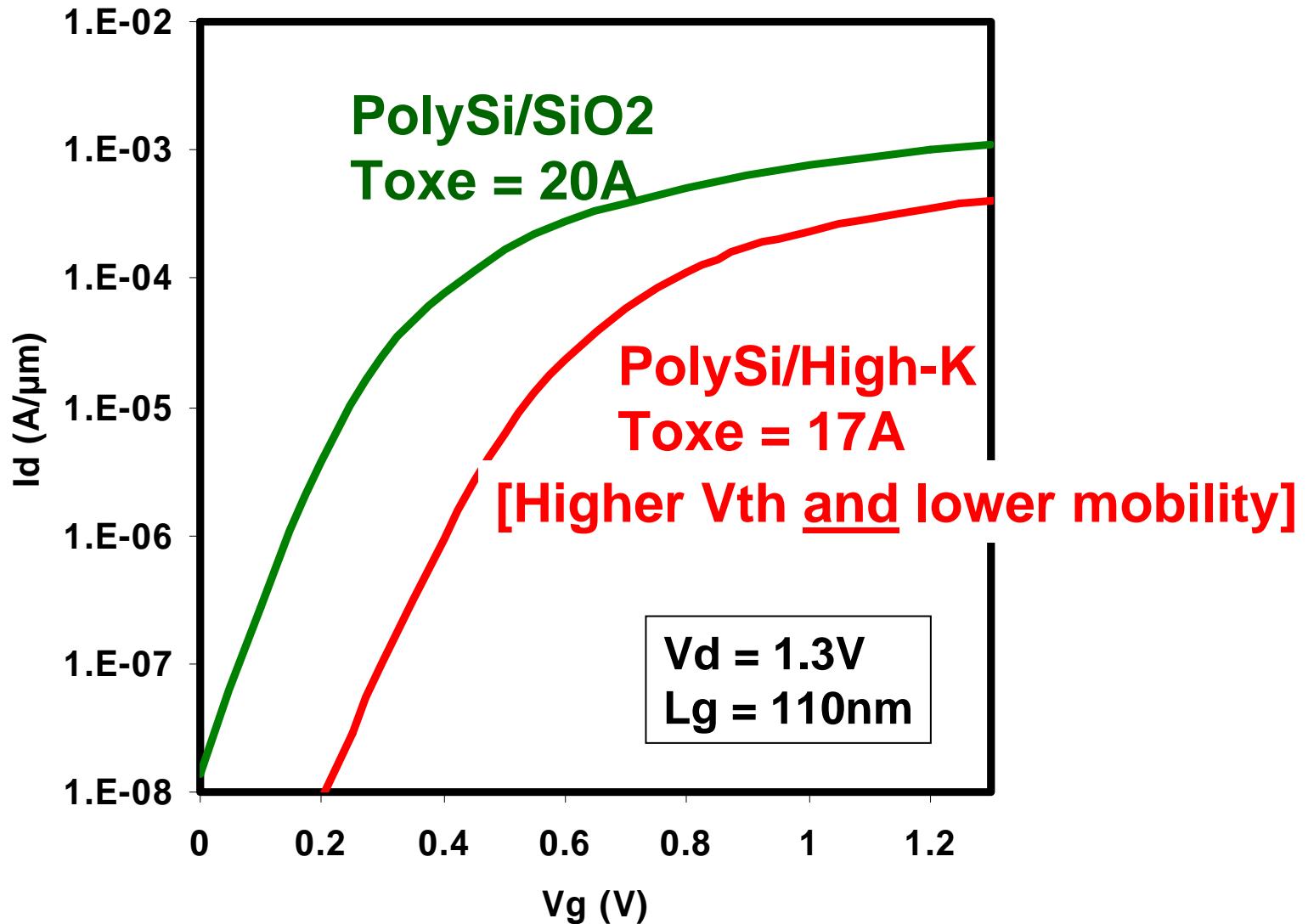

- High-K and polySi gate are incompatible due to Fermi level pinning at the high-K and polySi interface which causes high threshold voltages in transistors

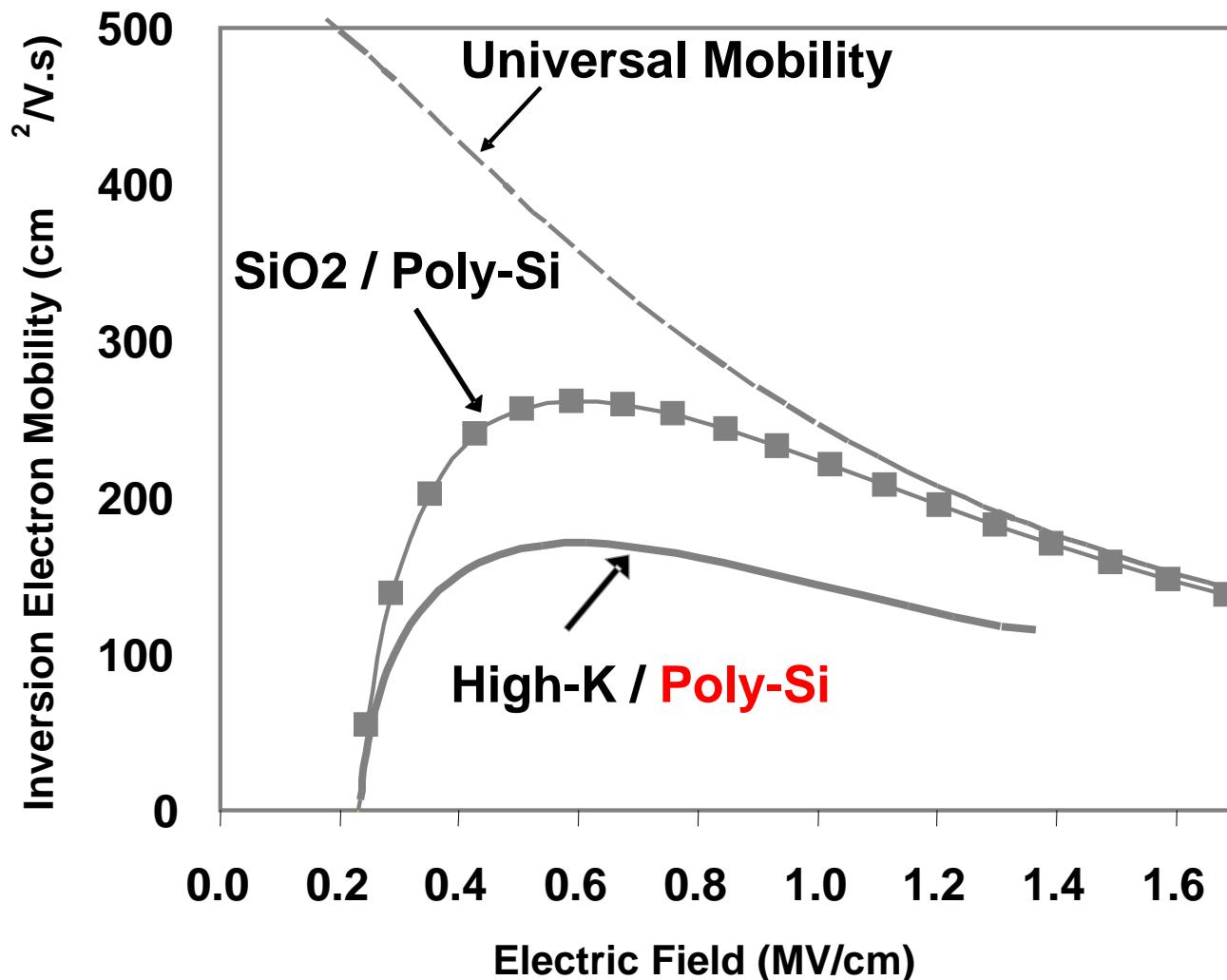

- High-K/polySi transistors exhibit severely degraded channel mobility due to the coupling of SO phonon modes in high-K to the inversion channel charge carriers

# High-K and PolySi are Incompatible

- Defect formation at the polySi-high-K interface

- TCAD simulation shows it takes only 1 defect out of 100 surface atoms to “pin” the transistor threshold voltage (high  $V_{th}$ )

# Mobility Degradation in High-K/PolySi

# Problems of High-K/PolySi Transistors

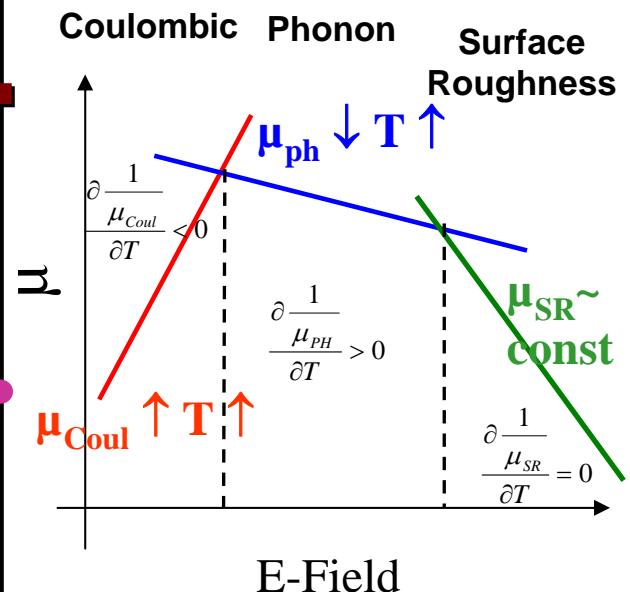

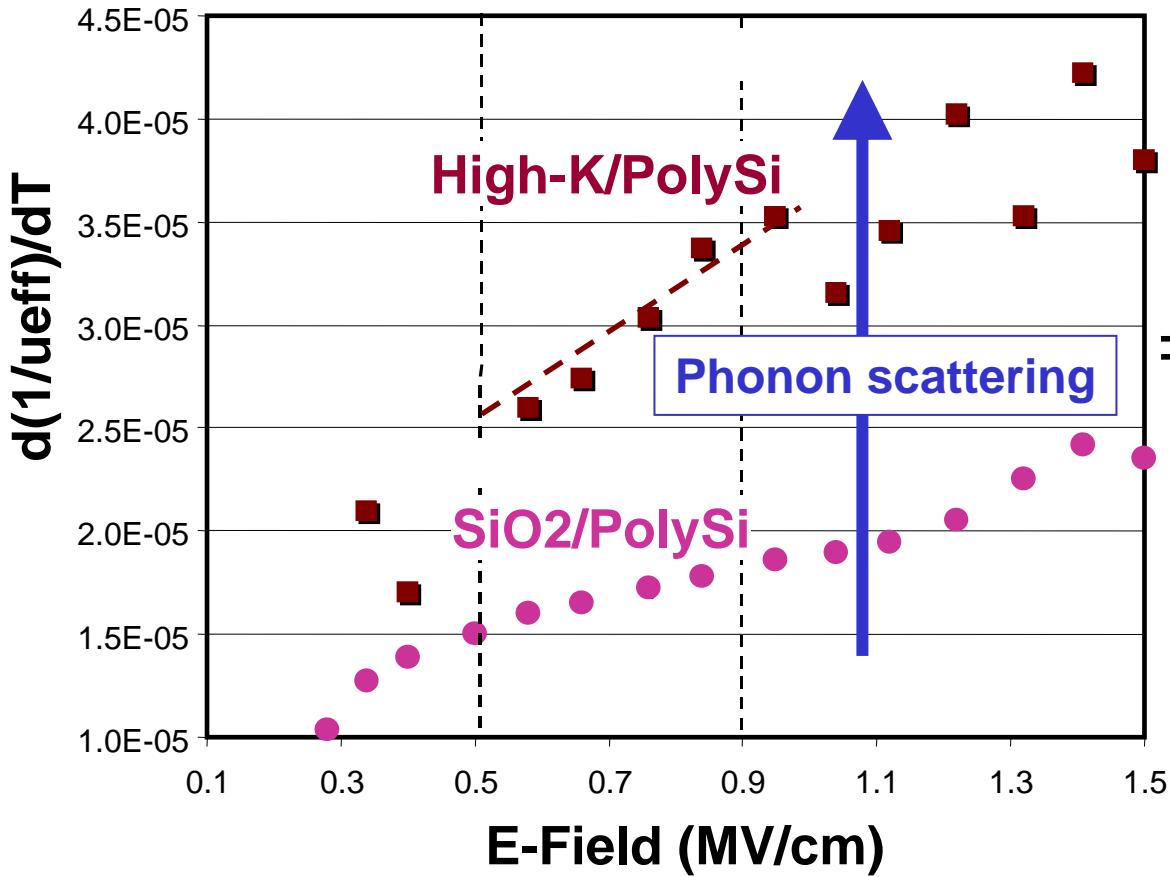

# Experimental Evidence of Phonon Scattering in High-K/PolySi Gate

$$\frac{1}{\mu_{eff}} = \frac{1}{\mu_{Coul}} + \frac{1}{\mu_{ph}} + \frac{1}{\mu_{SR}}$$

# Review on High-K Problems (High-K/Metal-Gate)

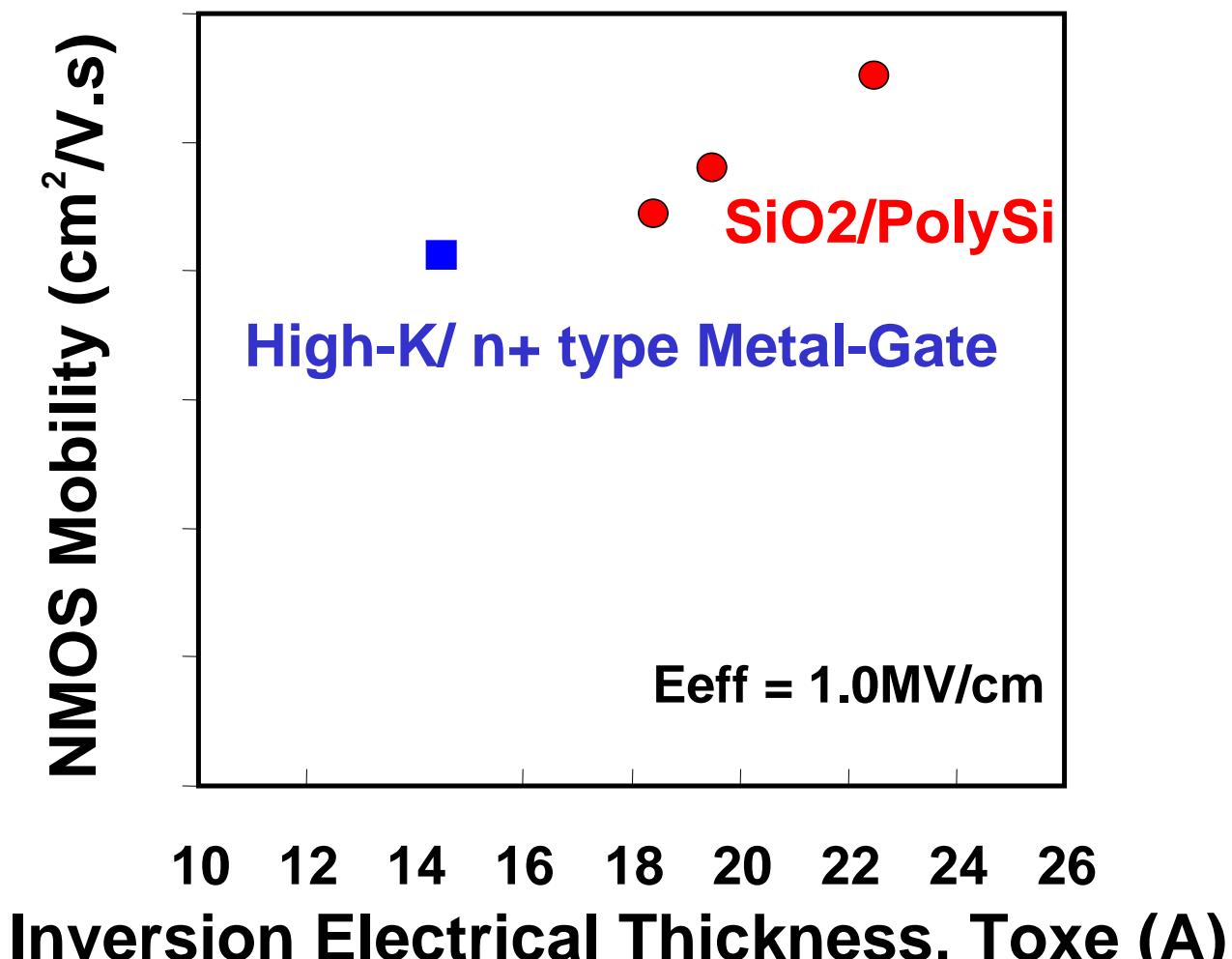

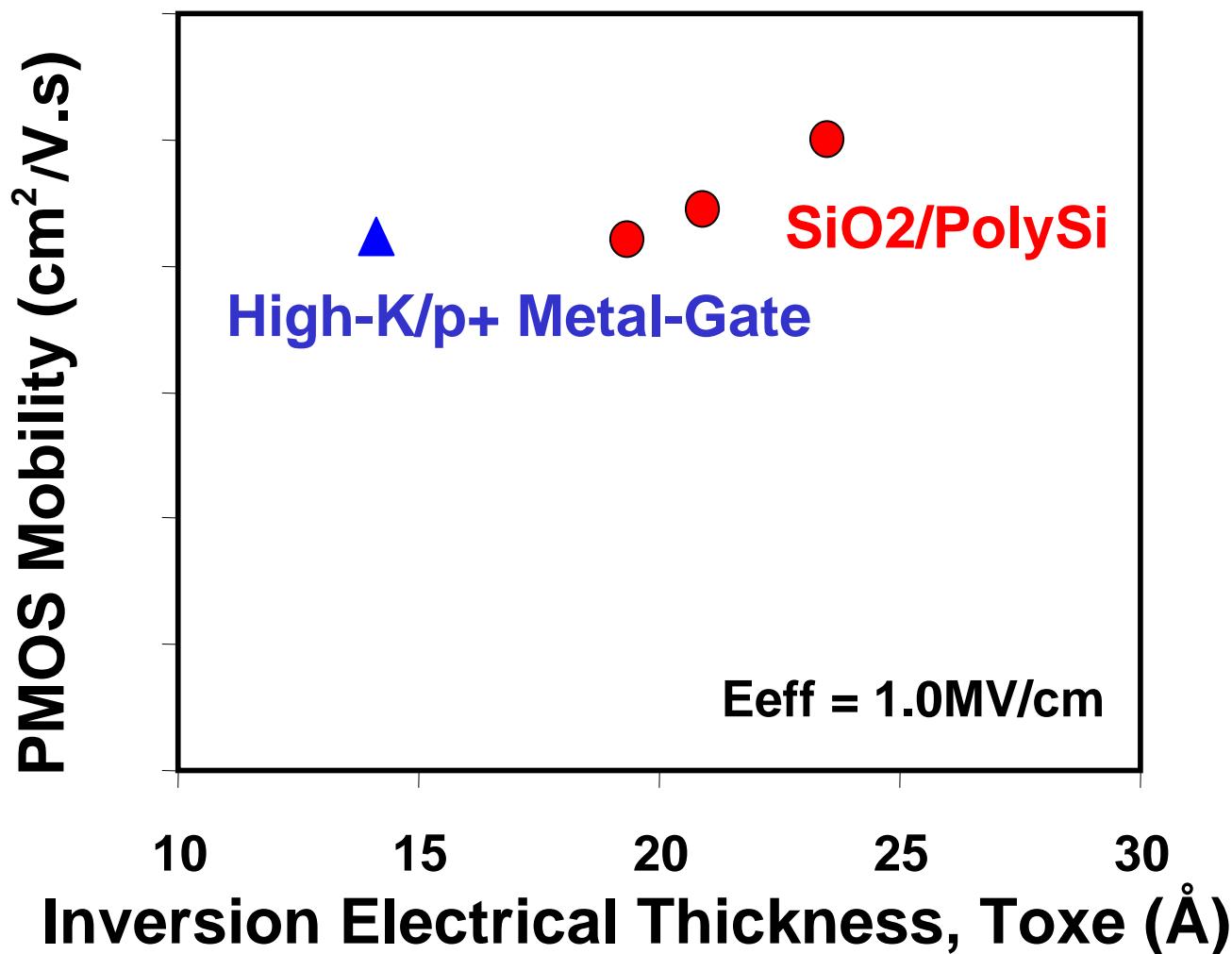

- Metal gate electrodes are able to screen the high-K SO phonons from coupling to the inversion channel charge carriers and reduce the mobility degradation problem

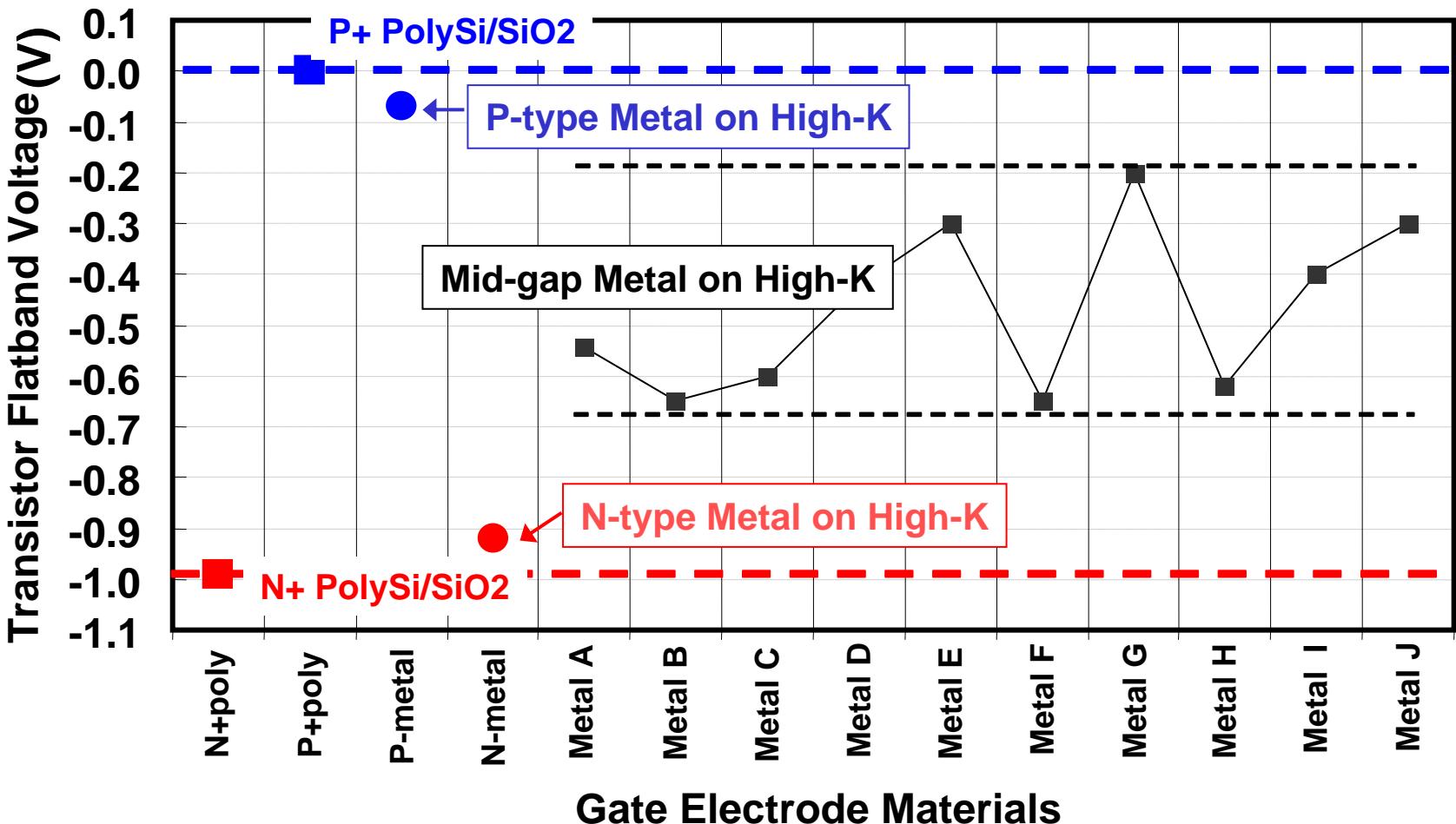

- However the use of high-K/metal-gate requires metal gate electrodes with the “correct” work functions on high-K for both PMOS and NMOS transistors for high performance

# Significant Breakthroughs in High-K/Metal-Gate made by Intel

- N-type metal and P-type metal with the correct work functions on high-K have been engineered and demonstrated for high-performance CMOS

- High-K/metal-gate stack achieves NMOS and PMOS channel mobility close to SiO<sub>2</sub>'s

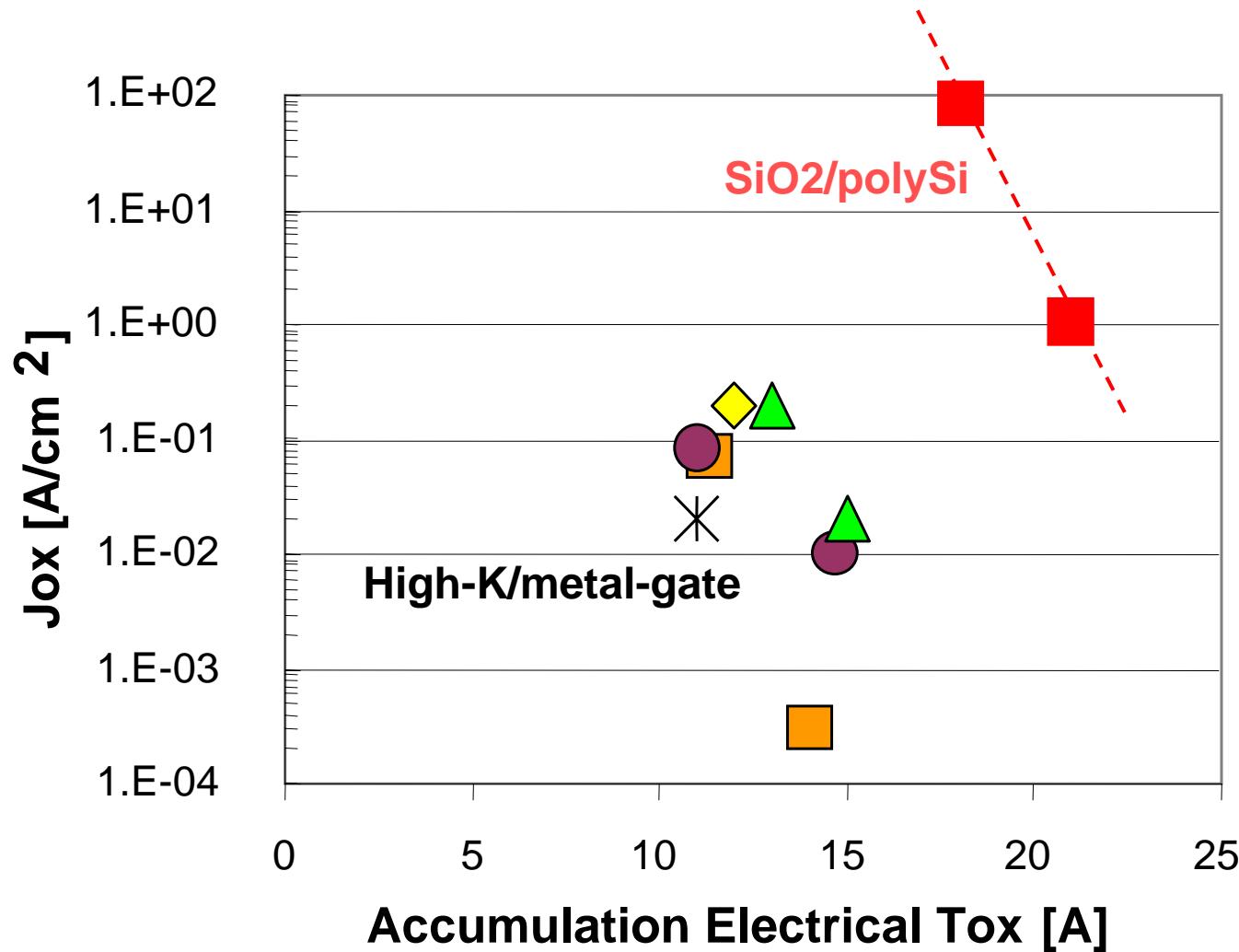

- High-K/metal-gate stack shows significantly lower gate leakage than SiO<sub>2</sub>

# We have Engineered N-type and P-type Metal Electrodes on High-K with the “Correct” Work Functions for NMOS and PMOS on Bulk Si

# High-K/n-type Metal-Gate Stack Achieves NMOS Channel Mobility Close to SiO<sub>2</sub>

# High-K/p-type Metal-Gate Stack Achieves PMOS Channel Mobility Close to SiO<sub>2</sub>

# High-K Reduces Gate Leakage

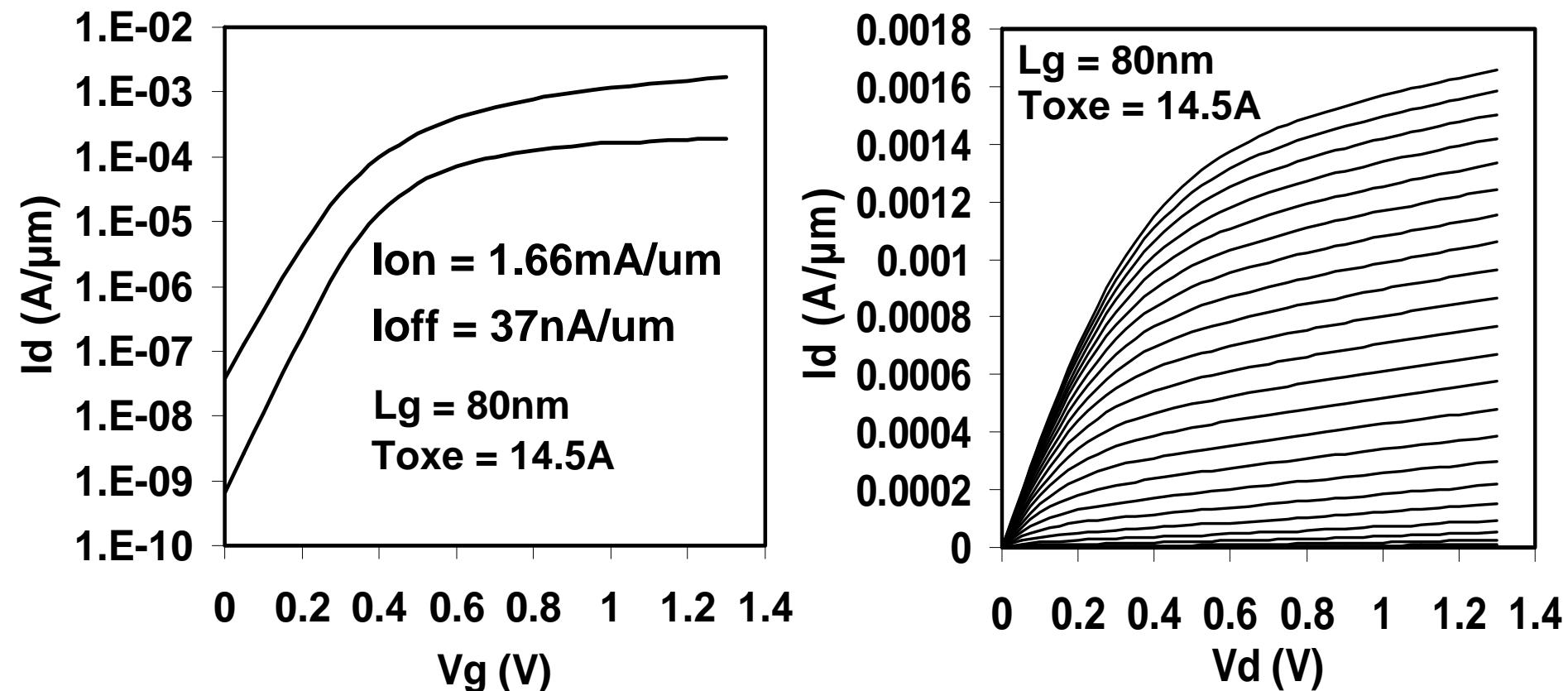

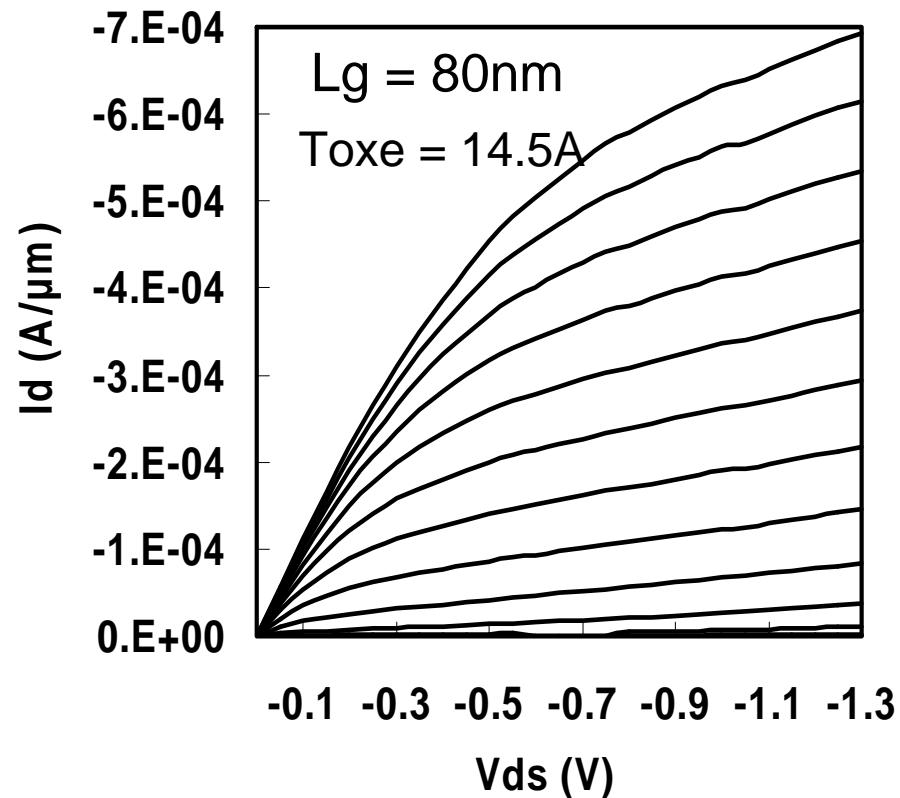

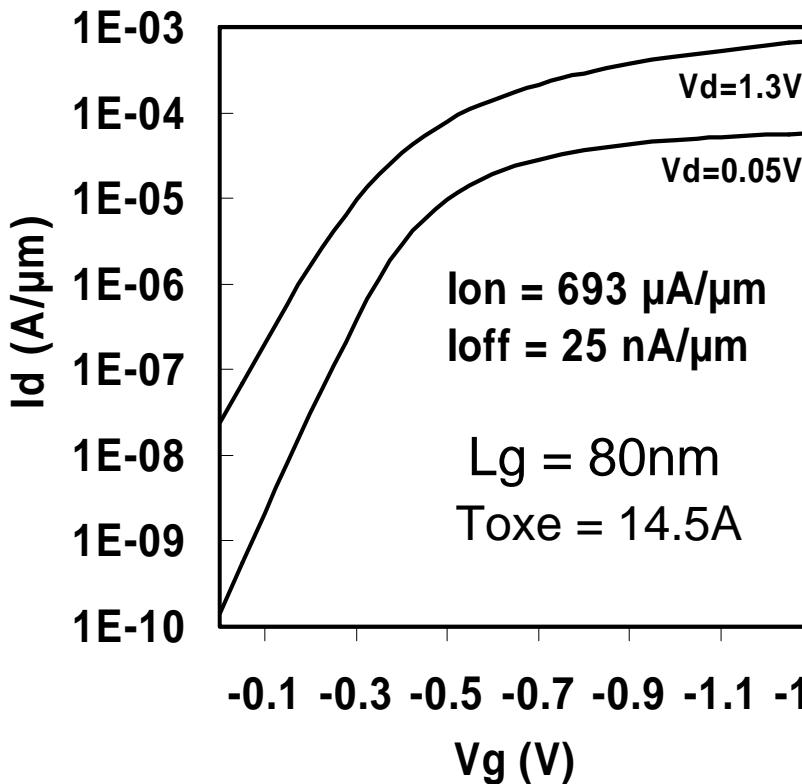

# High-K/Metal-gate NMOS and PMOS Transistors with Record-Setting Drive Current (Idsat) Performance

- NMOS and PMOS high-K/metal-gate transistors were made on bulk Si

- Physical gate length ( $L_g$ ) = 80nm

- Electrical Oxide Thickness @ inversion ( $Toxe$ ) = 1.45nm

- Record-setting NMOS Idsat

- $Idsat = 1.66\text{mA}/\text{um}$ ,  $Ioff = 37\text{nA}/\text{um}$  at  $Vcc = 1.3\text{V}$

- Record-setting PMOS Idsat

- $Idsat = 0.69\text{mA}/\text{um}$ ,  $Ioff = 25\text{nA}/\text{um}$  at  $Vcc = 1.3\text{V}$

# High-K/Metal-Gate NMOS with Record-Setting Drive Current Performance

- Electrical  $Tox$  at Inversion ( $Toxe$ ) =  $1.45\text{nm}$

- Transistor physical gate length ( $L_g$ ) =  $80\text{nm}$

# High-K/Metal-Gate PMOS with Record-Setting Drive Current Performance

- Electrical Tox at Inversion ( $Toxe$ ) = 1.45nm

- Transistor physical gate length ( $L_g$ ) = 80nm

# Summary

- We have implemented 1.2nm physical SiO<sub>2</sub> in our 90nm logic technology node and products, and have demonstrated 0.8nm physical SiO<sub>2</sub>

- We have engineered and demonstrated NMOS and PMOS high-K/metal-gate stacks on bulk Si with i) the correct work functions, ii) channel mobility close to SiO<sub>2</sub>'s and iii) very low gate leakage

- We have fabricated high-K/metal-gate NMOS and PMOS transistors on bulk Si with record-setting drive current performance

- We believe high-K/metal-gate is a key technology option for the 45nm logic technology node, to be in production in 2007