# Intel® 4 Series Chipset

## Thermal and Mechanical Design Guidelines

*September 2008*

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

This document contains information on products in the design phase of development.

All products, platforms, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. All dates specified are target dates, are provided for planning purposes only and are subject to change.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

Code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

Intel, Intel, Pentium, Intel Core, and the Intel logo and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All rights reserved.

# Contents

---

|            |                                                                           |    |

|------------|---------------------------------------------------------------------------|----|

| 1          | Introduction .....                                                        | 7  |

| 1.1        | Terminology .....                                                         | 8  |

| 1.2        | Reference Documents .....                                                 | 9  |

| 2          | Product Specifications.....                                               | 11 |

| 2.1        | Package Description.....                                                  | 11 |

| 2.1.1      | Non-Grid Array Package Ball Placement .....                               | 11 |

| 2.2        | Package Loading Specifications.....                                       | 12 |

| 2.3        | Thermal Specifications .....                                              | 12 |

| 2.3.1      | Thermal Design Power (TDP) .....                                          | 13 |

| 2.3.1.1    | Definition .....                                                          | 13 |

| 2.3.2      | TDP Prediction Methodology .....                                          | 13 |

| 2.3.2.1    | Pre-Silicon .....                                                         | 13 |

| 2.3.2.2    | Post-Silicon.....                                                         | 13 |

| 2.3.3      | Thermal Specifications .....                                              | 14 |

| 2.3.4      | $T_{CONTROL}$ Limit.....                                                  | 15 |

| 2.4        | Non-Critical to Function Solder Balls.....                                | 15 |

| 3          | Thermal Metrology .....                                                   | 17 |

| 3.1        | Case Temperature Measurements .....                                       | 17 |

| 3.1.1      | Thermocouple Attach Methodology.....                                      | 17 |

| 3.2        | Airflow Characterization .....                                            | 19 |

| 4          | Reference Thermal Solution.....                                           | 21 |

| 4.1        | Operating Environment .....                                               | 22 |

| 4.1.1      | ATX Form Factor Operating Environment .....                               | 23 |

| 4.1.2      | Balanced Technology Extended (BTX) Form Factor Operating Environment..... | 26 |

| 4.2        | Reference Design Mechanical Envelope .....                                | 27 |

| 4.3        | Thermal Solution Assembly.....                                            | 27 |

| 4.4        | Environmental Reliability Requirements .....                              | 29 |

| Appendix A | Enabled Suppliers .....                                                   | 31 |

| Appendix B | Mechanical Drawings .....                                                 | 33 |

## Figures

|                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1. (G)MCH Non-Grid Array.....                                                                                                   | 11 |

| Figure 2. Package Height .....                                                                                                         | 12 |

| Figure 3. Non-Critical to Function Solder Balls .....                                                                                  | 15 |

| Figure 4. 0° Angle Attach Methodology (top view, not to scale).....                                                                    | 18 |

| Figure 5. 0° Angle Attach Heatsink Modifications (generic heatsink side and bottom view shown, not to scale) .....                     | 18 |

| Figure 6. Airflow & Temperature Measurement Locations .....                                                                            | 19 |

| Figure 7. Cross-Cut Dimension Change of PWSHS Reference Design.....                                                                    | 22 |

| Figure 8. ATX Boundary Conditions.....                                                                                                 | 24 |

| Figure 9. Side View of ATX Boundary Conditions.....                                                                                    | 25 |

| Figure 10. Processor Heatsink Orientation to Provide Airflow to (G)MCH Heatsink on an ATX Platform.....                                | 25 |

| Figure 11. Processor Heatsink Orientation to Provide Airflow to (G)MCH Heatsink on a Balanced Technology Extended (BTX) Platform ..... | 27 |

| Figure 12. Design Concept for ATX (G)MCH Heatsink — Installed on Board.....                                                            | 28 |

| Figure 13. Design Concept for Balanced Technology Extended (BTX) (G)MCH Heatsink Design — Installed on Board .....                     | 28 |

| Figure 14. (G)MCH Package Drawing .....                                                                                                | 34 |

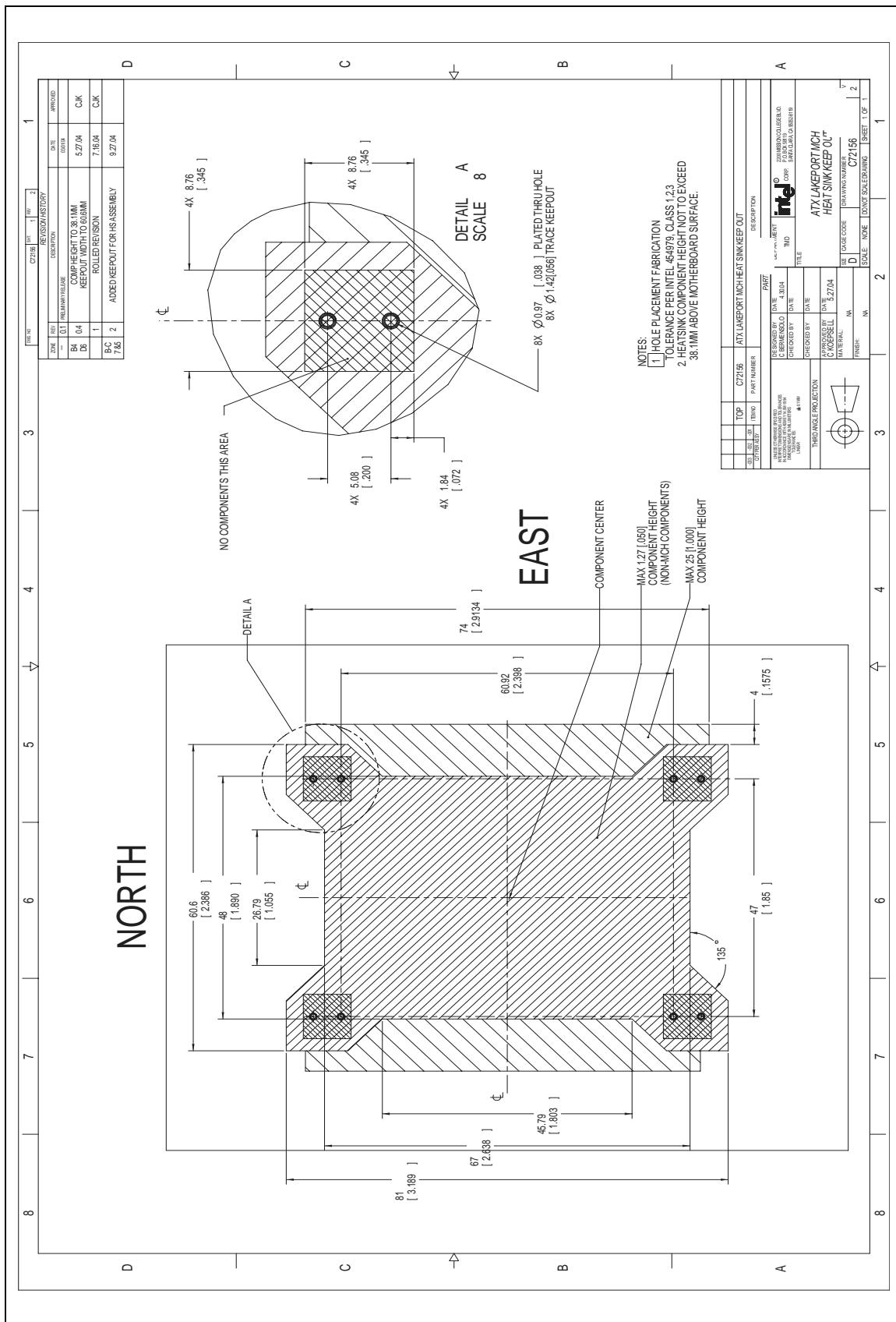

| Figure 15. (G)MCH Component Keep-Out Restrictions for ATX Platforms .....                                                              | 35 |

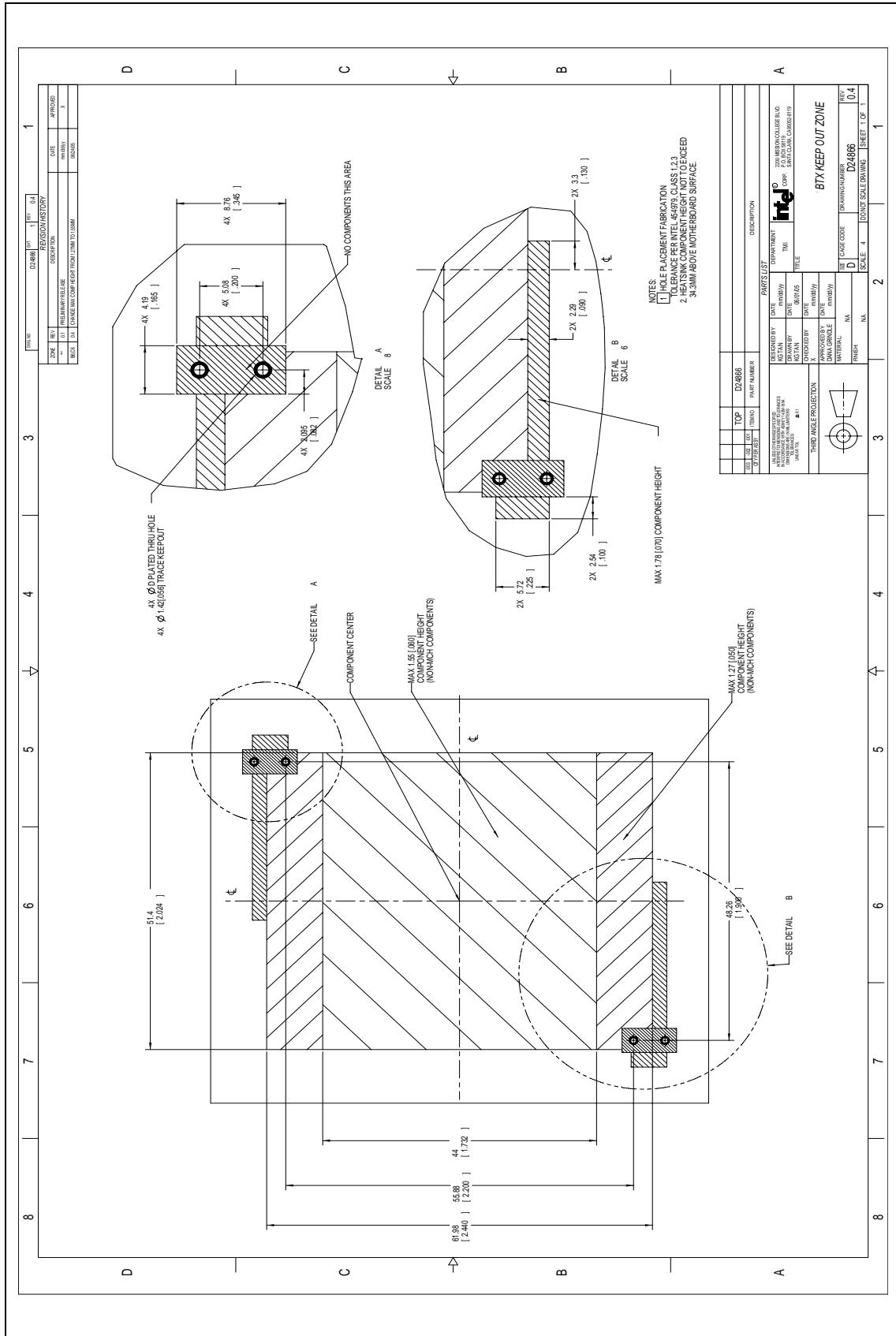

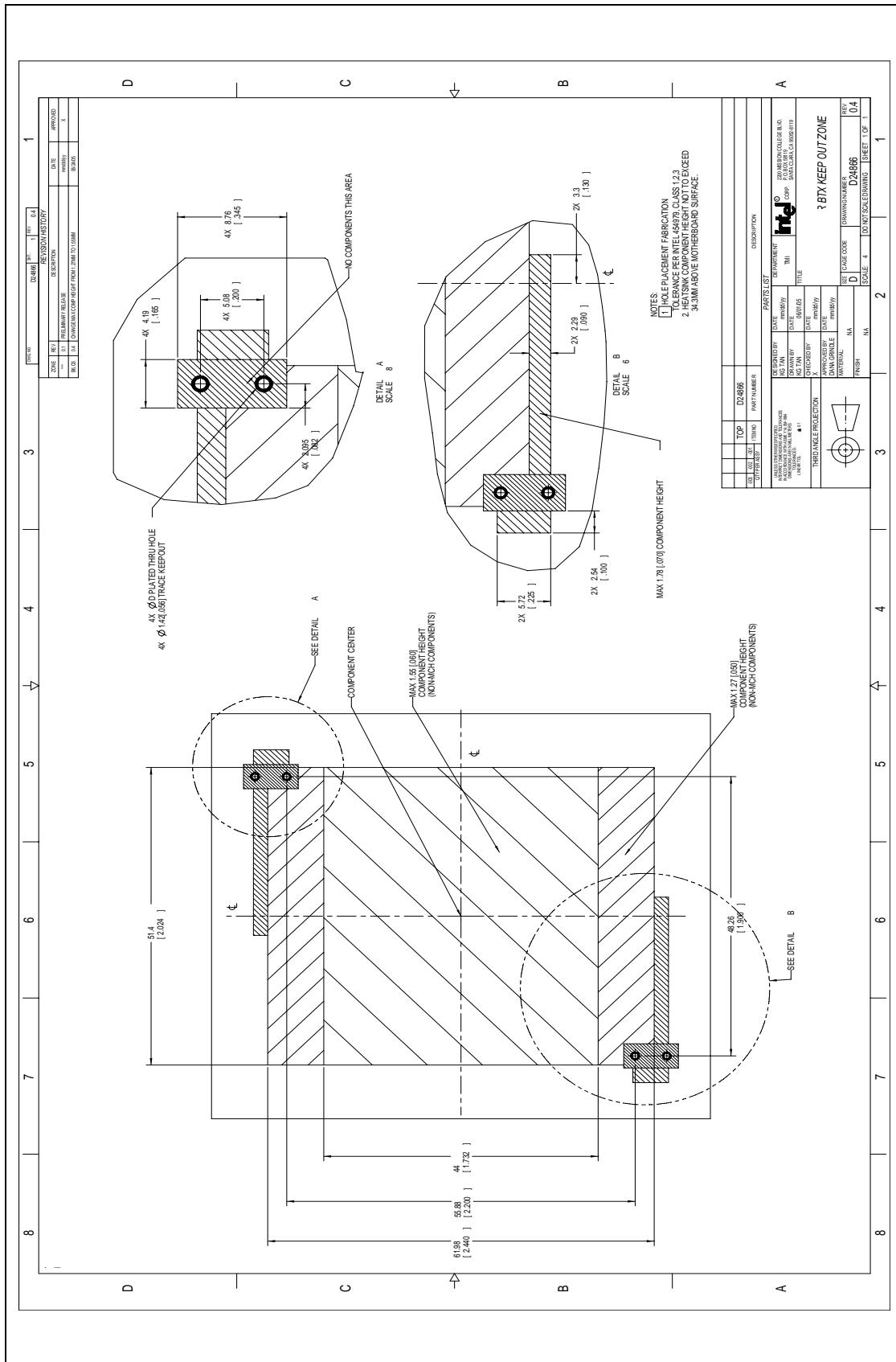

| Figure 16. (G)MCH Component Keep-Out Restrictions for Balanced Technology Extended (BTX) Platforms.....                                | 36 |

| Figure 17. (G)MCH Reference Heatsink for ATX Platforms – Sheet 1 .....                                                                 | 37 |

| Figure 18. (G)MCH Reference Heatsink for ATX Platforms – Sheet 2 .....                                                                 | 38 |

| Figure 19. (G)MCH Reference Heatsink for ATX Platforms – Anchor .....                                                                  | 39 |

| Figure 20. (G)MCH Reference Heatsink for ATX Platforms – Ramp Retainer Sheet 1 ..                                                      | 40 |

| Figure 21. (G)MCH Reference Heatsink for ATX Platforms – Ramp Retainer Sheet 2 ..                                                      | 41 |

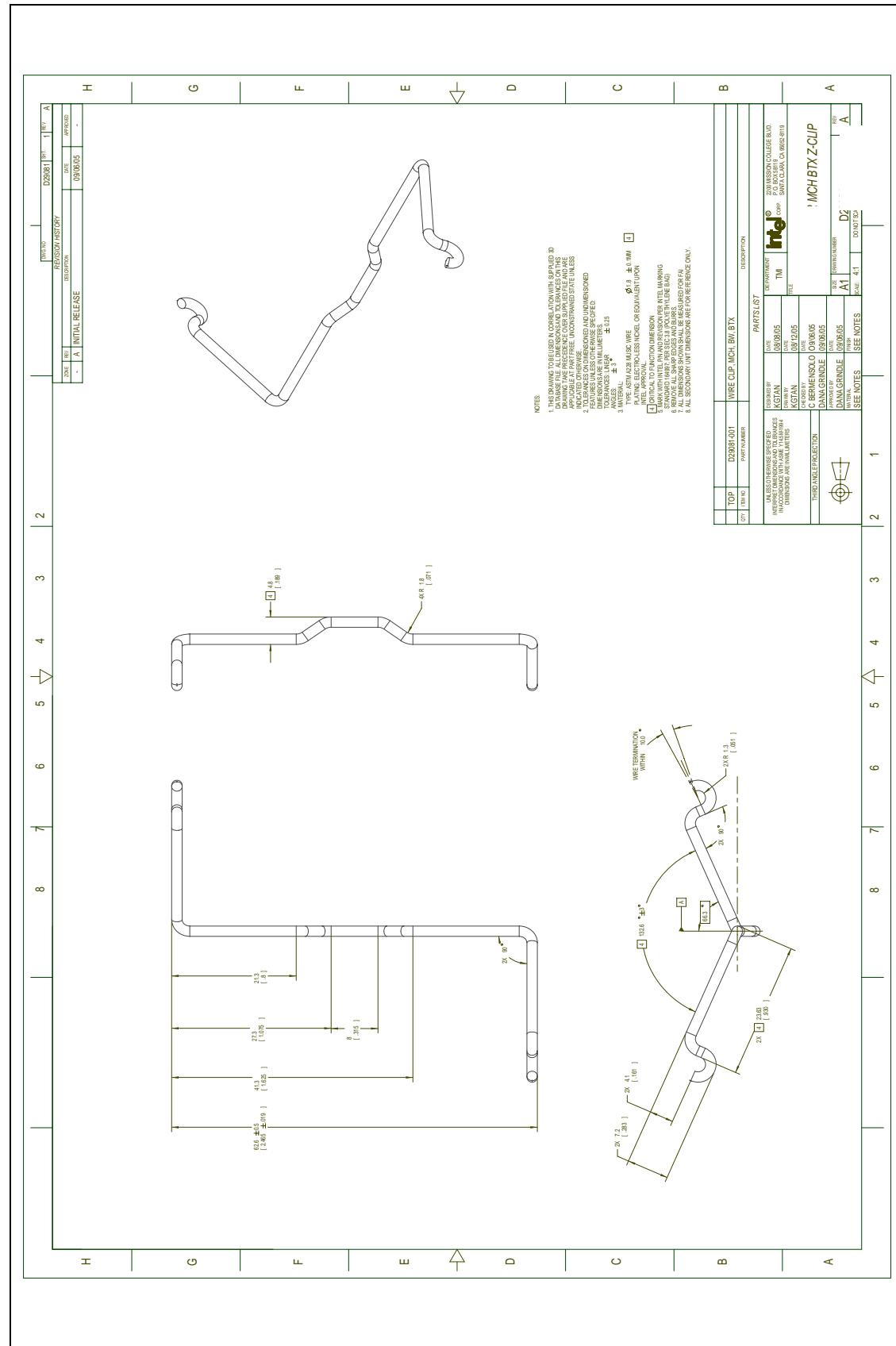

| Figure 22. (G)MCH Reference Heatsink for ATX Platforms – Wire Preload Clip .....                                                       | 42 |

| Figure 23. (G)MCH Reference Heatsink for Balanced Technology Extended (BTX) Platforms .....                                            | 43 |

| Figure 24. (G)MCH Chipsets Reference Heatsink for Balanced Technology Extended (BTX) Platforms – Clip .....                            | 44 |

## Tables

|                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1. Package Loading Specifications .....                                                                                      | 12 |

| Table 2. Thermal Specifications .....                                                                                              | 14 |

| Table 3. (G)MCH Heatsink Boundary Condition Summary in ATX Platforms .....                                                         | 23 |

| Table 4. (G)MCH Heatsink Boundary Condition Summary in BTX Platforms .....                                                         | 26 |

| Table 5. ATX Reference Thermal Solution Environmental Reliability Requirements (Board Level) .....                                 | 29 |

| Table 6. Balanced Technology Extended (BTX) Reference Thermal Solution Environmental Reliability Requirements (System Level) ..... | 30 |

| Table 7. ATX Intel Reference Heatsink Enabled Suppliers for (G)MCH .....                                                           | 31 |

| Table 8. BTX Intel Reference Heatsink Enabled Suppliers for (G)MCH .....                                                           | 31 |

| Table 9. Supplier Contact Information.....                                                                                         | 32 |

## Revision History

---

| Revision Number | Description                            | Date           |

|-----------------|----------------------------------------|----------------|

| -001            | Initial Release                        | June 2008      |

| -002            | Minor edits and formatting throughout. | June 2008      |

| -003            | Added Intel 82G41 GMCH                 | September 2008 |

| -004            | Added Intel 82Q43 GMCH and 82Q45 GMCH  | September 2008 |

§

# 1 Introduction

---

As the complexity of computer systems increases, so do power dissipation requirements. The additional power of next generation systems must be properly dissipated. Heat can be dissipated using improved system cooling, selective use of ducting, and/or passive heatsinks.

The objective of thermal management is to ensure that the temperatures of all components in a system are maintained within functional limits. The functional temperature limit is the range within which the electrical circuits can be expected to meet specified performance requirements. Operation outside the functional limit can degrade system performance, cause logic errors, or cause component and/or system damage. Temperatures exceeding the maximum operating limits may result in irreversible changes in the operating characteristics of the component.

This document is for the following devices:

- Intel® P45 Chipset MCH (82P45 MCH)

- Intel® P43 Chipset MCH (82P43 MCH)

- Intel® G45 Chipset GMCH (82G45 GMCH)

- Intel® G43 Chipset GMCH (82G43 GMCH)

- Intel® G41 Chipset GMCH (82G41 GMCH)

- Intel® Q45 Chipset GMCH (82Q45 GMCH)

- Intel® Q43 Chipset GMCH (82Q43 GMCH)

This document presents the conditions and requirements to properly design a cooling solution for systems that implement the (G)MCH. Properly designed solutions provide adequate cooling to maintain the (G)MCH case temperature at or below thermal specifications. This is accomplished by providing a low local-ambient temperature, ensuring adequate local airflow, and minimizing the case to local-ambient thermal resistance. By maintaining the (G)MCH case temperature at or below those recommended in this document, a system designer can ensure the proper functionality, performance, and reliability of this component.

**Note:** Unless otherwise specified the information in this document applies to all configurations of Intel® P45, P43, Q45, Q43, G45, G43, and G41 Chipsets. The Intel® Q45, Q43, G45, G43, and G41 Chipsets are available with integrated graphics and associated SDVO and digital display ports. In this document the integrated graphics version is referred to as GMCH. In addition a version will be offered using discrete graphics and is referred to as the MCH. The term (G)MCH will be used to when referring to all configurations.

**Note:** In this document the Intel P45, P43, Q45, Q43, G45, and G43 Chipsets refer to the combination of the (G)MCH and the Intel® ICH10. For ICH10 thermal details, refer to the *Intel® I/O Controller Hub 10 (ICH10) Thermal Design Guidelines*. The Intel G41 Chipset refers to the combination of the GMCH and Intel ICH7. For ICH7 details, refer to the *Intel® I/O Controller Hub 7 (ICH7) Thermal Design Guidelines*.

## 1.1 Terminology

| Term         | Description                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FC-BGA       | Flip Chip Ball Grid Array. A package type defined by a plastic substrate where a die is mounted using an underfill C4 (Controlled Collapse Chip Connection) attach style. The primary electrical interface is an array of solder balls attached to the substrate opposite the die. Note that the device arrives at the customer with solder balls attached. |

| Intel® ICH7  | Intel® I/O Controller Hub 7. The chipset component that contains the primary PCI interface, LPC interface, USB2, SATA, and/or other legacy functions.                                                                                                                                                                                                       |

| Intel® ICH10 | Intel® I/O Controller Hub 10. The chipset component that contains the primary PCI interface, LPC interface, HDA interface, USB2, SATA, and/or other legacy functions.                                                                                                                                                                                       |

| GMCH         | Graphic Memory Controller Hub. The chipset component that contains the processor and memory interface and integrated graphics core.                                                                                                                                                                                                                         |

| $T_A$        | The local ambient air temperature at the component of interest. The ambient temperature should be measured just upstream of airflow for a passive heatsink or at the fan inlet for an active heatsink.                                                                                                                                                      |

| $T_C$        | The case temperature of the (G)MCH component. The measurement is made at the geometric center of the die.                                                                                                                                                                                                                                                   |

| $T_{C-MAX}$  | The maximum value of $T_C$ .                                                                                                                                                                                                                                                                                                                                |

| $T_{C-MIN}$  | The minimum value of $T_C$ .                                                                                                                                                                                                                                                                                                                                |

| $TDP$        | Thermal Design Power is specified as the maximum sustainable power to be dissipated by the (G)MCH. This is based on extrapolations in both hardware and software technology. Thermal solutions should be designed to TDP.                                                                                                                                   |

| $TIM$        | Thermal Interface Material: thermally conductive material installed between two surfaces to improve heat transfer and reduce interface contact resistance.                                                                                                                                                                                                  |

| $\Psi_{CA}$  | Case-to-ambient thermal solution characterization parameter (Psi). A measure of thermal solution performance using total package power. Defined as $(T_C - T_A) / \text{Total Package Power}$ . Heat source size should always be specified for $\Psi$ measurements.                                                                                        |

## 1.2 Reference Documents

| Document                                                                                                                                                                                    | Location                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <i>Intel® 4 Series Chipset Family Datasheet</i>                                                                                                                                             | <a href="http://www.intel.com/assets/pdf/datasheet/319970.pdf">http://www.intel.com/assets/pdf/datasheet/319970.pdf</a>           |

| <i>Intel® I/O Controller Hub 7 (ICH7) Thermal Design Guidelines</i>                                                                                                                         | <a href="http://www.intel.com/assets/pdf/designguide/307015.pdf">http://www.intel.com/assets/pdf/designguide/307015.pdf</a>       |

| <i>Intel® I/O Controller Hub 10 (ICH10) Thermal Design Guidelines</i>                                                                                                                       | <a href="http://www.intel.com/assets/pdf/designguide/319975.pdf">http://www.intel.com/assets/pdf/designguide/319975.pdf</a>       |

| <i>Intel® Core™2 Duo Processor E8000<sup>4</sup> and E7000<sup>4</sup> Series and Intel® Pentium® Dual-Core Processor E5000<sup>4</sup> Series Thermal and Mechanical Design Guidelines</i> | <a href="http://www.intel.com/design/processor/designex/318734.pdf">http://www.intel.com/design/processor/designex/318734.pdf</a> |

| <i>Intel® Core™2 Extreme Quad-Core Processor and Intel® Core™2 Quad Processor Thermal and Mechanical Design Guidelines</i>                                                                  | <a href="http://www.intel.com/design/processor/designex/315594.htm">http://www.intel.com/design/processor/designex/315594.htm</a> |

| <i>Balanced Technology Extended (BTX) Interface Specification</i>                                                                                                                           | <a href="http://www.formfactors.org">http://www.formfactors.org</a>                                                               |

| <i>Various System Thermal and Mechanical Design Suggestions</i>                                                                                                                             | <a href="http://www.formfactors.org">http://www.formfactors.org</a>                                                               |

| <i>Various Chassis Thermal and Mechanical Design Suggestions</i>                                                                                                                            | <a href="http://www.formfactors.org">http://www.formfactors.org</a>                                                               |

§

## 2 Product Specifications

### 2.1 Package Description

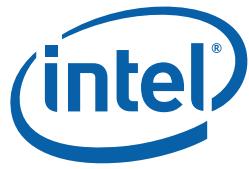

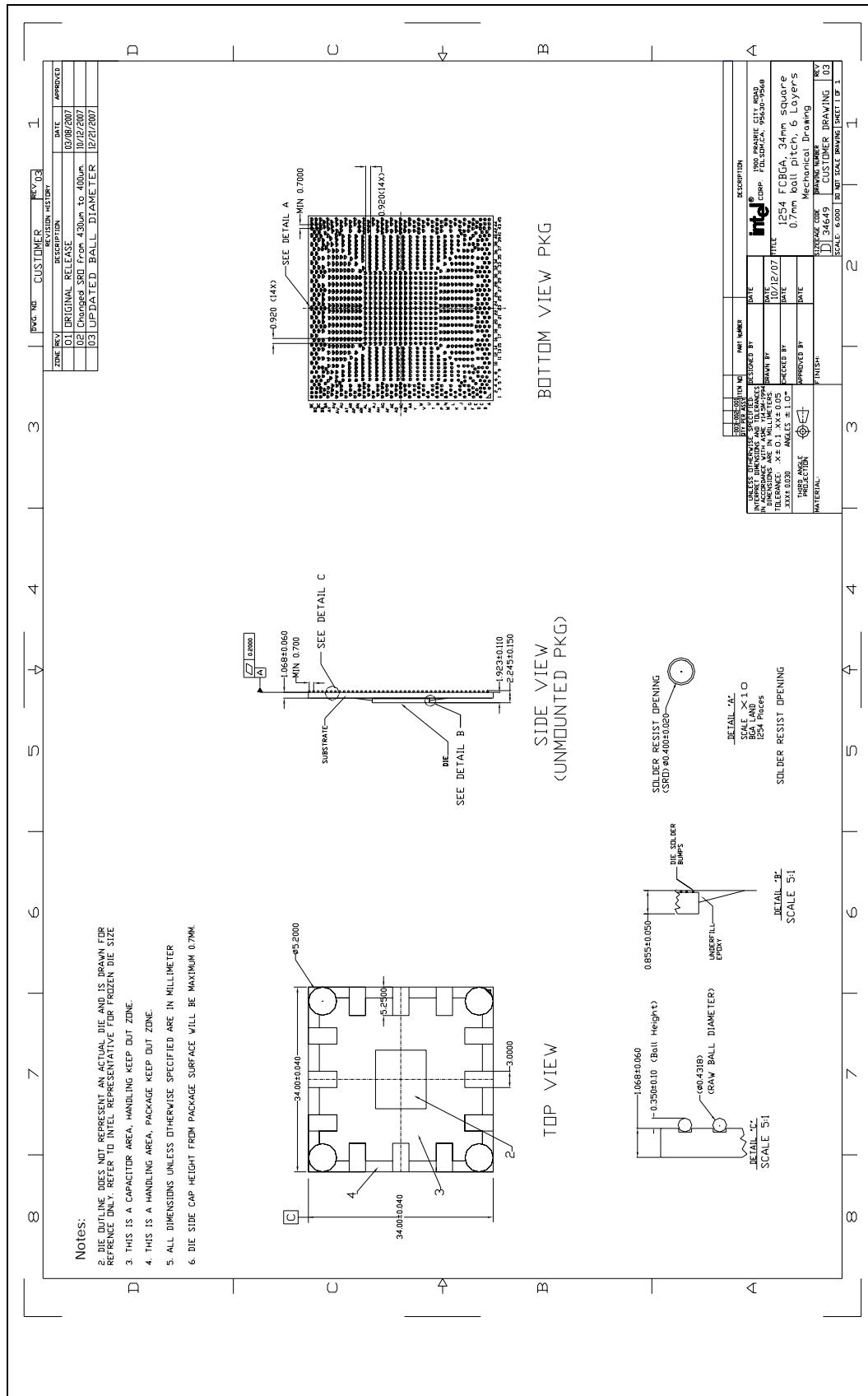

The (G)MCH is available in a 34 mm [1.34 in] x 34 mm [1.34 in] Flip Chip Ball Grid Array (FC-BGA) package with 1254 solder balls. The die size is currently 10.80 mm [0.425 in] x 9.06 mm [0.357 in] and is subject to change. A mechanical drawing of the package is shown in Figure 14, Appendix B.

#### 2.1.1 Non-Grid Array Package Ball Placement

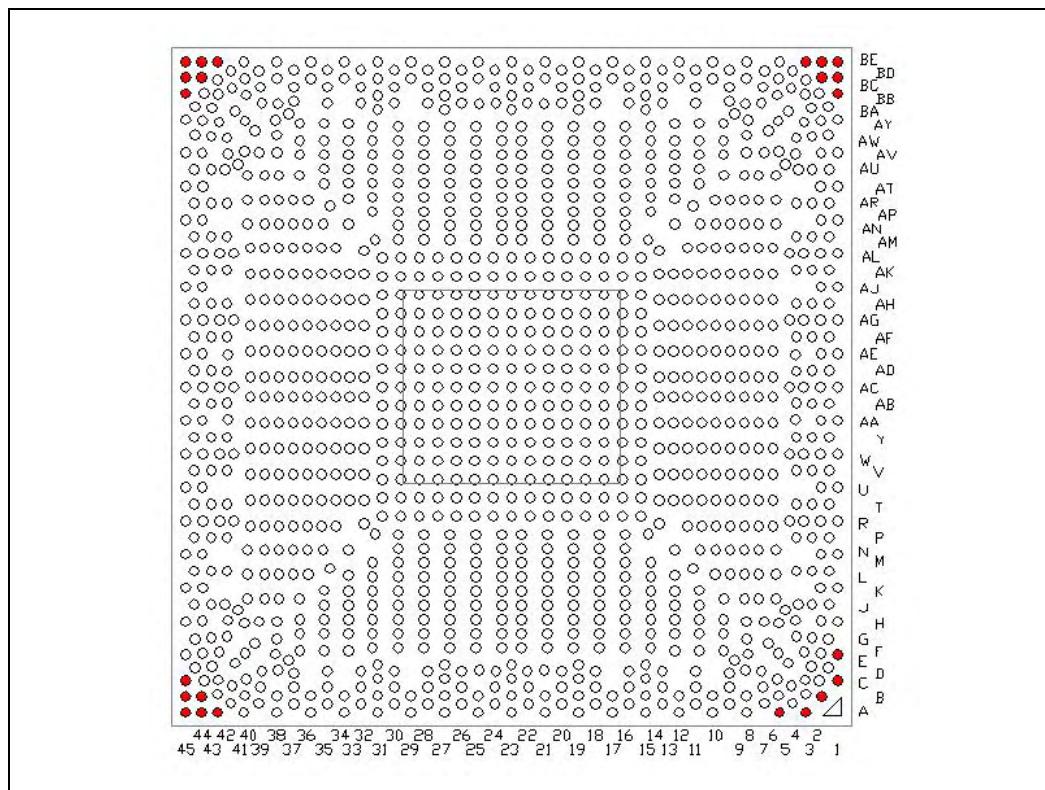

The (G)MCH package utilizes a “balls anywhere” concept. Minimum ball pitch is 0.7 mm [0.028 in], but ball ordering does not follow a 0.7 mm grid. Board designers should ensure correct ball placement when designing for the non-grid array pattern. For exact ball locations relative to the package, refer to the *Intel® 4 Series Chipset Family Datasheet*.

**Figure 1. (G)MCH Non-Grid Array**

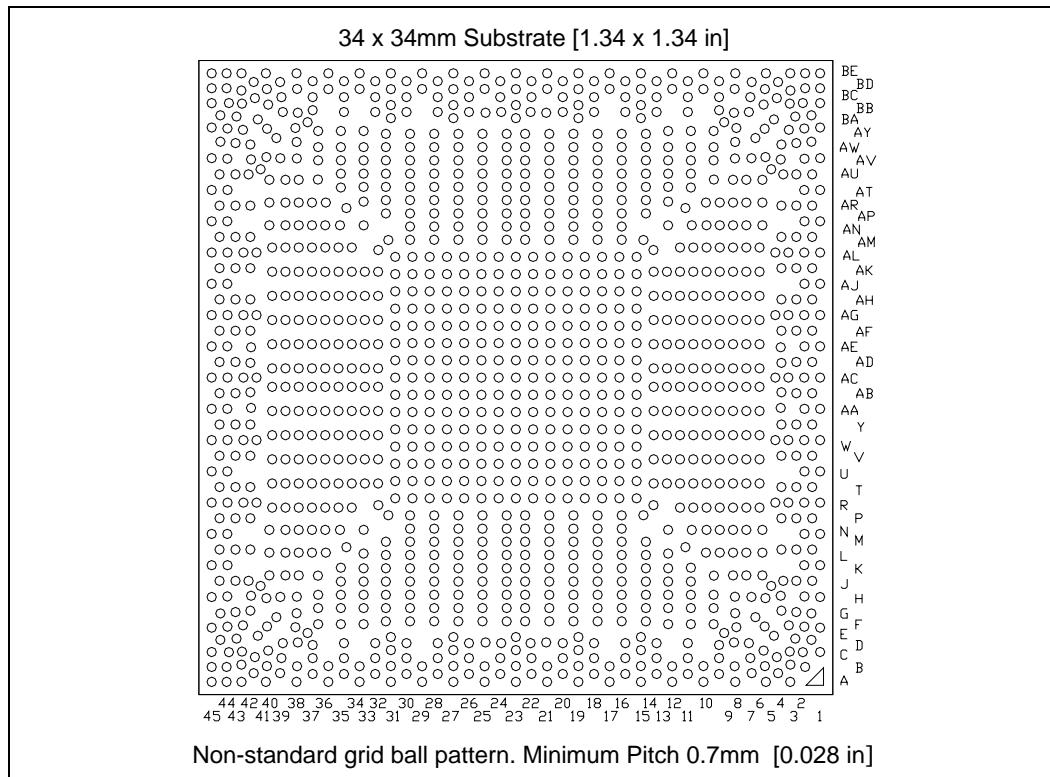

## 2.2 Package Loading Specifications

Table 1 provides static load specifications for the package. This mechanical maximum load limit should not be exceeded during heatsink assembly, shipping conditions, or standard use conditions. Also, any mechanical system or component testing should not exceed the maximum limit. The package substrate should not be used as a mechanical reference or load-bearing surface for the thermal and mechanical solution.

**Table 1. Package Loading Specifications**

| Parameter | Maximum | Notes |

|-----------|---------|-------|

| Static    | 15 lbf  | 1,2,3 |

**NOTES:**

1. These specifications apply to uniform compressive loading in a direction normal to the package.

2. This is the maximum force that can be applied by a heatsink retention clip. The clip must also provide the minimum specified load on the package.

3. These specifications are based on limited testing for design characterization. Loading limits are for the package only.

To ensure the package static load limit is not exceeded, the designer should understand the post reflow package height. The following figure shows the nominal post-reflow package height assumed for calculation of a heatsink clip preload of the reference design. Refer to the package drawing in Appendix B to perform a detailed analysis.

**Figure 2. Package Height**

## 2.3 Thermal Specifications

To ensure proper operation and reliability of the (G)MCH, the case temperature must be at or below the maximum value specified in Table 2. System and component level thermal enhancements are required to dissipate the heat generated and maintain the (G)MCH within specifications. Chapter 3 provides the thermal metrology guidelines for case temperature measurements.

## 2.3.1 Thermal Design Power (TDP)

### 2.3.1.1 Definition

Thermal design power (TDP) is the estimated power dissipation of the (G)MCH based on normal operating conditions including  $V_{CC}$  and  $T_{C-MAX}$  while executing real worst-case power intensive applications. This value is based on expected worst-case data traffic patterns and usage of the chipset and does not represent a specific software application. TDP attempts to account for expected increases in power due to variation in (G)MCH current consumption due to silicon process variation, processor speed, DRAM capacitive bus loading and temperature. However, since these variations are subject to change, there is no assurance that all applications will not exceed the TDP value.

The system designer must design a thermal solution for the (G)MCH such that it maintains  $T_C$  below  $T_{C-MAX}$  for a sustained power level equal to TDP. Note that the  $T_{C-MAX}$  specification is a requirement for a sustained power level equal to TDP, and that the case temperature must be maintained at temperatures less than  $T_{C-MAX}$  when operating at power levels less than TDP. This temperature compliance is to ensure component reliability. The TDP value can be used for thermal design if the thermal protection mechanisms are enabled. The (G)MCH incorporate a hardware-based fail-safe mechanism to keep the product temperature in spec in the event of unusually strenuous usage above the TDP power.

## 2.3.2 TDP Prediction Methodology

### 2.3.2.1 Pre-Silicon

To determine TDP for pre-silicon products in development, it is necessary to make estimates based on analytical models. These models rely on knowledge of the past (G)MCH power dissipation behavior along with knowledge of planned architectural and process changes that may affect TDP. Knowledge of applications available today and their ability to stress various aspects of the (G)MCH is also included in the model. The projection for TDP assumes (G)MCH operation at  $T_{C-MAX}$ . The TDP estimate also accounts for normal manufacturing process variation.

### 2.3.2.2 Post-Silicon

Once the product silicon is available, post-silicon validation is performed to assess the validity of pre-silicon projections. Testing is performed on both commercially available and synthetic high power applications and power data is compared to pre-silicon estimates. Post-silicon validation may result in a small adjustment to pre-silicon TDP estimates.

### 2.3.3 Thermal Specifications

The data in Table 2 is based on post-silicon power measurements for the (G)MCH. The TDP values are based on system configuration with two (2) DIMMs per channel, DDR3 (or DDR2) and the FSB operating at the top speed allowed by the chipset with a processor operating at that system bus speed. Intel recommends designing the (G)MCH thermal solution to the highest system bus speed and memory frequency for maximum flexibility and reuse. The (G)MCH packages have poor heat transfer capability into the board and have minimal thermal capability without thermal solutions. Intel requires that system designers plan for an attached heatsink when using the (G)MCH.

**Table 2. Thermal Specifications**

| Component                | Mem Type | Sys Bus Speed | Mem Freq  | Max Idle Power (C1/C2 Enabled) | Max Idle Power (C3/C4 Enabled) | TDP  | T <sub>C-MIN</sub> | T <sub>C-MAX</sub> | Notes   |

|--------------------------|----------|---------------|-----------|--------------------------------|--------------------------------|------|--------------------|--------------------|---------|

| Intel® G45 Chipset       | DDR3     | 1333 MT/s     | 1333 MT/s | 9 W                            | 7.7 W                          | 24 W | 0 °C               | 103 °C             | 1,2,3,4 |

| Intel® G43 Chipset       | DDR3     | 1333 MT/s     | 1067 MT/s | 9 W                            | 7.7 W                          | 24 W | 0 °C               | 103 °C             | 1,2,3,4 |

| Intel® G41 Chipset       | DDR3     | 1333 MT/s     | 1067 MT/s | 11.5 W                         | N/A                            | 25 W | 0 °C               | 102 °C             | 1,2,3   |

| Intel® Q45 / Q43 Chipset | DDR3     | 1333 MT/s     | 1067 MT/s | 6W                             | 4.7 W                          | 17 W | 0 °C               | 105 °C             | 1,2,3   |

| Intel® Q45 / Q43 Chipset | DDR2     | 1333 MT/s     | 800 MT/s  | 6W                             | 4.7 W                          | 17 W | 0 °C               | 105 °C             | 1,2,3   |

| Intel® Q43 Chipset       | DDR3     | 1333 MT/s     | 1067 MT/s | 5W                             | 3.8 W                          | 13 W | 0 °C               | 105 °C             | 1,2,3,5 |

| Intel® P45 Chipset       | DDR3     | 1333 MT/s     | 1333 MT/s | 9 W                            | 7.5 W                          | 22 W | 0 °C               | 103 °C             | 1,2,3,6 |

| Intel® P43 Chipset       | DDR3     | 1333 MT/s     | 1067 MT/s | 9 W                            | 7.5 W                          | 22 W | 0 °C               | 103 °C             | 1,2,3,6 |

**NOTES:**

1. Thermal specifications assume an attached heatsink is present.

2. Max Idle power is the worst case idle power in the system booted to Windows\* with no background applications running.

3. Intel® P45, P43, G45, G43, Q45, and Q43 Chipset TDP is measured with DDR3 (or DDR2) with 2 channels, 2 DIMMs per channel and Max Idle power is measured with DDR3 (or DDR2) with 2 channels, 1 DIMM per channel. Intel® G41 Chipset TDP and Max Idle power are measured with DDR3 with 2 channels, 1 DIMM per channel.

4. When an external graphic card is installed in a system with the Intel® G45, G43 Chipsets, the TDP for these parts will drop to approximately 22 W. The GMCH will detect the presence of the graphics card and disable the on-board graphics resulting in the lower TDP for these components.

5. The Idle and TDP numbers are assuming Internal Graphics is disabled on the Intel Q43 Chipset.

6. Idle data is measured on Intel P45, P43 Chipset when an external graphics card is installed in a system wherein this card must support L0s /L1 ASPM.

### 2.3.4 $T_{CONTROL}$ Limit

Intel® Quiet System Technology (Intel® QST) can monitor an embedded thermal sensor. The maximum operating limit when monitoring this thermal sensor is  $T_{CONTROL}$ . For the (G)MCH this value is 99° C. This value should be programmed into the appropriate register of Intel® QST, as the maximum sensor temperature for operation of the (G)MCH.

## 2.4 Non-Critical to Function Solder Balls

Intel has defined selected solder joints of the (G)MCH as non-critical to function (NCTF) when evaluating package solder joints post environmental testing. The (G)MCH signals at NCTF locations are typically redundant ground or non-critical reserved, so the loss of the solder joint continuity at end of life conditions will not affect the overall product functionality. Figure 3 identifies the NCTF solder joints of the (G)MCH package.

**Figure 3. Non-Critical to Function Solder Balls**

S

## 3 Thermal Metrology

---

The system designer must measure temperatures in order to accurately determine the thermal performance of the system. Intel has established guidelines for proper techniques of measuring (G)MCH component case temperatures.

### 3.1 Case Temperature Measurements

To ensure functionality and reliability of the (G)MCH the  $T_C$  must be maintained at or below the maximum temperature listed in Table 2. The surface temperature measured at the geometric center of the die corresponds to  $T_C$ . Measuring  $T_C$  requires special care to ensure an accurate temperature reading.

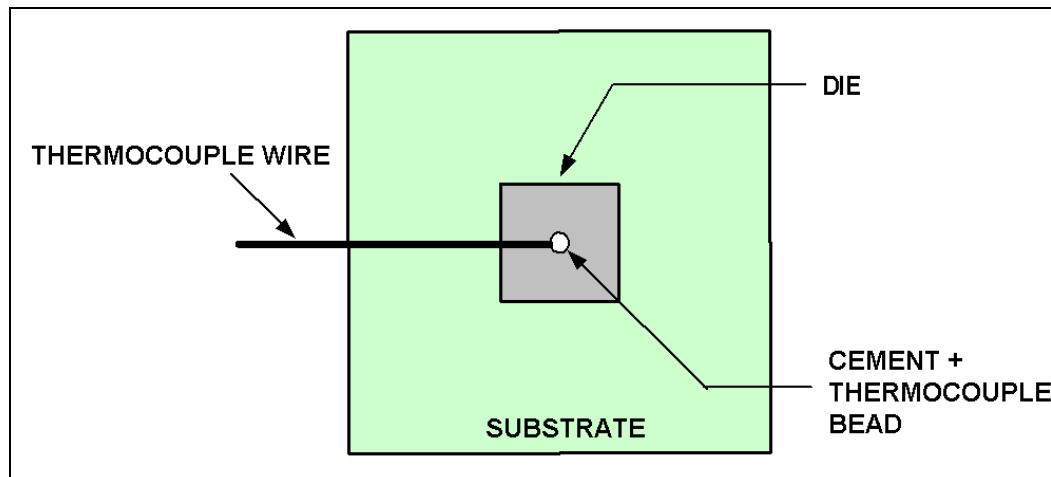

Temperature differences between the temperature of a surface and the surrounding local ambient air can introduce error in the measurements. The measurement errors could be due to a poor thermal contact between the thermocouple bead and the surface of the package, heat loss by radiation and/or convection, conduction through thermocouple leads, or contact between the thermocouple cement and the heatsink base (if a heatsink is used). To minimize these measurement errors a thermocouple attach with a zero-degree methodology is recommended.

#### 3.1.1 Thermocouple Attach Methodology

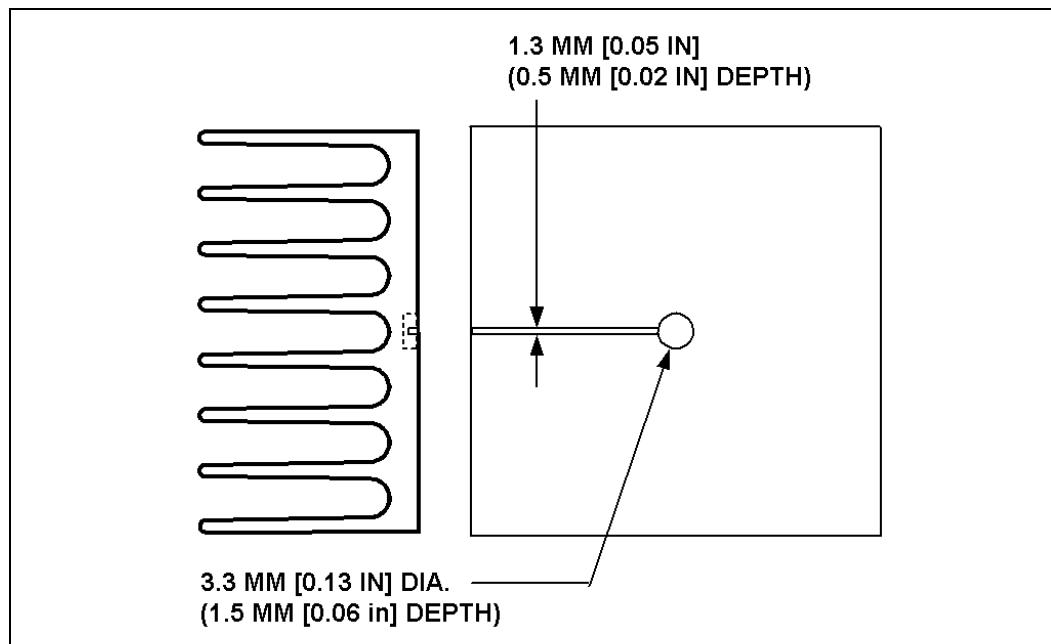

1. Mill a 3.3 mm [0.13 in] diameter hole centered on bottom of the heatsink base. The milled hole should be approximately 1.5 mm [0.06 in] deep.

2. Mill a 1.3 mm [0.05 in] wide slot, 0.5 mm [0.02 in] deep, from the centered hole to one edge of the heatsink. The slot should be in the direction parallel to the heatsink fins (see Figure 5).

3. Attach thermal interface material (TIM) to the bottom of the heatsink base.

4. Cut out portions of the TIM to make room for the thermocouple wire and bead. The cutouts should match the slot and hole milled into the heatsink base.

5. Attach a 36 gauge or smaller K-type thermocouple bead to the center of the top surface of the die using a cement with high thermal conductivity. During this step, make sure no contact is present between the thermocouple cement and the heatsink base because any contact will affect the thermocouple reading. **It is critical that the thermocouple bead makes contact with the die** (see Figure 4).

6. Attach heatsink assembly to the (G)MCH, and route thermocouple wires out through the milled slot.

Figure 4. 0° Angle Attach Methodology (top view, not to scale)

Figure 5. 0° Angle Attach Heatsink Modifications (generic heatsink side and bottom view shown, not to scale)

## 3.2 Airflow Characterization

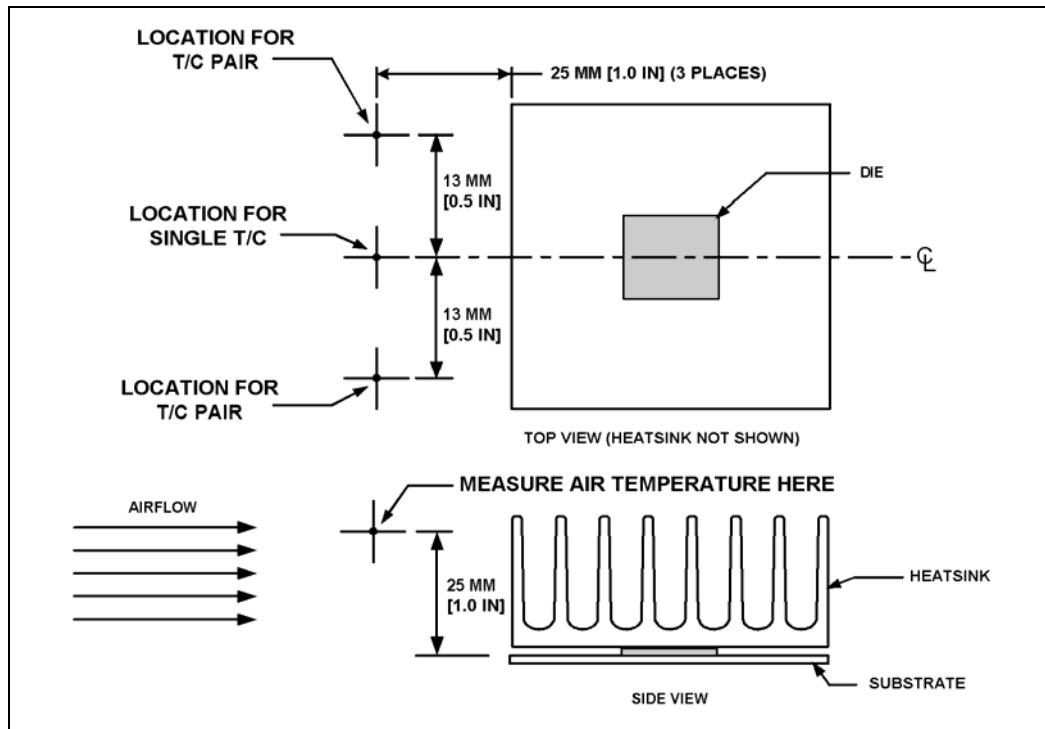

Figure 6 describes the recommended location for air temperature measurements measured relative to the component. For a more accurate measurement of the average approach air temperature, Intel recommends averaging temperatures recorded from two thermocouples spaced about 25 mm [1.0 in] apart. Locations for both a single thermocouple and a pair of thermocouples are presented.

**Figure 6. Airflow & Temperature Measurement Locations**

Airflow velocity can be measured using sensors that combine air velocity and temperature measurements. Typical airflow sensor technology may include hot wire anemometers. Figure 6 provides guidance for airflow velocity measurement locations which should be the same as used for temperature measurement. These locations are for a typical JEDEC test setup and may not be compatible with chassis layouts due to the proximity of the processor to the (G)MCH. The user may have to adjust the locations for a specific chassis. Be aware that sensors may need to be aligned perpendicular to the airflow velocity vector or an inaccurate measurement may result. Measurements should be taken with the chassis fully sealed in its operational configuration to achieve a representative airflow profile within the chassis.

§

## 4

## Reference Thermal Solution

---

The design strategy for the reference thermal solution for the (G)MCH for use in ATX platforms reuses the Intel® 3 Series Chipsets reference thermal solution, Preload Wave Solder Heatsink (PWSHS), see Figure 18 and Figure 19. The ramp retainer, MB anchors and the thermal interface material remains the same to meet the (G)MCH thermal/mechanical requirements. The keep out zone remains the same as used with the Intel 3 Series Chipsets, see Figure 15.

The (G)MCH maximum TDP has been updated in Table 2. The TDP reduction may allow system designers to lower thermal solution cost for McCreary and Boulder Creek platforms. The reference design for the (G)MCH is a PWSHS which provides adequate solder joint protection but may exceed thermal performance requirements in most systems. Customers may save costs by reducing the heatsink size to meet the lowered TDP.

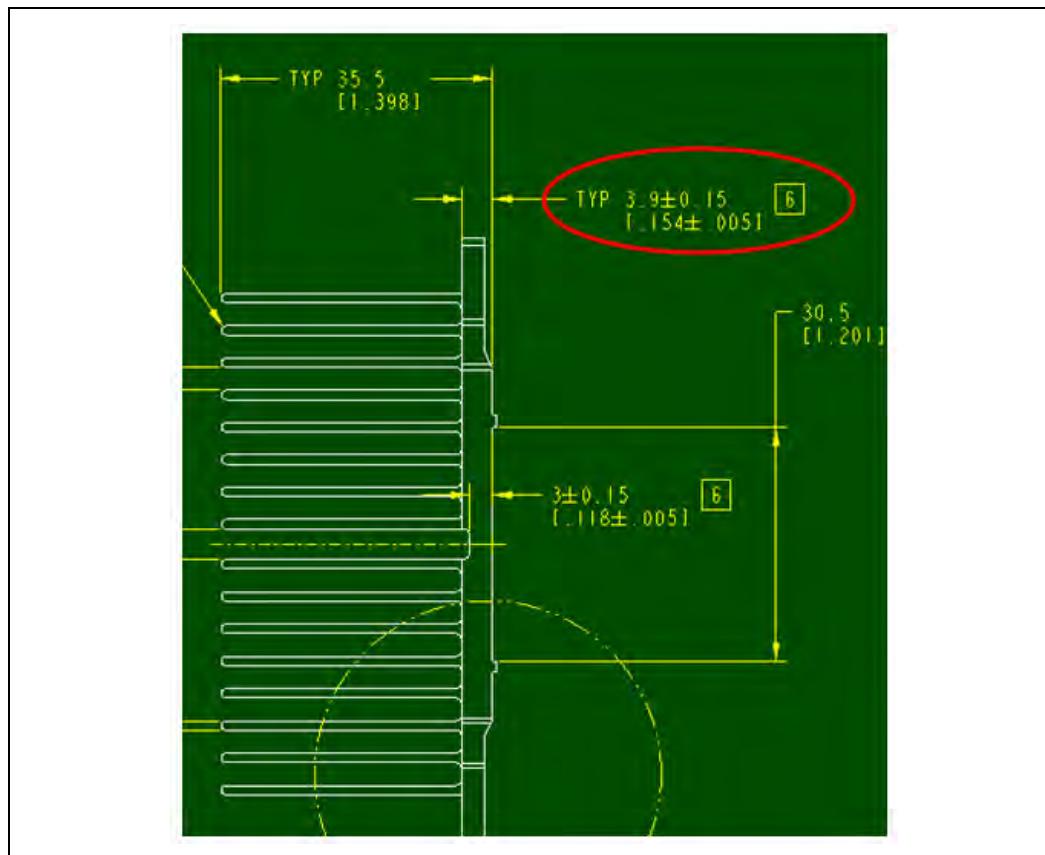

The PWSHS reference design has the cross-cut dimension change from 3.75 mm to 3.90 mm (see Figure 7) to prevent the gapping issue for cross-products heatsink design (Intel® 3 Series Chipsets and Intel® 4 Series Chipsets).

**Note:** The nominal height of (G)MCH package (see Figure 2) is 0.25 mm lower compared to Intel® 3 Series Chipsets package. Customers should analyze this gapping issue resulting of thinner Intel® 4 Series Chipsets package (nominal height of 2.13 mm) compared to Intel® 3 Series Chipsets package (nominal height of 2.38 mm) prior to design.

**Note:** The PWSHS reference design retention requires zero gap (between anchor wire clip and ramp retainer) to ensure effective top-side stiffening for solder joint protection. This cross-cut dimension change design allows to be used on Intel® 3 Series Chipsets without assembly issue.

Figure 7. Cross-Cut Dimension Change of PWSHS Reference Design

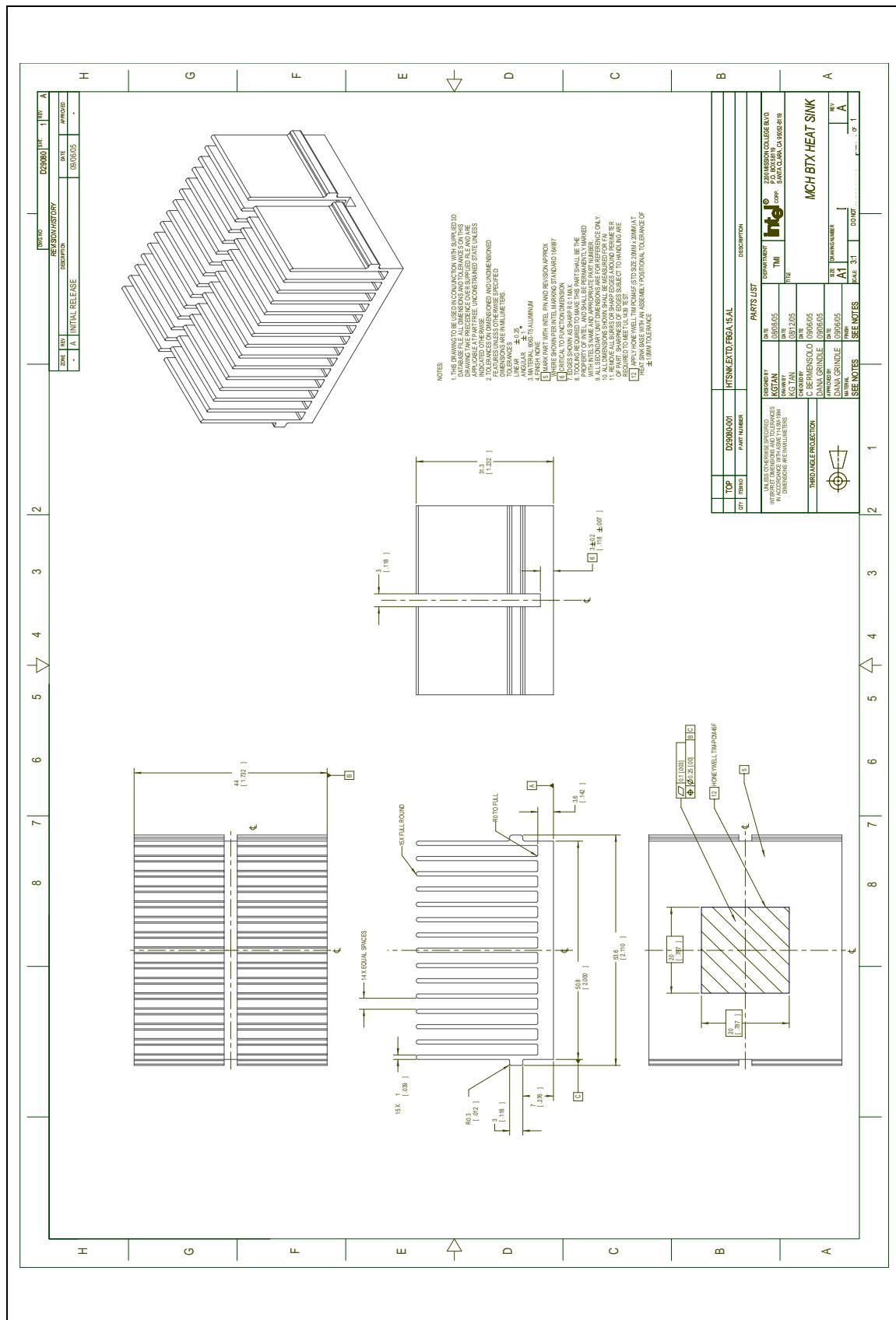

The BTX reference design for the (G)MCH will reuse the Z-clip heatsink and MB anchors from the Intel® 3 Series Chipsets thermal solution. The thermal interface material and extrusion design requirements are being evaluated for changes necessary to meet the (G)MCH thermal requirements. The keep out zone remains the same as used with the Intel® 3 Series Chipsets, see Figure 16.

This chapter provides detailed information on operating environment assumptions, heatsink manufacturing, and mechanical reliability requirements for the (G)MCH.

## 4.1 Operating Environment

The operating environment of the (G)MCH will differ depending on system configuration and motherboard layout. This section defines operating environment boundary conditions that are typical for ATX and BTX form factors. The system designer should perform analysis in the expected platform operating environment to assess impact on thermal solution selection.

#### 4.1.1 ATX Form Factor Operating Environment

The (G)MCH reference design thermal solution has been optimized to meet all three boundary conditions for 65W/95W/130W processor TDPs. The highest processor TDP provide a boundary condition for the (G)MCH heatsink with higher air inlet speed and temperature ( $T_{A,i}$ ) while the lowest processor TDP provides lower air inlet speed and temperature. The (G)MCH heatsink design is required to meet all of these boundary conditions as specified in Table 3.

**Table 3. (G)MCH Heatsink Boundary Condition Summary in ATX Platforms**

| Processor TDP (TDP) | Airflow Speed (LFM) | Air Inlet Temperature ( $T_{A,i}$ ) |

|---------------------|---------------------|-------------------------------------|

| 65 W                | 245                 | 47.2 °C                             |

| 95 W                | 292                 | 50.0 °C                             |

| 130 W               | 341                 | 51.6 °C                             |

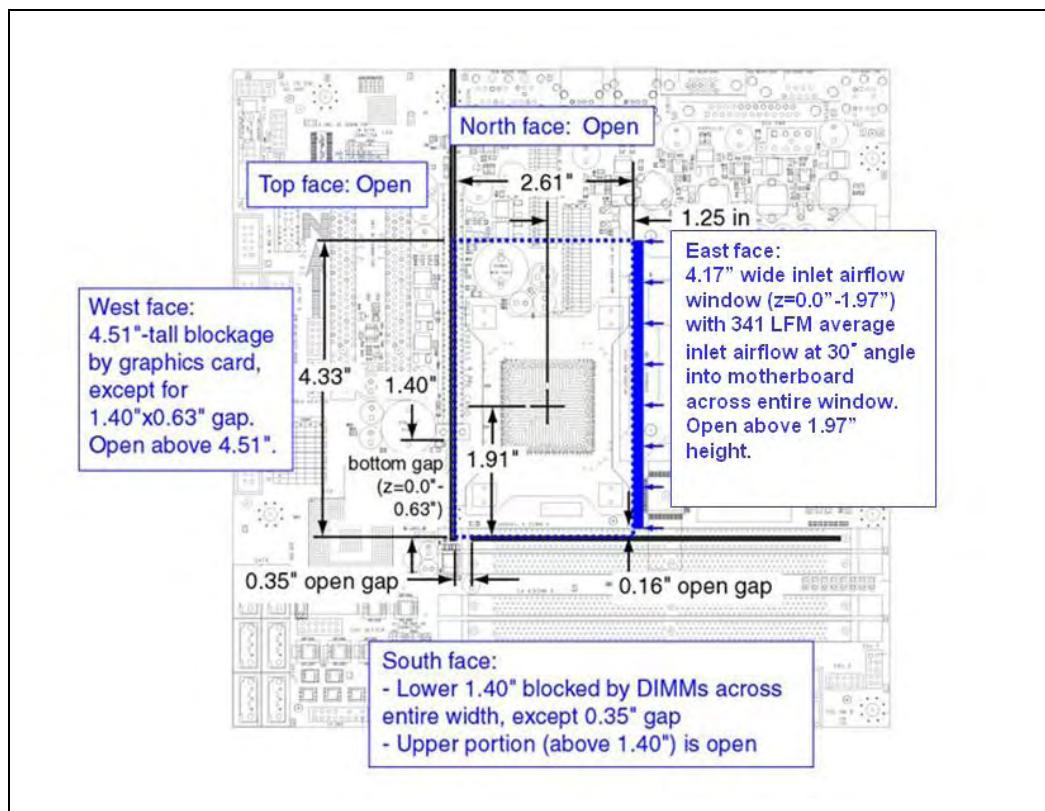

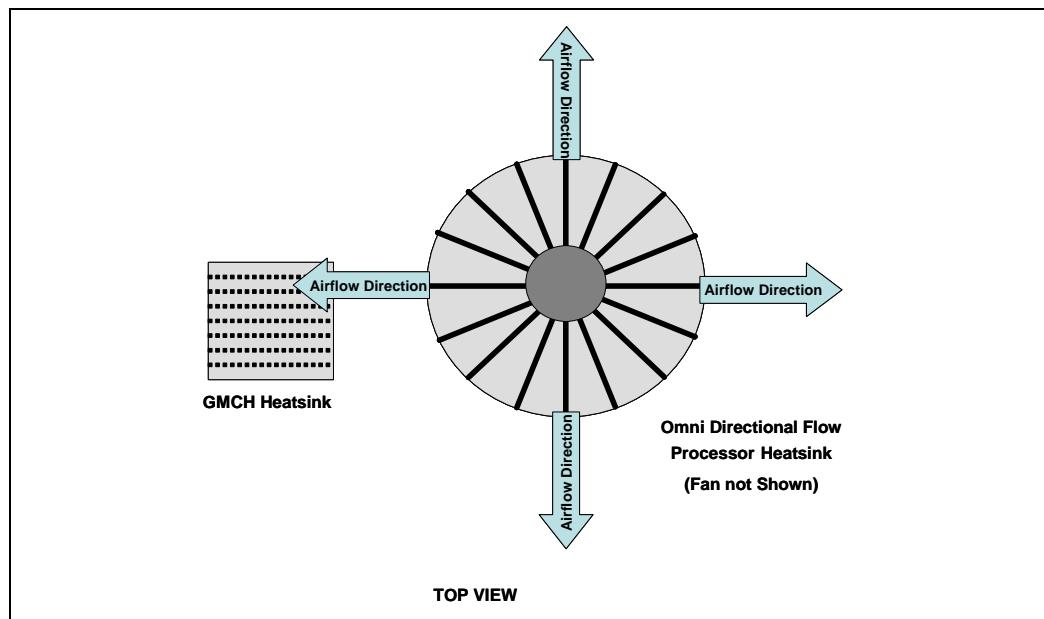

In ATX platforms using the 130 W TDP processor, an airflow speed of 1.73 m/s [341 lfm] is assumed to be approaching the heatsink at a 30° angle from the processor thermal solution, see Figure 8 and Figure 9 for more details. The local ambient air temperature,  $T_{A,i}$ , at the (G)MCH heatsink in an ATX platform is assumed to be 51.6 °C for the (G)MCH. The airflow assumed above can be achieved by using a processor heatsink providing omni directional airflow, such as a radial fin or "X" pattern heatsink. Such a heatsink can deliver airflow to both the (G)MCH and other areas like the voltage regulator, as shown in Figure 10. In addition, (G)MCH board placement should ensure that the (G)MCH heatsink is within the air exhaust area of the processor heatsink.

**Note that heatsink orientation alone does not guarantee that airflow speed will be achieved.** The system integrator should use analytical or experimental means to determine whether a system design provides adequate airflow speed for a particular (G)MCH heatsink.

The thermal designer must carefully select the location to measure airflow to get a representative sampling. ATX platforms need to be designed for the worst-case thermal environment, typically assumed to be 35 °C ambient temperature external to the system measured at sea level.

Figure 8. ATX Boundary Conditions

**Figure 9. Side View of ATX Boundary Conditions**

**Figure 10. Processor Heatsink Orientation to Provide Airflow to (G)MCH Heatsink on an ATX Platform**

Other methods exist for providing airflow to the (G)MCH heatsink, including the use of system fans and/or ducting, or the use of an attached fan (active heatsink).

#### 4.1.2 Balanced Technology Extended (BTX) Form Factor Operating Environment

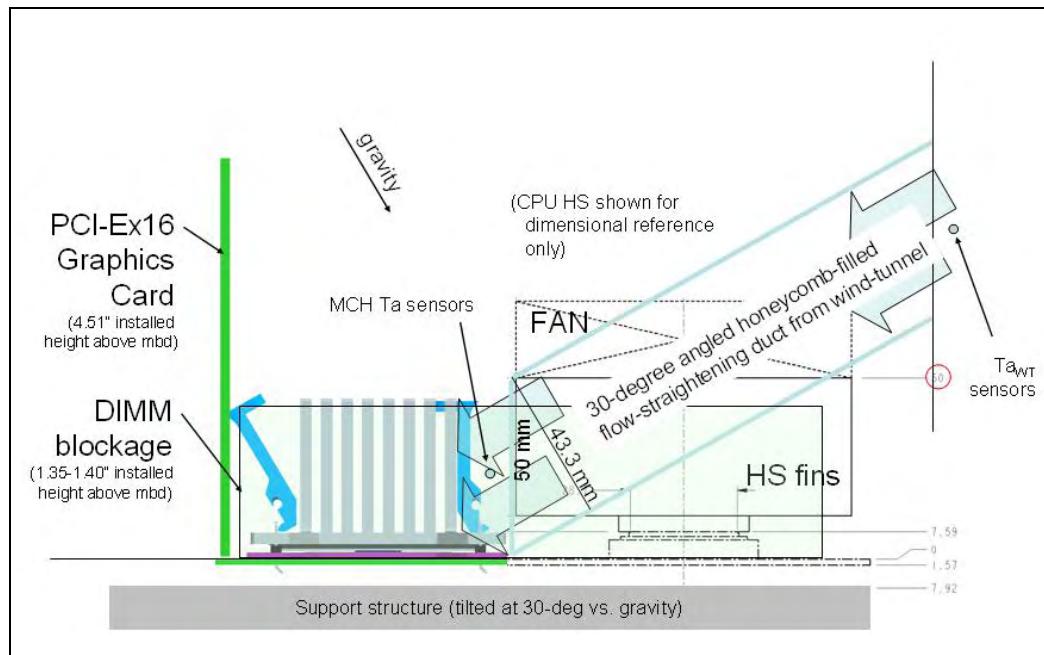

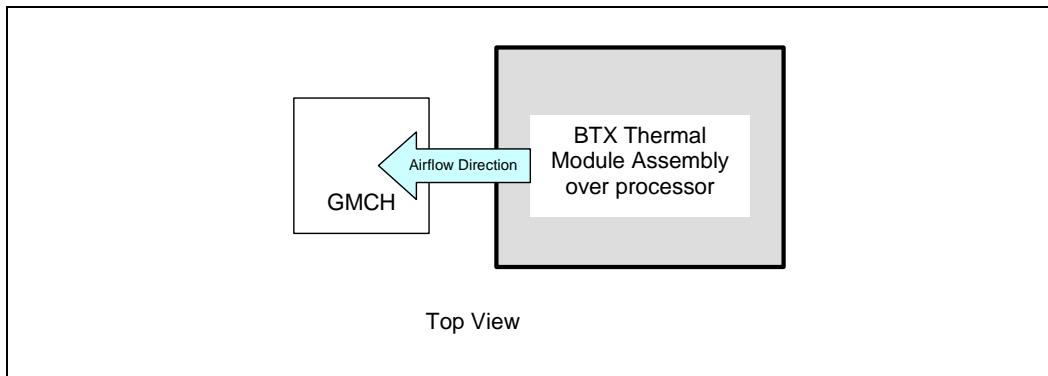

This section provides operating environment conditions based on what has been exhibited on the Intel BTX Entertainment PC reference design, refer to the *Balanced Technology Extended (BTX) Entertainment PC Case Study* for detail system study. On a BTX platform, the (G)MCH obtains in-line airflow directly from the processor thermal module. Since the processor thermal module provides lower inlet temperature airflow to the processor, reduced inlet ambient temperatures are also often seen at the (G)MCH as compared to ATX. An example of how airflow is delivered to the (G)MCH on a BTX platform is shown in Figure 11.

A set of three system level boundary conditions will be established to determine (G)MCH thermal solution requirement.

- Low external ambient (23 °C)/ idle power for the components (Case 3). This covers the system idle acoustic condition

- Low external ambient (23 °C)/ TDP for the components (Case 2). The TMA fan speed is limited by the thermistor in the fan hub.

- High ambient (35 °C)/ TDP for the components (Case 1). This covers the maximum TMA fan speed condition.

The values in Table 4 correspond to the ePC configuration. For more details on the TMA airflow set points, refer to the *Balanced Technology Extended (BTX) System Design Guide*.

**Table 4. (G)MCH Heatsink Boundary Condition Summary in BTX Platforms**

| Case   | Processor TDP (TDP) | T <sub>A</sub> into MCH heatsink (°C) | Airflow into the (G)MCH heatsink (LFM) |

|--------|---------------------|---------------------------------------|----------------------------------------|

| Case 1 | 65W                 | 43.0                                  | 194                                    |

| Case 2 | 65W                 | 38.2                                  | 117                                    |

| Case 3 | 65W                 | 34.7                                  | 29.5                                   |

**Note:** The customer should analyze their system design to verify their applicable boundary conditions prior to design. The thermal designer must carefully select the location to measure airflow to get a representative sampling. BTX platforms need to be designed for the worst-case thermal environment, typically assumed to be 35 °C ambient temperature external to the system measured at sea level.

**Note:** The risk of the solder ball fracture can be minimized with good chassis structure design on a BTX platform, refer to the *Balanced Technology Extended (BTX) Chassis Design Guide* (or *Balanced Technology Extended (BTX) System Design Guide*) for detail chassis mechanical design.

**Figure 11. Processor Heatsink Orientation to Provide Airflow to (G)MCH Heatsink on a Balanced Technology Extended (BTX) Platform**

## 4.2 Reference Design Mechanical Envelope

The motherboard component keep-out restrictions for the (G)MCH on an ATX platform are included in Appendix B, Figure 15. The motherboard component keep-out restrictions for the (G)MCH on a BTX platform are included in Appendix B, Figure 16.

## 4.3 Thermal Solution Assembly

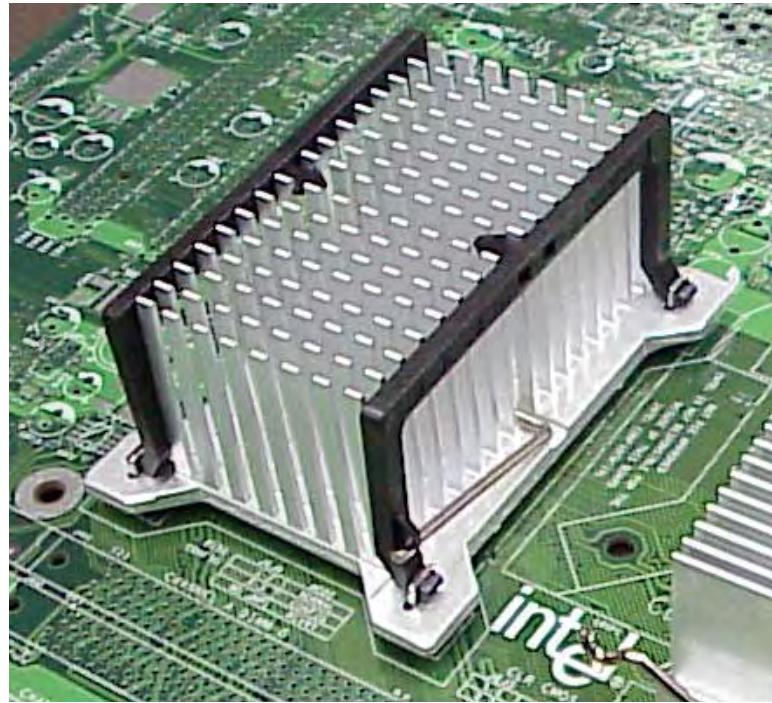

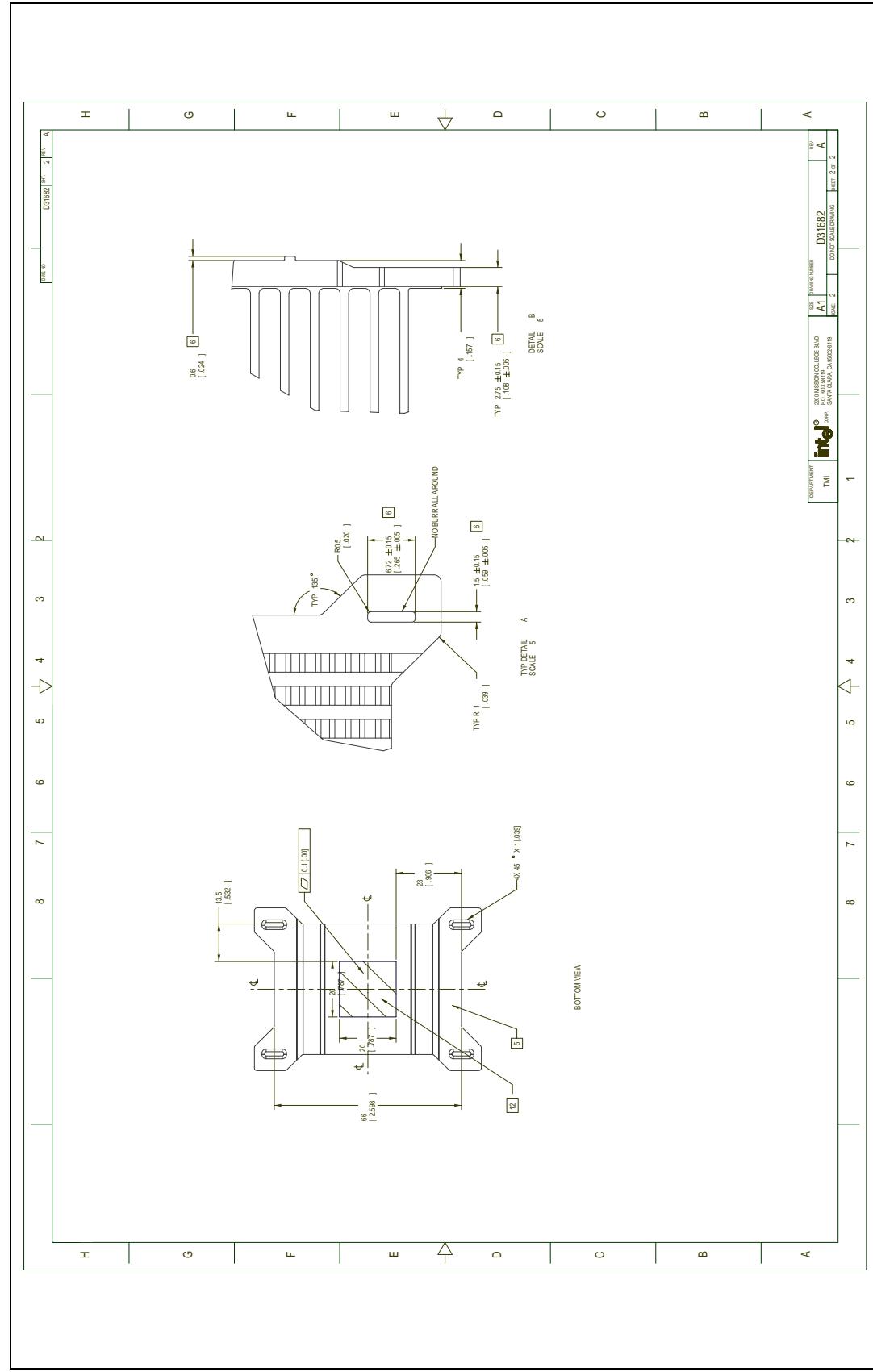

The reference thermal solution for the (G)MCH for an ATX chassis is shown in Figure 12 and is an aluminum extruded heatsink that uses two ramp retainers, a wire preload clip, and four motherboard anchors. Refer to Appendix B for the mechanical drawings. The heatsink is attached to the motherboard by assembling the anchors into the board, placing the heatsink, with the wire preload clip over the (G)MCH and anchors at each of the corners, and securing the plastic ramp retainers through the anchor loops before snapping each retainer into the fin gap. Leave the wire preload clip loose in the extrusion during the wave solder process. The assembly is then sent through the wave process. Post wave, the wire preload clip is snapped into place on the hooks located on each of the ramp retainers. The clip provides the mechanical preload to the package. This mechanical preload is necessary to provide both sufficient pressure to minimize thermal contact resistance and improvement for solder ball joint reliability. The mechanical stiffness and orientation of the extruded heat sink also provides protection to reduce solder ball reliability risk. A thermal interface material (*Honeywell PCM45F*) is pre-applied to the heatsink bottom over an area which contacts the package die.

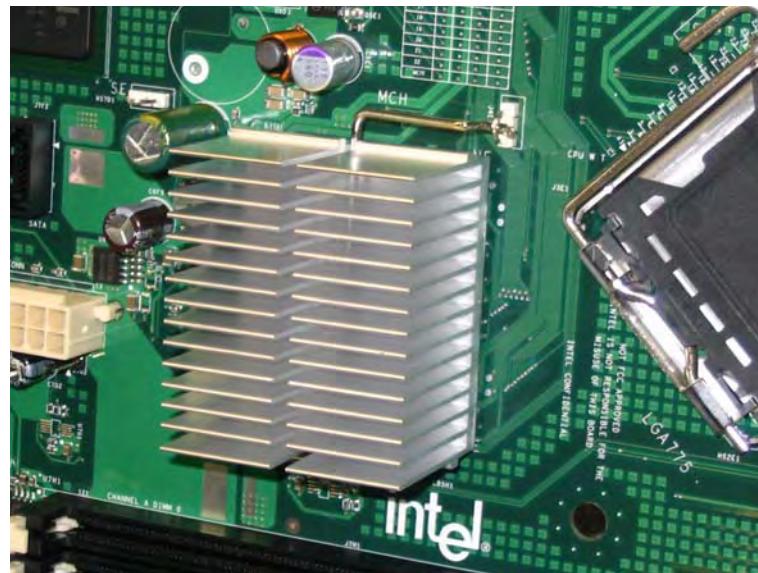

The design concept for the (G)MCH in a BTX chassis is shown in Figure 13. The heatsink is aluminum extruded and utilizes a Z-clip for attach. The clip is secured to the system motherboard via two solder down anchors around the (G)MCH. The clip helps to provide a mechanical preload to the package via the heatsink. A thermal interface material (*Honeywell PCM45F*) will be pre-applied to the heatsink bottom over an area in contact with the package die.

**Note:** To minimize solder ball joint reliability risk, the BTX Z-clip heatsink is intended to be used with the Support Retention Mechanism (SRM) described in the *Balanced Technology Extended (BTX) Interface Specification*. For additional information on designing the BTX chassis to minimize solder ball joint reliability, refer to the *Balanced Technology Extended (BTX) Chassis Design Guide*.

Figure 12. Design Concept for ATX (G)MCH Heatsink — Installed on Board

Figure 13. Design Concept for Balanced Technology Extended (BTX) (G)MCH Heatsink Design — Installed on Board

## 4.4

## Environmental Reliability Requirements

The environmental reliability requirements for the reference thermal solution are shown in Table 5 and Table 6. These should be considered as general guidelines. Validation test plans should be defined by the user based on anticipated use conditions and resulting reliability requirements.

The ATX testing will be performed with the sample board mounted on a test fixture and includes a processor heatsink with a mass of 550g. The test profiles are unpackaged board level limits.

**Table 5. ATX Reference Thermal Solution Environmental Reliability Requirements (Board Level)**

| Test <sup>1</sup> | Requirement                                                                                                                                                                                                                                                                      | Pass/Fail Criteria <sup>2</sup> |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Mechanical Shock  | <ul style="list-style-type: none"> <li>3 drops for + and - directions in each of 3 perpendicular axes (i.e., total 18 drops).</li> <li>Profile: 50 G, Trapezoidal waveform, 4.3 m/s [170 in/s] minimum velocity change</li> </ul>                                                | Visual\Electrical Check         |

| Random Vibration  | <ul style="list-style-type: none"> <li>Duration: 10 min/axis, 3 axes</li> <li>Frequency Range: 0.01 g<sup>2</sup>/Hz @ 5Hz ramping to 0.02 g<sup>2</sup>/Hz @20 Hz, 0.02 g<sup>2</sup>/Hz @ 20 Hz to 500 Hz</li> <li>Power Spectral Density (PSD) Profile: 3.13 g RMS</li> </ul> | Visual/Electrical Check         |

| Thermal Cycling   | <ul style="list-style-type: none"> <li>Non-Operating, -40 °C to +70 °C</li> </ul>                                                                                                                                                                                                | Thermal Performance             |

| Humidity          | <ul style="list-style-type: none"> <li>85 % relative humidity / 55 °C</li> </ul>                                                                                                                                                                                                 | Visual Check                    |

**NOTES:**

1. The above tests should be performed on a sample size of at least 12 assemblies from 3 different lots of material.

2. Additional Pass/Fail Criteria may be added at the discretion of the user.

The current plan for BTX reference solution testing is to mount the sample board mounted in a representative BTX chassis with a thermal module assembly having a mass of 900g. The test profiles are unpackaged system level limits.

**Table 6. Balanced Technology Extended (BTX) Reference Thermal Solution Environmental Reliability Requirements (System Level)**

| Test <sup>1</sup> | Requirement                                                                                                                                                                                                                                                                       | Pass/Fail Criteria <sup>2</sup> |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Mechanical Shock  | <ul style="list-style-type: none"> <li>3 drops for + and - directions in each of 3 perpendicular axes (i.e., total 18 drops).</li> <li>Profile: 25g, Trapezoidal waveform, 5.7 m/s [225 in/sec] minimum velocity change.</li> </ul>                                               | Visual\Electrical Check         |

| Random Vibration  | <ul style="list-style-type: none"> <li>Duration: 10 min/axis, 3 axes</li> <li>Frequency Range: 0.001 g<sup>2</sup>/Hz @ 5Hz ramping to 0.01 g<sup>2</sup>/Hz @20 Hz, 0.01 g<sup>2</sup>/Hz @ 20 Hz to 500 Hz</li> <li>Power Spectral Density (PSD) Profile: 2.20 g RMS</li> </ul> | Visual/Electrical Check         |

| Thermal Cycling   | <ul style="list-style-type: none"> <li>Non-Operating, -40 °C to +70 °C</li> </ul>                                                                                                                                                                                                 | Thermal Performance             |

| Humidity          | <ul style="list-style-type: none"> <li>85 % relative humidity / 55 °C</li> </ul>                                                                                                                                                                                                  | Visual Check                    |

**NOTES:**

1. The above tests should be performed on a sample size of at least 12 assemblies from 3 different lots of material.

2. Additional Pass/Fail Criteria may be added at the discretion of the user.

3. Mechanical Shock minimum velocity change is based on a system weight of 20 to 29 lbs.

4. For the chassis level testing the system will include: 1 HD, 1 ODD, 1 PSU, 2 DIMMs and the I/O shield.

§

## Appendix A Enabled Suppliers

Enabled suppliers for the (G)MCH reference thermal solution are listed in Table 7 and Table 8. The supplier contact information is listed in Table 9.

**Note:** These vendors and devices are listed by Intel as a convenience to Intel's general customer base, but Intel does not make any representations or warranties whatsoever regarding quality, reliability, functionality, or compatibility of these devices. This list and/or these devices may be subject to change without notice.

**Table 7. ATX Intel Reference Heatsink Enabled Suppliers for (G)MCH**

| ATX Items      | Intel PN   | AVC        | CCI          | Foxconn   | Wieson        |

|----------------|------------|------------|--------------|-----------|---------------|

| Heatsink & TIM | D31682-002 | S902Y10002 | 335I83330201 |           |               |

| Plastic Clip   | C85370-001 | P109000024 | 334C863501A  | 3EE77-002 |               |

| Wire Clip      | D29082-001 | A208000233 | 334I833301A  | 3KS02-155 |               |

| Anchor         | C85376-001 |            |              | 2Z802-015 | G2100C888-143 |

**Table 8. BTX Intel Reference Heatsink Enabled Suppliers for (G)MCH**

| BTX Items                              | Intel PN   | AVC        | CCI        | Foxconn    | Wieson         |

|----------------------------------------|------------|------------|------------|------------|----------------|

| Heatsink assembly (HS/TIM & Wire Clip) | D34258-001 | S905Y00001 | 00I833201A | 2ZQ99-066  |                |

| Anchor (Lead Free)                     | A13494-008 |            |            | HB9703E-DW | G2100C888-064H |

**Table 9. Supplier Contact Information**

| <b>Supplier</b>             | <b>Contacts</b> | <b>Phone</b>               | <b>Email</b>            |

|-----------------------------|-----------------|----------------------------|-------------------------|

| AVC (Asia Vital Components) | David Chao      | +886-2-2299-6930 ext. 7619 | david_chao@avc.com.tw   |

|                             | Raichel Hsu     | +886-2-2299-6930 ext. 7630 | raichel_hsi@avc.com.tw  |

| CCI(Chau Choung Technology) | Monica Chih     | +886-2-2995-2666           | monica_chih@ccic.com.tw |

|                             | Harry Lin       | (714) 739-5797             | hlinack@aol.com         |

| Foxconn                     | Jack Chen       | (408) 919-6121             | jack.chen@foxconn.com   |

|                             | Wanchi Chen     | (408) 919-6135             | wanchi.chen@foxconn.com |

| Wieson Technologies         | Chary Lee       | +886-2-2647-1896 ext. 6684 | chary@wieson.com        |

|                             | Henry Liu       | +886-2-2647-1896 ext. 6330 | henry@wieson.com        |

§

## Appendix B Mechanical Drawings

---

The following table lists the mechanical drawings available in this document:

| Drawing Name                                                                                 | Page Number |

|----------------------------------------------------------------------------------------------|-------------|

| . (G)MCH Package Drawing                                                                     | 34          |

| . (G)MCH Component Keep-Out Restrictions for ATX Platforms                                   | 35          |

| . (G)MCH Component Keep-Out Restrictions for Balanced Technology Extended (BTX) Platforms    | 36          |

| . (G)MCH Reference Heatsink for ATX Platforms – Sheet 1                                      | 37          |

| . (G)MCH Reference Heatsink for ATX Platforms – Sheet 2                                      | 38          |

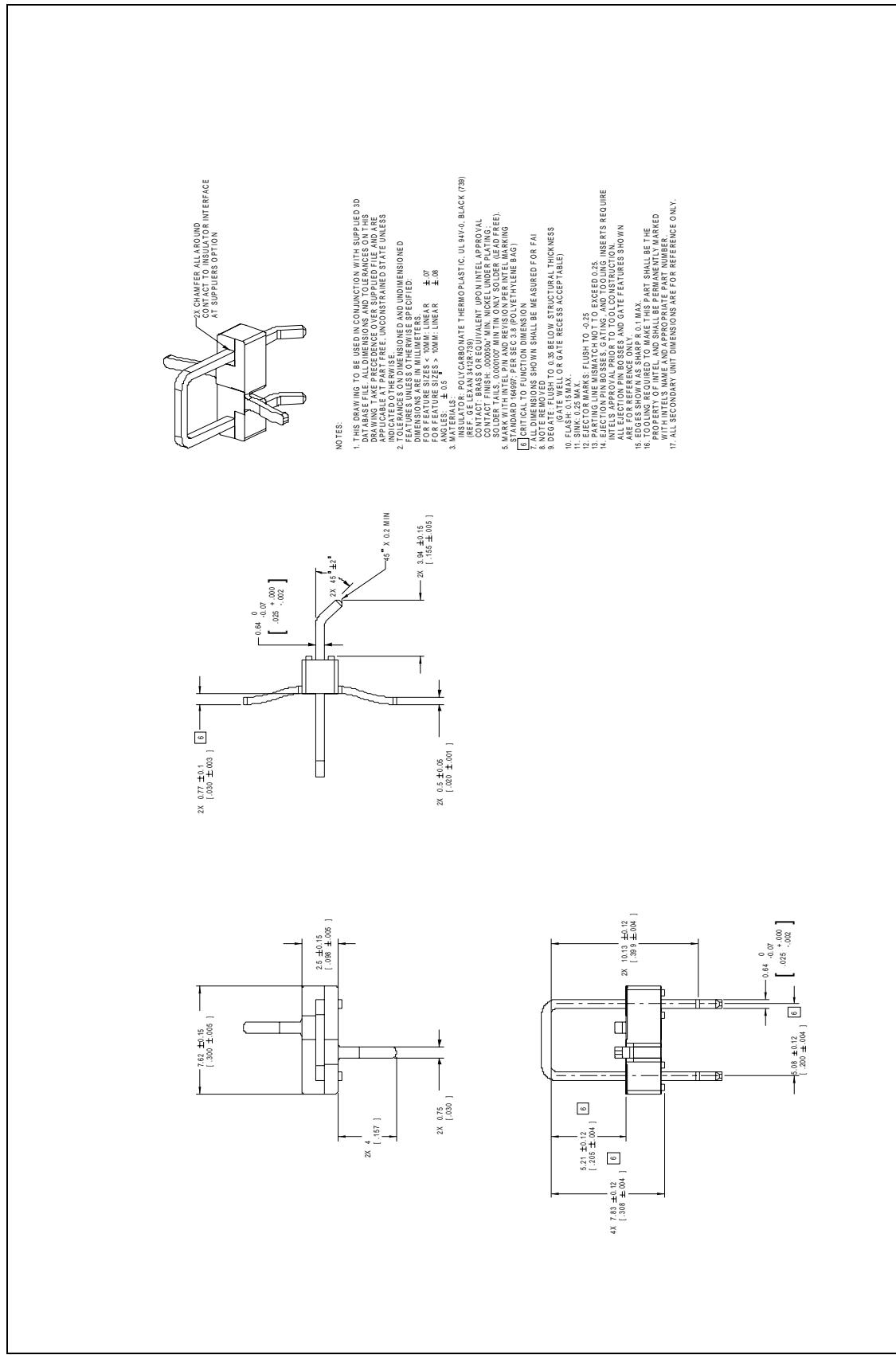

| . (G)MCH Reference Heatsink for ATX Platforms – Anchor                                       | 39          |

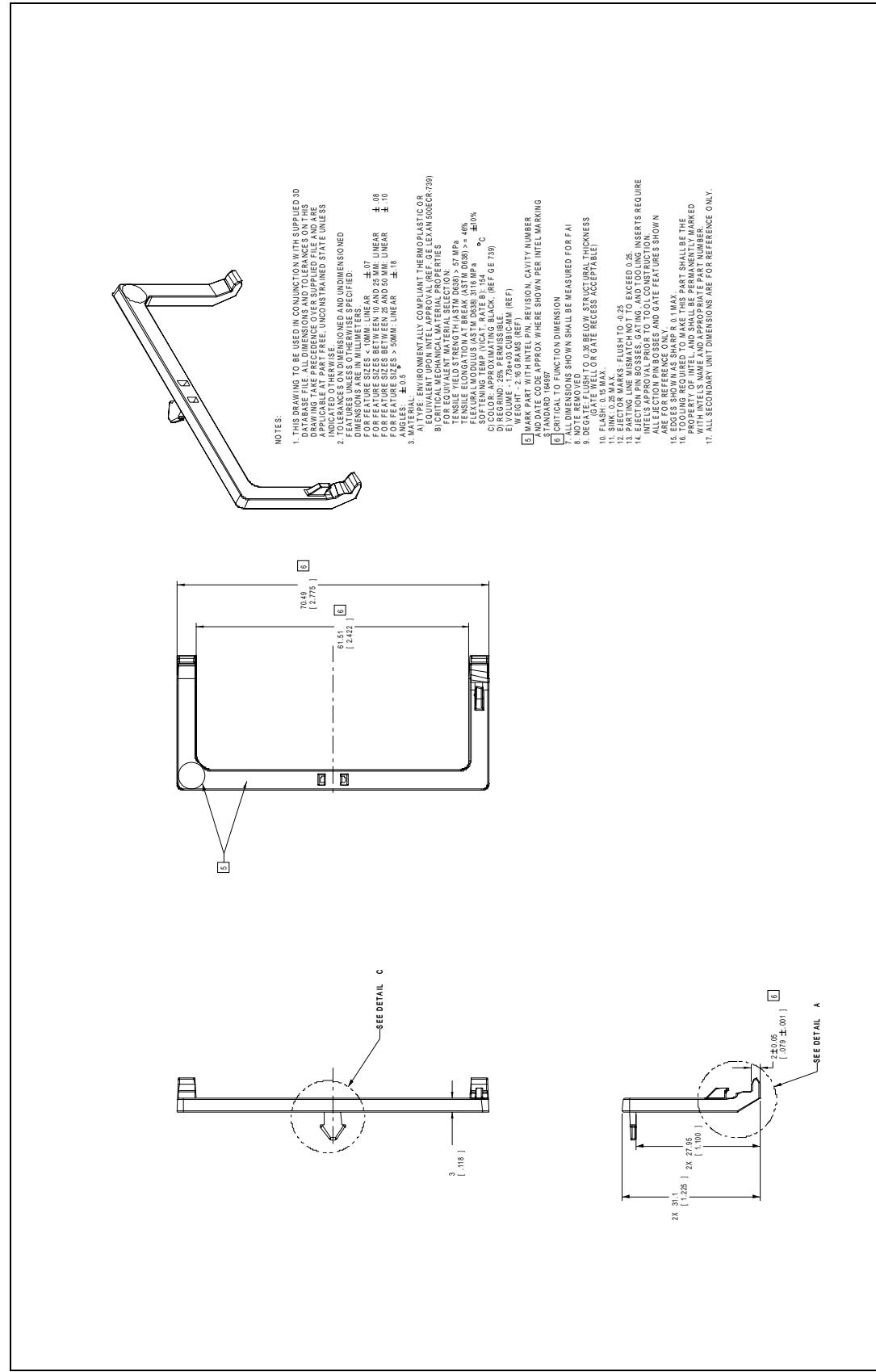

| . (G)MCH Reference Heatsink for ATX Platforms – Ramp Retainer Sheet 1                        | 40          |

| . (G)MCH Reference Heatsink for ATX Platforms – Ramp Retainer Sheet 2                        | 41          |

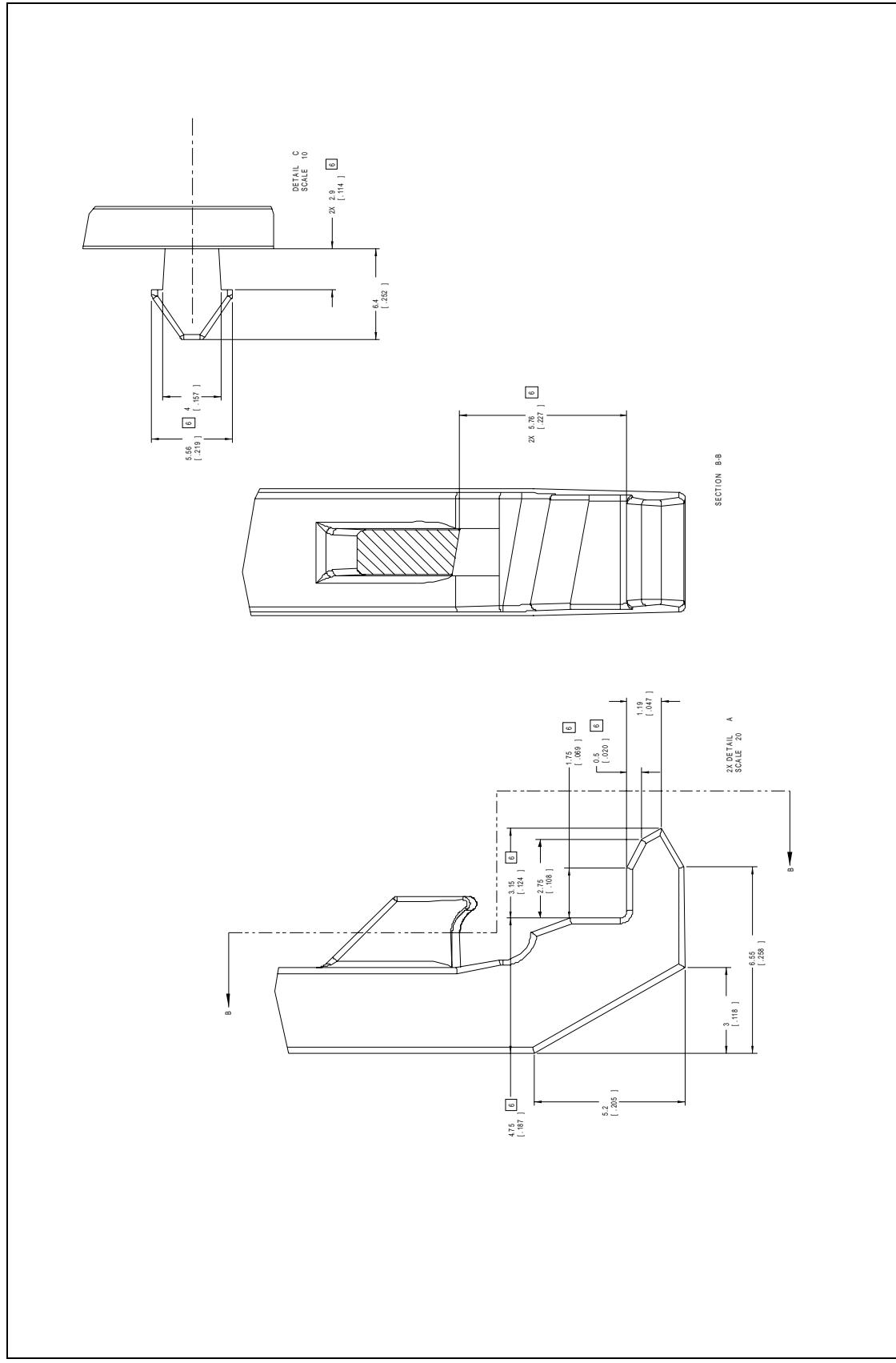

| . (G)MCH Reference Heatsink for ATX Platforms – Wire Preload Clip                            | 42          |

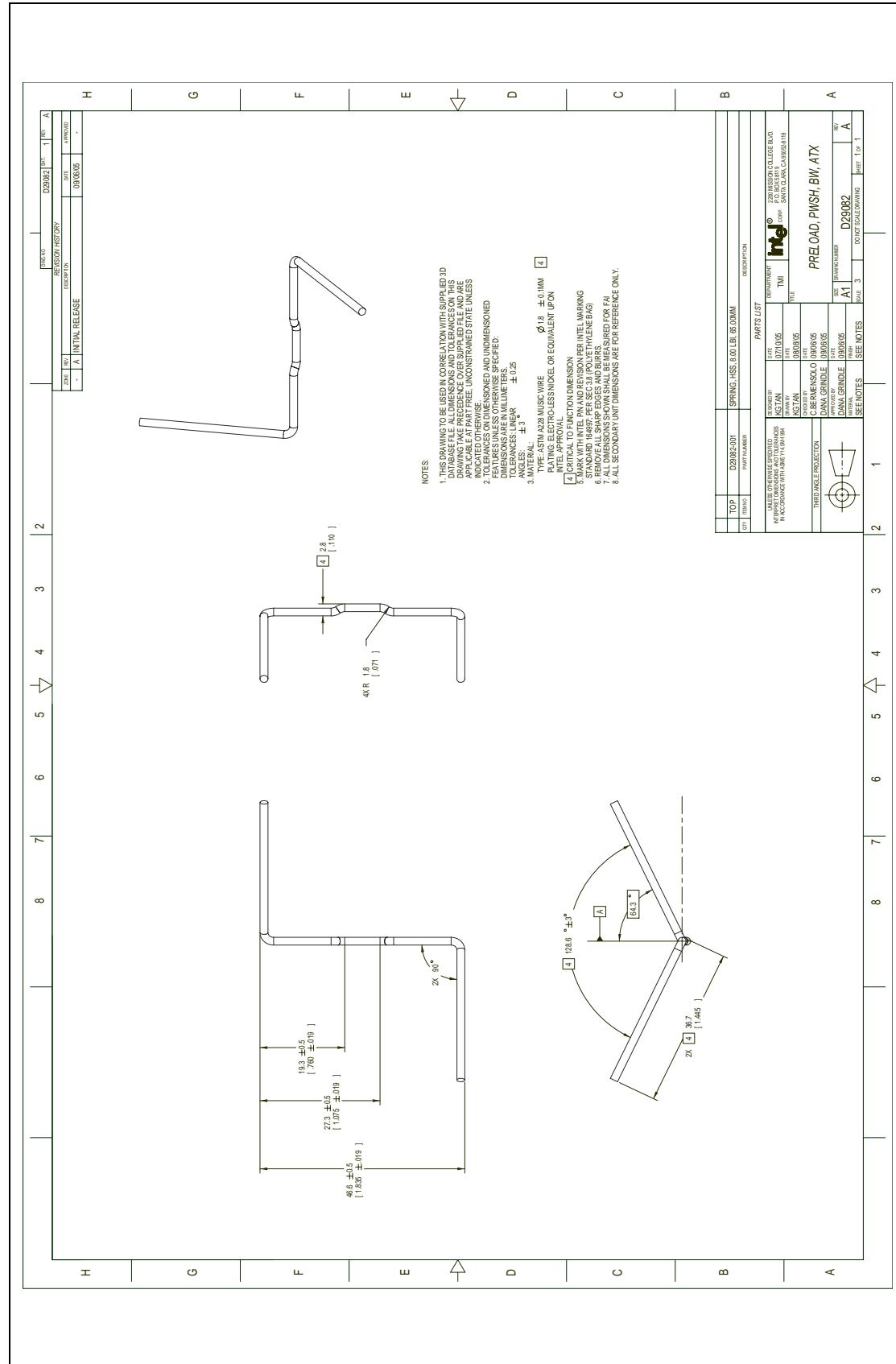

| . (G)MCH Reference Heatsink for Balanced Technology Extended (BTX) Platforms                 | 43          |

| . (G)MCH Chipsets Reference Heatsink for Balanced Technology Extended (BTX) Platforms – Clip | 44          |

Figure 14. (G)MCH Package Drawing

**Figure 15. (G)MCH Component Keep-Out Restrictions for ATX Platforms**

Figure 16. (G)MCH Component Keep-Out Restrictions for Balanced Technology Extended (BTX) Platforms

Figure 17. (G)MCH Reference Heatsink for ATX Platforms – Sheet 1

Figure 18. (G)MCH Reference Heatsink for ATX Platforms – Sheet 2

Figure 19. (G)MCH Reference Heatsink for ATX Platforms – Anchor

Figure 20. (G)MCH Reference Heatsink for ATX Platforms – Ramp Retainer Sheet 1

Figure 21. (G)MCH Reference Heatsink for ATX Platforms – Ramp Retainer Sheet 2

Figure 22. (G)MCH Reference Heatsink for ATX Platforms – Wire Preload Clip

Figure 23. (G)MCH Reference Heatsink for Balanced Technology Extended (BTX) Platforms

Figure 24. (G)MCH Chipsets Reference Heatsink for Balanced Technology Extended (BTX) Platforms – clip