# 82573 NVM Map and Programming Information Guide

September 2008

Order No.: 315483-005 Revision 2.7

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

IMPORTANT - PLEASE READ BEFORE INSTALLING OR USING INTEL® PRE-RELEASE PRODUCTS.

Please review the terms at http://www.intel.com/netcomms/prerelease\_terms.htm carefully before using any Intel® pre-release product, including any evaluation, development or reference hardware and/or software product (collectively, "Pre-Release Product"). By using the Pre-Release Product, you indicate your acceptance of these terms, which constitute the agreement (the "Agreement") between you and Intel Corporation ("Intel"). In the event that you do not agree with any of these terms and conditions, do not use or install the Pre-Release Product and promptly return it unused to Intel.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The 82573 GbE Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/products/ht/Hyperthreading\_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from: Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All Rights Reserved.

# Contents

| 1.0 | Intro |                | and Scope                                                             |    |

|-----|-------|----------------|-----------------------------------------------------------------------|----|

|     | 1.1   |                | ted NVM Devices                                                       |    |

|     | 1.2   |                | evice Detection                                                       |    |

|     |       |                | CRC Field                                                             |    |

|     | 1.3   |                | Operation with EEPROM                                                 |    |

|     | 1.4   |                | Operation with Flash                                                  |    |

|     |       | 1.4.1          | Shadow RAM                                                            |    |

|     | 1.5   |                | M Mode                                                                |    |

|     | 1.6   |                | ients                                                                 |    |

|     | 1.7   |                | IVM Protection Scheme                                                 |    |

|     |       | 1.7.1<br>1.7.2 | Initial Programming for Shared Flash with ICH                         |    |

|     | 1.8   |                | ATE Utility                                                           |    |

|     | 1.0   | 1.8.1          | Command Line Parameters                                               |    |

| ~ ~ |       |                |                                                                       |    |

| 2.0 |       |                | у Мар                                                                 |    |

|     | 2.1   |                | Configuration Table                                                   |    |

|     |       | 2.1.1<br>2.1.2 | Ethernet Address (Words 00h-02h)                                      | 16 |

|     |       |                | Compatibility Field (Word 03h-07h)                                    |    |

|     |       | 2.1.3<br>2.1.4 | PBA Number (Word 08h-09h)<br>Initialization Control Word 1 (Word 0Ah) |    |

|     |       | 2.1.4          | Subsystem ID (Word 0Bh)                                               |    |

|     |       | 2.1.5          | Subsystem Vendor ID (Word 0Ch)                                        |    |

|     |       | 2.1.7          | Device ID (Word ODh)                                                  |    |

|     |       | 2.1.7          | Vendor ID (Word 0Eh)                                                  |    |

|     |       | 2.1.9          | Initialization Control Word 2 (Word OFh)                              |    |

|     |       |                | NVM Word 0: NVM0 (Word 10h)                                           |    |

|     |       |                | NVM Word 1: NVM1 (Word 11h)                                           |    |

|     |       |                | NVM Word 2: NVM2 (Word 12h)                                           |    |

|     |       |                | Management Enable (Word 13h, High Byte)                               |    |

|     |       |                | Management Capabilities (Word 13h, Low Byte)                          |    |

|     |       | 2.1.15         | Extended Configuration Word 1 (Word 14h)                              | 23 |

|     |       |                | Extended Configuration Word 2 (Word 15h)                              |    |

|     |       |                | Extended Configuration Word 3 (Word 16h)                              |    |

|     |       |                | Memory Scrub Control / PCIe* Delay (Word 17h)                         |    |

|     |       |                | PCIe* Initial Configuration Word 1 (Word 18h)                         |    |

|     |       |                | PCIe* Initial Configuration Word 2 (Word 19h)                         |    |

|     |       |                | PCIe* Initial Configuration Word 3 (Word 1Ah)                         |    |

|     |       |                | PCIe* Control (Word 1Bh)                                              |    |

|     |       |                | PHY Configuration (Word 1Ch, High Byte)                               |    |

|     |       |                | LED Control Registers                                                 |    |

|     |       |                | Device Revision ID (Word 1Eh)<br>Firmware Configuration (Word 20h)    |    |

|     |       |                | LAN Power Consumption (Word 22h)                                      |    |

|     |       |                | Flash Software Detection Word (Word 23h)                              |    |

|     |       |                | Initialization Control Word 3 (Word 24h)                              |    |

|     |       |                | PXE Words (Words 30h to 3Eh)                                          |    |

|     |       |                | Checksum Word Calculation (Word 3Fh)                                  |    |

|     | 2.2   |                | rea 40h                                                               |    |

|     | 2.2   | 2.2.1          | Manageability D0 Power Consumption (Word 40h)                         |    |

|     |       | 2.2.1          | Manageability D3 Power Consumption (Word 41h)                         |    |

|     |       | 2.2.3          | IDE Device Word (Word 42h)                                            |    |

|     |       |                |                                                                       |    |

|      |            | 2.2.4              | Serial Port Device ID (Word 43h)                       | 38 |

|------|------------|--------------------|--------------------------------------------------------|----|

|      |            | 2.2.5              | KCS Device ID (Word 44h)                               |    |

|      |            | 2.2.6              | IDE Subsystem ID (Word 45h)                            | 39 |

|      |            | 2.2.7              | Serial Port Subsystem ID (Word 46h)                    | 39 |

|      |            | 2.2.8              | KCS Subsystem ID (Word 47h)                            | 39 |

|      |            | 2.2.9              | Future Request Time-Out (Word 48h)                     | 39 |

|      |            | 2.2.10             | Functions Control (Word 49h)                           | 40 |

|      |            | 2.2.11             | Flash Parameters (Word 4Ah)                            | 40 |

|      |            | 2.2.12             | Boot Expansion Address (Word 4Bh)                      | 40 |

|      |            | 2.2.13             | Boot Expansion Size (Word 4Ch)                         | 41 |

|      |            | 2.2.14             | KCS Device Class Code Low (Word 4Eh)                   | 41 |

|      |            | 2.2.15             | KCS Device Class Code High (Word 4Fh)                  | 41 |

|      | 2.3        | Intel <sup>®</sup> | AMT Main Area                                          | 42 |

|      |            | 2.3.1              | Intel <sup>®</sup> AMT MAC Address (Words 80h - 82h)   | 42 |

|      | 2.4        | ASF Co             | ntrol Words                                            | 42 |

|      |            | 2.4.1              | ASF Words: Content                                     | 42 |

|      |            | 2.4.2              | ASF Words: NVM Checksum (CRC)                          | 42 |

|      |            | 2.4.3              | ASF Configuration Map                                  |    |

| Α    | 0257       | 2 111/11           | Contents                                               | 15 |

| A    |            |                    | V with No Management and 1 Kb EEPROM Image             |    |

|      | A.1<br>A.2 |                    | . with No Management and 1 Kb EEPROM Image             |    |

|      |            |                    |                                                        |    |

| В    | Intel      | ® AMT (            | Guidelines for Local Programming of Shared SPI Devices | 46 |

|      | B.1        | Overvie            | ew                                                     |    |

|      |            | B.1.1              | Intel <sup>®</sup> Active Management Technology        | 46 |

|      | B.2        | Intel <sup>®</sup> | AMT Flash Image Map                                    | 46 |

|      |            | B.2.1              | Legacy Area                                            |    |

|      |            | B.2.2              | Legacy Area Scratch Sector                             |    |

|      |            | B.2.3              | Manageability Configuration Area                       |    |

|      |            | B.2.4              | Intel <sup>®</sup> AMT Configuration Area              |    |

|      |            | B.2.5              | ISV Storage (Third Party Data)                         |    |

|      |            | B.2.6              | Intel <sup>®</sup> AMT Code                            |    |

|      |            | B.2.7              | Intel <sup>®</sup> AMT Patches                         |    |

|      | B.3        | Local F            | irmware Update Process – Code Only                     | 48 |

| с    | Local      | Firmwa             | are Update Process – Recovery Mode                     | 51 |

| Figu | ires       |                    |                                                        |    |

|      |            |                    |                                                        |    |

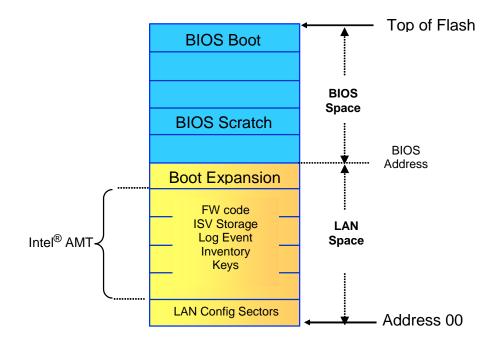

| 1 | Flash Mapping of the LAN and BIOS Regions | . 10 | C |

|---|-------------------------------------------|------|---|

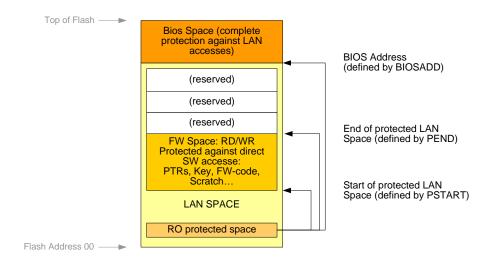

| 2 | NVM Protected Space Mapping               | . 12 | 2 |

## **Tables**

| 1  | EEPROM/Flash Configuration Size            | 8  |

|----|--------------------------------------------|----|

| 2  | Compatible EEPROM Parts                    | 8  |

| 3  | Compatible Flash Parts                     | 8  |

| 4  | Specifications for Flash Devices           | 9  |

| 5  | NVM Client Interface                       | 11 |

| 6  | Protected Spaces                           | 12 |

| 7  | 82573 NVM Map for Address Range 00h to 3Fh | 15 |

| 8  | MAC Address Example                        | 16 |

| 9  | Compatibility Field (Word 03h)             | 17 |

| 10 | Compatibility Field (Word 04h)             | 17 |

| 11 | Compatibility Field (Word 05h)             | 17 |

| 12 | Compatibility Field (Word 06h)             | 18 |

| 13 | Compatibility Field (Word 07h)                     | 18   |

|----|----------------------------------------------------|------|

| 14 | Initialization Control Word 1 (Word OAh)           | 18   |

| 15 | Device ID Values                                   | . 19 |

| 16 | Initialization Control Word 2 (Word 0Fh)           | 20   |

| 17 | NVM Word 0 (Word 10h)                              | . 21 |

| 18 | NVM Word 1 (Word 11h)                              |      |

| 19 | NVM Word 2 (Word 12h)                              |      |

| 20 | Management Enable Byte (Word 13h, High Byte)       | . 22 |

| 21 | Management Capabilities Byte (Word 13h, Low Byte)  | 23   |

| 22 | Extended Configuration Word 1 (Word 14h)           | . 23 |

| 23 | Extended Configuration Word 2 (Word 15h)           |      |

| 24 | Extended Configuration Word 3 (Word 16h)           | . 23 |

| 25 | Memory Scrub Control / PCIe Delay (Word 17h)       | . 24 |

| 26 | PCIe Initial Configuration Word 1 (Word 18h)       | 24   |

| 27 | PCIe Initial Configuration Word 2 (Word 19h)       | . 24 |

| 28 | PCIe Initial Configuration Word 3 (Word 1Ah)       | . 25 |

| 29 | PCIe Control (Word 1Bh)                            |      |

| 30 | PHY Configuration (Word 1Ch, High Byte)            |      |

| 31 | LED 1 Configuration Defaults (Word 1Ch, Low Byte)  | . 28 |

| 32 | LED 0 and 2 Configuration Defaults (Word 1Fh)      | . 29 |

| 33 | LED Control Source                                 |      |

| 34 | Device Revision ID (Word 1Eh)                      |      |

| 35 | Firmware Configuration (Word 20h)                  |      |

| 36 | LAN Power Consumption (Word 22h)                   |      |

| 37 | Flash Software Detection Word (Word 23h)           |      |

| 38 | Initialization Control Word 3 (Word 24h)           | . 31 |

| 39 | Boot Agent Main Setup Options (Word 30h)           |      |

| 40 | Boot Agent Configuration Custom Options (Word 31h) |      |

| 41 | Boot Agent Configuration Custom Options (Word 32h) |      |

| 42 | IBA Capabilities (Word 33h)                        |      |

| 43 | Boot Configuration Start Address (Word 3Dh)        |      |

| 44 | Boot Agent Configuration Custom Options (Word 3Eh) |      |

| 45 | 82573 NVM Map for Address Range 40h to 4Fh         |      |

| 46 | Manageability D0 Power Consumption (Word 40h)      |      |

| 47 | Manageability D3 Power Consumption (Word 41h)      |      |

| 48 | Future Request Time-Out (Word 48h)                 |      |

| 49 | Functions Control (Word 49h)                       |      |

| 50 | Flash Parameters (Word 4Ah)                        |      |

| 51 | Boot Expansion Address (Word 4Bh)                  |      |

| 52 | Boot Expansion Size (Word 4Ch)                     |      |

| 53 | KCS Device Class Code Low (Word 4Eh)               | . 41 |

| 54 | KCS Device Class Code High (Word 4Fh)              |      |

| 55 | 82573E/V NVM Map for ASF                           | . 43 |

# **Revision History**

| Date                                              | Revision | Description                                                                                                                         |  |

|---------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| September 2005                                    | 2.0      | Initial release.                                                                                                                    |  |

| January 20062.1Device ID Value added for the 8257 |          | Updated values for the default of Word 12h<br>Device ID Value added for the 82573L<br>Included new (11/05) NVM Images in Appendix A |  |

| September 2006 2.2 Included 82573V in section 2.4 |          | Included 82573V in section 2.4                                                                                                      |  |

| October 2006                                      | 2.3      | Major edit all sections<br>Updated Table 3 "Compatible Flash Parts".<br>Added document ordering number.                             |  |

| October 2006                                      | 2.4      | Updated Tables 1, 3, 14, and 16.<br>Removed the note from Section 2.1.11.                                                           |  |

| January 2007                                      | 2.5      | Removed Table 31 "LED Control".                                                                                                     |  |

| May 2007                                          | 2.6      | Updated Table 16 (bit 0 description). Changed setting to 1b for the 82573E/V only.                                                  |  |

| September 2008                                    | 2.7      | Updated Boot Agent bit descriptions (removed all references to RPL).                                                                |  |

## 1.0 Introduction and Scope

This document covers programming information for the Non-Volatile Memory (NVM) of the Intel<sup>®</sup> 82573. For purposes of this document, 82573 refers to the 82573E, 82573V and 82573L, unless otherwise stated.

The Intel<sup>®</sup> 82573 requires non-volatile content for device configuration, log events and firmware extensions. The NVM might contain the following four main regions:

- LAN Configuration Space for Hardware. This area is accessed by hardware and loaded by the 82573 after power-up, PCI reset de-assertion, D3 to D0 transition, or software commanded EEPROM reset (CTRL\_EXT.EE\_RST).

- Firmware Space. This space is accessed by the 82573E/V in Alert Standard Format (ASF) mode or by the 82573E in Intel<sup>®</sup> Active Management Technology (Intel<sup>®</sup> AMT) mode. In ASF mode, the 82573E/V loads the data following power-up, ASF soft reset (ASF FRC\_RST), or software commanded ASF EEPROM read (ASF FRC\_EELD). In Intel<sup>®</sup> AMT mode, this space is protected against software access, and the firmware might access it at any time.

- LAN Configuration Space for Software. This space is used by software only. Register descriptions are listed here as a convention for the software only and are ignored by the 82573.

- Boot Expansion Space. This is accessed by software and is used by the BIOS at boot time.

A software utility based in Microsoft\* DOS called EEUPDATE was created by Intel and can be used to program EEPROM images in development or production line environments. To obtain copies of this program, contact your Intel representative.

Unless otherwise specified, all numbers in this document use the following numbering convention:

- Numbers with a suffix of "b" are binary (base 2).

- Numbers that do not have a suffix are decimal (base 10).

- Numbers with a suffix of "h" are hexadecimal (base 16).

*Note:* The 82573V and 82573L devices do not support Intel<sup>®</sup> AMT. Any references relating to Intel<sup>®</sup> AMT only apply to the 82573E.

### 1.1 Supported NVM Devices

Predecessors to the 82573 required both an EEPROM and Flash device for storing LAN data. However, the 82573 reduces the Bill of Material (BOM) cost by consolidating the EEPROM and Flash into a single non-volatile memory device. The NVM is connected to a single Serial Peripheral Interface (SPI). In addition, the 82573 reduces the BOM by enabling a solution that merges the BIOS and 82573 storage into a single shared Flash device. Shared Flash with the BIOS is valuable for Intel<sup>®</sup> AMT, ASF and basic functionality.

The 82573 is compatible with many sizes of 4-wire SPI EEPROM devices. The required EEPROM size is dependent upon the manageability platform. The 82573 accesses the EEPROM at a frequency of 2 MHz and supports EEPROM devices from STM\*, SST\*, and Chingis\*.

The 82573 can operate with an SPI Flash as a stand alone device or shared device with the system BIOS. The Flash size is selected by the system integrator according to its usage. However, a minimum 4-Mb Flash is required for Intel<sup>®</sup> AMT support.

#### Table 1. EEPROM/Flash Configuration Size

| Configuration                                    | Minimum NVM Size                                                                                                        | Memory Family |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|

| ASF or APT Manageability                         | 64 Kb                                                                                                                   | SPI EEPROM    |

| No Manageability (Intel® AMT, ASF or APT)        | 1 Kb                                                                                                                    | SPI EEPROM    |

| Shared Flash with Intel® AMT<br>(82573E only)    | 8 Mb to 16 Mb total<br>The minimum requirement for<br>Intel® AMT is 4 Mb.                                               | SPI Flash     |

| Shared Flash without Intel® AMT                  | 8 Mb to 16 Mb total for mobile<br>4 Mb to 16 Mb total for desktop<br>128 Kb (minimum) is reserved for<br>the LAN image. | SPI Flash     |

| Dedicated Flash with Intel® AMT<br>(82573E only) | 4 Mb                                                                                                                    | SPI Flash     |

| Dedicated Flash without Intel® AMT               | 128 Kb                                                                                                                  | SPI Flash     |

#### Table 2. Compatible EEPROM Parts

| Vendor    | 1 Kb              |

|-----------|-------------------|

| Atmel*    | AT25010N-10SI-2.7 |

| STM*      | 95010WMN6         |

| Catalyst* | CAT25010S         |

#### Table 3.Compatible Flash Parts

| Vendor    | 4 Mb                                          | 8 Mb                                          | 16 Mb    |

|-----------|-----------------------------------------------|-----------------------------------------------|----------|

| ST Micro* | 25PE40 <sup>1</sup> ,<br>M45PE40 <sup>2</sup> | 25PE80 <sup>1</sup> ,<br>M45PE80 <sup>2</sup> |          |

| Chingis*  | PM25LV040                                     |                                               |          |

| SST*      | 25VF040B<br>25LF040A                          | 25VF080B                                      | 25VF016B |

1. ST Micro\* parts can only be used with non-Intel® AMT Systems.

2. These parts have been fully tested but are not pin compatible with the other Flash components listed in this table.

In a shared Flash, 82573 implements SPI arbitration with the ICH. At any size, the 82573 has the following requirements from the Flash: block erase instruction of 4 KB or 256 bytes with the Flash supporting the Read Device ID instruction that enables software to identify an empty device type. The 82573 drives the Flash at a frequency of approximately 15.6 MHz and supports devices from STM\*, SST\*, and Chingis\*. (Intel is currently working with these SPI Flash vendors. More details can be obtained through your technical representative.) The following table lists existing Flash devices and their specifications.

*Note:* Additional 8 Mb and 16 Mb Flash parts will become available in early 2007 and will be validated for use with the 82573 GbE controller. Consult your local Intel representative for availability information.

#### Table 4.Specifications for Flash Devices

|                                                                            | STM* Family  | SST* Family           | Chingis* Family |

|----------------------------------------------------------------------------|--------------|-----------------------|-----------------|

| Size (bytes)                                                               | 0.5 Mb, 1 Mb | 0.5 Mb, 1 Mb,<br>2 Mb | 64 KB, 128 Kb   |

| Maximum Write<br>Burst Size<br>(Word 4Ah, bit 5)<br>Sector Size            | 256 byte     | 1 byte                | 256 bytes       |

| Minimum Block<br>Erase Size<br>(Word 12h, bits<br>3:2) Sector Size         | 256 bytes    | 4 Kb                  | 4 Kb            |

| Device Erase<br>Instruction<br>(Word 4Ah, bits<br>15:8) Sector Size        | -            | 60h                   | C7h             |

| Minimum Block<br>Erase Instruction<br>(Word 11h, bits<br>15:8) Sector Size | DBh          | 20h                   | D7h             |

### 1.2 NVM Device Detection

82573 detects the device connected on the SPI interface in two phases:

- 1. It first detects the device type by the state of the NVM Type (NVMT) strapping pin.

- 2. It looks at the NVM content depending on a valid signature in word 12h of the NVM device.

### 1.2.1 CRC Field

In ASF Mode, the 82573 ASF function reads the ASF CRC word to determine whether the EEPROM is valid. If the CRC is not valid, the ASF configuration registers retain their default value. This CRC does not affect any of the remaining 82573 configuration, including the Management Control Register.

### 1.3 Device Operation with EEPROM

When the 82573 is connected to an external EEPROM it provides similar functionality to its predecessors with the following enhancements:

- Enables a complete parallel interface for reads and writes to the EEPROM.

- Enables software to explicitly specify the address length, eliminating the need for bit clocking accesses even with an empty EEPROM.

### 1.4 Device Operation with Flash

The 82573 merges the legacy EEPROM and Flash content in a single Flash device. This mechanism provides a seamless backwards compatible interface for the software and firmware to the legacy EEPROM space. This also enables the 82573 to share the BIOS content with the LAN content on the same device at separate regions.

The 82573 supports Flash devices with block erase size of 256 bytes and 4 Kb. The 82573 firmware relates to logical sectors of 4 Kb regardless of the block erase size.

*Note:* Many Flash vendors use the term sector differently. For purposes of this document, the term Flash sector refers to a logic section of 4 Kb.

In a shared Flash, the LAN data and BIOS content reside side by side. Each entity spans across non-overlapping regions and sectors. The BIOS is located at the top of the Flash and the LAN content is located at the bottom of the Flash. Figure 1 shows the Flash memory mapping of LAN and BIOS regions.

#### 1.4.1 Shadow RAM

The 82573 uses shadow RAM to minimize the number of times the Flash is read. The Flash is read once into shadow RAM at power up and is not read again until the next power up. During normal operation and when the 82573 resumes from any Sx state, the shadow RAM is used instead of the Flash.

#### Figure 1. Flash Mapping of the LAN and BIOS Regions

### 1.5 **EEPROM Mode**

When an external EEPROM is present any access to the EEPROM interface is directed to the external EEPROM device.

### 1.6 NVM Clients

Several client systems can access the NVM through their software driver, BIOS, firmware and hardware. Table 5 lists the systems and their interfaces.

#### Table 5.NVM Client Interface

| Client & Interface                 | NVM Port | NVM Instruction                                                                      |

|------------------------------------|----------|--------------------------------------------------------------------------------------|

| Host CPU on EEC CSR                | EEPROM   | Legacy bit clocking.                                                                 |

| Host CPU on EERD and EEWR          | EEPROM   | Parallel word read and write to EEPROM (controlled by the EEC.SELSHAD bit).          |

| MNG on EEMNG CSR                   | EEPROM   | Parallel word read and write to EEPROM.                                              |

| Host CPU on FLA CSR                | Flash    | Flash erase instructions (only for non-protected Flash). <sup>1</sup> , <sup>2</sup> |

| MNG on DMA Engine                  | Flash    | Read and write DMA to the Flash and Block Erase. <sup>1</sup>                        |

| MNG via the cache                  | Flash    | Code fetch and data read. Access to FL1 and FL2 spaces.                              |

| Host CPU via BAR                   | Flash    | Read byte word and Dword and byte programming. <sup>1</sup>                          |

| Host CPU via FLSWxxx CSR registers | Flash    | Host write access to the Flash.                                                      |

| Direct hardware accesses           | Both     |                                                                                      |

1. After a write or erase instruction to the Flash, the 82573 initiates a seamless write enable before the write or erase instruction is executed and polls the status at the end to verify its completion.

2. Bit clocking access and device erase are enabled only for non-protected Flash devices.

### 1.7 Flash NVM Protection Scheme

The 82573 Flash protection protects the BIOS area and Intel<sup>®</sup> AMT in shared Flash configurations in Intel<sup>®</sup> AMT enabled systems. Systems that do not share the Flash with the ICH or include Intel<sup>®</sup> AMT functionality do not require the Flash device protection.

The 82573 Flash device is protected when a valid image has been programmed onto the device and the protection mechanism has been switched on. Once the security mechanism is invoked, it might only be overridden by setting the NVM\_PROT strapping pin to 0. A jumper can be installed to physically disable the protection. The jumper must be connected to NVM\_PROT pin A5. (The *Intel<sup>®</sup> 82573 Family of GbE Controllers Datasheet* and the *Intel<sup>®</sup> 82573/82562 Dual Footprint Design Guide* can be used for reference.)

When the Flash device is programmed by an external Flash burner for shared Flash configurations, setting word 10h bits 5:4 to 11b ensures the protection mechanism is enabled. Bit 4 enables the Flash vendor identification, which adapts the image according to the installed Flash part, and bit 5 enables the protection.

The EEUPDATE program can be used to program a blank Flash when it is not protected using the No Protection (NoProt) flag. The No Protection flag disables protection.

The BADDR value in word 11h enables BIOS protection on shared Flash configurations. This value sets the highest address that the LAN device might read or write. BADDR should be set to the highest address of the LAN image on a protection enabled Flash image.

When the Flash is protected, the legacy LAN image, except word 10h, 11h, and 12h, can be updated using the EEUPDATE tool. EEUPDATE does not have the ability to modify the Intel<sup>®</sup> AMT Flash component. This is updated using the Intel<sup>®</sup> AMT network interface through the tftp server or the Intel<sup>®</sup> AMT Firmware Update tool (available in the 82573E software release).

#### Table 6.Protected Spaces

| Space                                      | Conditions                                                                             | Protected Space Behavior                                                                                                                                              |  |

|--------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device Protected                           | NVPROTN 12h[4] = 0<br>NVM_PROT samples 1<br>NVM Signature is valid<br>12h[15:8] = 7Eh  | Legacy bit clocking is disabled. The Flash Erase is not<br>propagated to the Flash. Protected spaces are enabled<br>and some CSR are read only.                       |  |

| Words 11h and 12h                          | Device Protected                                                                       | Host software or firmware cannot write to these addresses in the EEPROM, Flash S0, Flash S1, or Shadow RAM.                                                           |  |

| Word 10h                                   | Device Protected                                                                       | Host software cannot write to this address in the EEPROM, Flash S0, Flash S1, or Shadow RAM.                                                                          |  |

| Intel® AMT<br>Protected Space <sup>1</sup> | Device Protected<br>PEND 10h is not equal to 0<br>NVM_Type samples 0<br>(equals Flash) | For the 82573E, host software cannot access (read or write) this area of protected space. This space is defined by PSTART and PEND fields in word 10h.                |  |

| BIOS Protected<br>Space                    | Device Protected<br>BADDR is not equal to 0<br>NVM_Type samples 0<br>(equals Flash)    | Host software and firmware cannot access (read or<br>write) any address above BADDR. BADDR is valid for<br>shared Flash with the BIOS as well as non-shared<br>setup. |  |

1. This protected space is defied only by Intel® AMT mode (all other spaces might exist at any operation mode). At this mode the PEND pointer in the NVM word 10h should have a valid (null) value while the PSTART pointer in the same location defines the beginning of the Intel® AMT protected space. In ASF mode, the PEND should have a null value while the PSTART defines the starting address of the ASF space.

#### Figure 2. NVM Protected Space Mapping

### 1.7.1 Initial Programming for Shared Flash with ICH

The Flash device should be programmed using an external Flash burner. The image must be combined including the LAN and BIOS components. The LAN image programmed using the external burner should have word 10h bit 4 set to 1b. This ensures that firmware identifies the Flash device and re-configures the image accordingly when the 82573 powers up from the default image (no Flash vendor specific configuration). Setting word 10h bit 5 to 1b enables the Flash protection mechanism.

For the 82573E, in a shared Flash configuration, the Intel<sup>®</sup> AMT component cannot be updated or modified using tools such as EEUPDATE after the initial programming cycle. The Intel<sup>®</sup> AMT component can only be updated using the firmware update application.

#### 1.7.2 Initial Programming for Non-Shared Configurations

EEUPDATE can be used to program a blank Flash and update a valid Flash image. EEUPDATE is unable to update a Flash image if protection has been enabled without installing an override jumper.

### **1.8 EEUPDATE Utility**

Intel has created a DOS\* utility that meets the two basic requirements for an in-circuit programming utility. First, the utility can be used to update EEPROM images as part of an end-of-line production tool. Secondly, it can be used as a standalone development tool. The tool uses the two basic data files outlined in the following section (static data file and IA address file). To obtain a copy of this program, contact your Intel representative.

The EEUPDATE utility is flexible and can be used to update the entire EEPROM image or update only the IA address of the 82573.

*Note:* EEUPDATE can only be used to program the image in non-shared mode. Programming in shared mode requires the use of an external programmer.

#### 1.8.1 Command Line Parameters

The DOS\* command format is a follows:

**EEUPDATE** Parameter\_1 Parameter\_2 Parameter 3

where:

Parameter\_1 = filename or /D

Parameter\_2 = filename or /A

Parameter\_3 = /noprot

Parameter 1, in this example case, is file1.eep, which contains the complete EEPROM image in a specific format that is used to update the complete EEPROM. All comments in the .eep file must be preceded by a semicolon (;).

Parameter 1 can also be a switch, "/D." The switch /D means, "Do not update the complete EEPROM image."

Parameter 2, in this example case, is file2.dat, which contains a list of IA addresses. the EEUPDATE utility picks up the first unused address from this file and uses it to update the EEPROM. An address is marked as used by following the address with a date stamp. When the utility uses a specific address, it updates that address as used in a log file called eelog.dat. This file should then be used as the .dat file for the next update.

Parameter 2 can also be a switch, "/A." The switch /A implies, "Do not update the IA address."

The following flags are defined as follows:

/D <imagefile> or /DATA <imagefile>

This programs the EEPROM with the contents of <imagefile> without changing the MAC address.

/A <addrfile> or /address <addrfile>

This programs the EEPROM with only the MAC address from the <addrfile> without changing the rest of the EEPROM.

/NOPROT

This disables protection while an image is being programmed. This switch has no effect if it is not used with the /data command.

See Appendix A for an example of the raw EEPROM contents.

## 2.0 NVM Memory Map

The NVM contains two regions located at fixed addresses and various regions located at programmable addresses throughout the physical NVM space.

The NVM base area resides at word addresses 00h through 3Fh. All defined fields are fixed, while reserved words can be used by programmable areas. The base area is present in the NVM of all system configurations. Words 10h through 12h of the base area are protected.

The base area at 40h to 4Fh contains additional configuration that is applicable and loaded only when the Base Area 40h bit is set in Initialization Control Word 1. This area has fixed locations for its fields and contains Flash and Intel<sup>®</sup> AMT (for the 82573E device only) configuration data.

The programmable areas are as follows:

- An optional Preboot eXecutable Environment (PXE) configuration area resides in word addresses 30h to 3Fh of the base area. A pointer at address 3Dh indicates the Boot Configuration area.

- These words within the base area provide a pointer to the optional manageability area, which can serve either ASF or Intel<sup>®</sup> AMT. (Intel<sup>®</sup> AMT is only available on the 82573E.)

- When the 82573E/V is configured to ASF mode in the Management Capabilities word, the Start Address (PSTART) points to the beginning of the ASF configuration area.

- When the 82573E is configured for Intel<sup>®</sup> AMT in the Management Capabilities word, the Start Address (PSTART) points to the beginning of the Intel<sup>®</sup> AMT programmable configuration area. The Base Area 40h is also enabled and loaded when Intel<sup>®</sup> AMT is enabled. The BADDR field in the protected area indicates the beginning of the BIOS code. This field is relevant only in a shared NVM configuration.

### 2.1 Basic Configuration Table

The following table lists the NVM map for words 00h through 3Fh of the 82573. Each word listed is described in the sections that follow.

| Word       | Used<br>By | High Byte<br>Bits 15:8                                                     | Low Byte<br>Bits 7:0                               |  |  |  |  |

|------------|------------|----------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| 00h<br>01h | HW<br>HW   | Ethernet Address Byte 2<br>Ethernet Address Byte 4                         | Ethernet Address Byte 1<br>Ethernet Address Byte 3 |  |  |  |  |

| 02h        | HW         | Ethernet Address Byte 6                                                    | Ethernet Address Byte 5                            |  |  |  |  |

| 03h        |            |                                                                            |                                                    |  |  |  |  |

| 04h<br>05h |            | Compatibility High                                                         | Compatibility Low                                  |  |  |  |  |

| 06h        |            | oompatizinty mgn                                                           | companionity zon                                   |  |  |  |  |

| 07h        |            |                                                                            |                                                    |  |  |  |  |

| 08h<br>09h | SW         | PBA, byte 1<br>PBA, byte 3                                                 | PBA, byte 2<br>PBA, byte 4                         |  |  |  |  |

| 0Ah        | HW         |                                                                            | ion Control 1                                      |  |  |  |  |

| 0Bh        | НW         |                                                                            | n ID (Vendor)                                      |  |  |  |  |

| 0Ch        | HW         |                                                                            | m Vendor ID                                        |  |  |  |  |

| 0Dh        | HW         |                                                                            | vice ID                                            |  |  |  |  |

| 0Eh        | HW         |                                                                            | dor ID                                             |  |  |  |  |

| OFh        | HW         |                                                                            | ion Control 2                                      |  |  |  |  |

| 10h        | HW         |                                                                            | d 0 (NVM0)                                         |  |  |  |  |

| 11h        | HW         |                                                                            | d 0 (NVM0)                                         |  |  |  |  |

| 12h        | HW         |                                                                            | d 2 (NVM2)                                         |  |  |  |  |

| 13h        | HW         |                                                                            |                                                    |  |  |  |  |

| 14h        | HW         | Management Enable Management Capabilities<br>Extended Configuration Word 1 |                                                    |  |  |  |  |

|            |            |                                                                            | -                                                  |  |  |  |  |

| 15h        | HW         |                                                                            | figuration Word 2                                  |  |  |  |  |

| 16h        | HW         | Extended Configuration Word 3 Reserved Memory Scrub Control                |                                                    |  |  |  |  |

| 17h        | HW         |                                                                            |                                                    |  |  |  |  |

| 18h        | HW         | PCI Express* (PCIe*) Initial Configuration 1                               |                                                    |  |  |  |  |

| 19h        | HW         | PCIe Initial Configuration 2                                               |                                                    |  |  |  |  |

| 1Ah        | HW         |                                                                            | Configuration 3                                    |  |  |  |  |

| 1Bh        | HW         |                                                                            | Control                                            |  |  |  |  |

| 1Ch        | HW         | PHY Configuration                                                          | LEDCTL 1 Default                                   |  |  |  |  |

| 1Dh        | HW         |                                                                            | served                                             |  |  |  |  |

| 1Eh        | HW         | Device F                                                                   | Revision ID                                        |  |  |  |  |

| 1Fh        | HW         | LEDCTL 0                                                                   | and 2 Default                                      |  |  |  |  |

| 20h        | HW         | Firmv                                                                      | Firmware Bits                                      |  |  |  |  |

| 21h        |            | Res                                                                        | served                                             |  |  |  |  |

| 22h        | HW         | LAN Power Consumption                                                      |                                                    |  |  |  |  |

| 23h        | SW         | Flash Softw                                                                | vare Detection                                     |  |  |  |  |

| 24h        | нw         | Initializati                                                               | on Control 3                                       |  |  |  |  |

### Table 7.82573 NVM Map for Address Range 00h to 3Fh (Sheet 1 of 2)

| Word | Used<br>By | High Byte<br>Bits 15:8 | Low Byte<br>Bits 7:0  |

|------|------------|------------------------|-----------------------|

| 25h  |            |                        |                       |

| 26h  |            |                        |                       |

| 27h  |            |                        |                       |

| 28h  |            |                        |                       |

| 29h  |            |                        |                       |

| 2Ah  |            | Rese                   | erved                 |

| 2Bh  |            |                        |                       |

| 2Ch  |            |                        |                       |

| 2Dh  |            |                        |                       |

| 2Eh  |            |                        |                       |

| 2Fh  |            |                        |                       |

| 30h  |            | PXE Word 0 (Softwar    | re Use) Configuration |

| 31h  |            | PXE Word 1 (Softwar    | e Use) Configuration  |

| 32h  |            | PXE Word (Softwar      | e Use) PXE Version    |

| 33h  | PXE        | PXE Word (Softwar      | re Use) EFI Version   |

| 34h  |            | PXE                    | Word                  |

|      |            |                        |                       |

| 3Eh  |            | PXE                    | Word                  |

| 3Fh  |            | Software Checksum, v   | vords 00h through 3Fh |

#### Table 7.82573 NVM Map for Address Range 00h to 3Fh (Sheet 2 of 2)

### 2.1.1 Ethernet Address (Words 00h-02h)

The Ethernet Individual Address (IA) is a six-byte field that must be unique for each Ethernet port and unique for each copy of the NVM image. The first three bytes are vendor specific. The value from this field is loaded into the Receive Address Register 0 (RALO/RAH0). An example is provided in the table below for the Ethernet address of: 12 34 56 78 90 ABh.

#### Table 8.MAC Address Example

| Word | Value Loaded |

|------|--------------|

| 0    | 3412h        |

| 1    | 7856h        |

| 2    | AB90h        |

*Note:* The values are byte-swapped.

## 2.1.2 Compatibility Field (Word 03h-07h)

This area is reserved for compatibility information to be used by software drivers.

### Table 9.Compatibility Field (Word 03h)

| Bit   | Name               | Default | Description                                                                                                                                                             |

|-------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13 | Reserved           | 000b    | These bits are reserved and should be set to 000b.                                                                                                                      |

| 12    | ASF SMBus Connect  |         | This bit identifies whether or not the ASF SMBus is connected.<br>Ob = ASF SMBus is not connected.<br>1b = ASF SMBus is connected.                                      |

| 11    | LOM Design         |         | This bit identifies whether or not the implementation is a LAN on<br>Motherboard (LOM) design or not.<br>Ob = Network Interface Card (NIC)<br>1b = LOM design (default) |

| 10    | Server NIC         |         | This bit identifies whether or not the system is a server or a client.<br>0b = Client<br>1b = Server                                                                    |

| 9     | Client NIC         |         | This bit identifies whether or not the system is a server or a client.<br>Ob = Server<br>1b = Client                                                                    |

| 8     | Retail/OEM         |         | This bit identifies a retail or OEM status.<br>Ob = Retail<br>1b = OEM                                                                                                  |

| 7:6   | Reserved           |         | These bits are reserved and should be set to 0b.                                                                                                                        |

| 5     | Reserved           |         | This bit is reserved and should be set to 1b.                                                                                                                           |

| 4     | SMB Connect        |         | This bit identifies whether or not the SMB is connected.<br>Ob = SMB is not connected.<br>1b = SMB is connected.                                                        |

| 3     | Reserved           |         | This bit is reserved and should be set to 0b.                                                                                                                           |

| 2     | PCI Bridge Present |         | This bit identifies whether or not a PCI bridge is present.<br>Ob = PCI bridge is not present.<br>1b = PCI bridge is present.                                           |

| 1:0   | Reserved           |         | These bits are reserved and should be set to 00b.                                                                                                                       |

### Table 10. Compatibility Field (Word 04h)

| Bit   | Name          | Default | Description                                         |

|-------|---------------|---------|-----------------------------------------------------|

| 15:12 | Reserved      |         | These bits are reserved and should be set to 0000b. |

| 11:8  | LED 2 Control |         | This field is the control for LED 2.                |

| 7:4   | LED 1 Control |         | This field is the control for LED 1.                |

| 3:0   | LED 0 Control |         | This field is the control for LED 0.                |

### Table 11.Compatibility Field (Word 05h)

| Bit  | Name                    | Default | Description                                                 |

|------|-------------------------|---------|-------------------------------------------------------------|

| 15:8 | EEPROM Major<br>Version |         | This field contains the major version number of the EEPROM. |

| 7:0  | EEPROM Minor<br>Version |         | This field contains the minor version number of the EEPROM. |

### Table 12. Compatibility Field (Word 06h)

| Bit  | Name              | Default | Description                              |

|------|-------------------|---------|------------------------------------------|

| 15:0 | OEM Configuration |         | This word is used for OEM configuration. |

### Table 13. Compatibility Field (Word 07h)

| Bit  | Name              | Default | Description                              |

|------|-------------------|---------|------------------------------------------|

| 15:0 | OEM Configuration |         | This word is used for OEM configuration. |

### 2.1.3 PBA Number (Word 08h-09h)

A nine-digit Printed Board Assembly (PBA) number, used for Intel manufactured NICs, are stored in a four-byte field. Other hardware manufacturers can use these fields as desired. Network driver software should not rely on this field to identify the product or its capabilities.

### 2.1.4 Initialization Control Word 1 (Word 0Ah)

This is the first word read by the 82573 and contains initialization values that:

- Set defaults for some internal registers.

- Enable/disable specific features.

- Determine which PCI configuration space values are loaded from the NVM.

### Table 14. Initialization Control Word 1 (Word 0Ah) (Sheet 1 of 2)

| Bit | Name                                | Default | Description                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Link Status Change<br>Wake Enable   | Ob      | This bit enables wake on link status change as part of APM wake capabilities.<br>It is not read automatically by the hardware. Software reads the NVM and writes it to hardware.                                                                                                                                                                    |

| 14  | Link Status Change<br>Wake Override | Ob      | If this bit equals 1b, the wake on link status change does not<br>depend on the LNKC bit of the Wake Up Filter Control Register<br>(WUFC). The wake on link status change is determined by the APM<br>settings in the Wake Up Register.<br>This bit is not read automatically by the hardware. Software reads<br>the NVM and writes it to hardware. |

| 13  | Base Area 40h                       | 1b      | When this bit is set, it indicates that the Base Area starting at address 40h must be loaded from the NVM.                                                                                                                                                                                                                                          |

| 12  | Reserved                            | 0b      | This bit is reserved and must be set to 0b.                                                                                                                                                                                                                                                                                                         |

| 11  | FRCSPD                              | Ob      | This bit reflects the Force Speed bit in the device Control Register (CTRL[11]). When it is set to 1b, the speed is forced. When it is 0b, it does not force speed.                                                                                                                                                                                 |

| 10  | FD                                  | Ob      | This bit reflects the duplex setting. It is mapped to the Control Register bit 0. It has a hardware reset value of 1b. When it is set to 1b, full duplex is enabled. When it is set to 0b, full duplex is disabled.                                                                                                                                 |

| 9   | Reserved                            | 1b      | This bit is reserved and should be set to 1b.                                                                                                                                                                                                                                                                                                       |

| 8:7 | Reserved                            | 00b     | These bits are reserved and should be set to 0bb.                                                                                                                                                                                                                                                                                                   |

| 6   | Mask g_fnc_tar_g<br>MSB             | 1b      | When this bit is set to 1b, the most significant bit of g_fnc_tar_g is masked by the EEPROM or Flash.                                                                                                                                                                                                                                               |

#### Table 14. Initialization Control Word 1 (Word 0Ah) (Sheet 2 of 2)

| Bit | Name                      | Default | Description                                                                                                                                                                                                                                                                |

|-----|---------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | Reserved                  | 1b      | This bit is reserved and should be set to 1b.                                                                                                                                                                                                                              |

| 4   | ILOS                      | Ob      | This bit represents the default setting for the loss of signal polarity setting of Control Register bit 7. The hardware default value is 0.                                                                                                                                |

| 3   | Power Management          | 1b      | When this bit is set to 1b (default), full support for power<br>management is enabled.<br>When it is set to 0b, the power management register settings are<br>read only, and the 82573 does not execute a hardware transition to<br>D3.                                    |

| 2   | Reserved                  | 0b      | This bit is reserved and should be set to 0b.                                                                                                                                                                                                                              |

| 1   | Load Subsystem<br>IDs     | 1b      | When this bit is set to 1b (default), it indicates that the device<br>needs to load its PCIe) Subsystem ID and Subsystem Vendor ID<br>from the NVM (words 0Bh and 0Ch).<br>When it is set to 0b, the device loads the default PCI Subsystem ID<br>and Subsystem Vendor ID. |

| 0   | Load Vendor/Device<br>IDs | 1b      | When this bit equals 1b, the device loads the default values for PCIe Vendor and Device IDs from the NVM (words 0Dh and 0Eh).                                                                                                                                              |

### 2.1.5 Subsystem ID (Word 0Bh)

If Load Subsystem IDs bit of word 0Ah is valid, this word is read in to initialize the Subsystem ID. The Subsystem ID default value is 0h.

### 2.1.6 Subsystem Vendor ID (Word 0Ch)

If Load Subsystem IDs bit of word 0Ah is valid, this word is read in to initialize the Subsystem Vendor ID. The Subsystem Vendor ID default value is 8086h.

### 2.1.7 Device ID (Word 0Dh)

If the Load Vendor/Device IDs bit in word 0Ah is set, this word is read to initialize the Device ID of the LAN function. 108Bh is used for a basic 82573 based design, and 108Ch for a design based on the 82573E with Intel<sup>®</sup> AMT.

#### Table 15. Device ID Values

| Vendor ID | Device ID | String Name                                                                                    |

|-----------|-----------|------------------------------------------------------------------------------------------------|

| 8086h     | 108Bh     | Intel <sup>®</sup> PRO/1000 PM Network Connection (82573 based design)                         |

| 8086h     | 108Ch     | Intel $^{\textcircled{B}}$ PRO/1000 PM Network Connection (82573E based design with Intel AMT) |

| 8086h     | 109Ah     | Intel <sup>®</sup> PRO/1000 PM Network Connection (82573L based design)                        |

*Note:* The Vendor ID for Intel is always 8086h.

### 2.1.8 Vendor ID (Word 0Eh)

If the Load Vendor/Device IDs bit in word 0Ah is set, this word is read to initialize the Vendor ID. The default Vendor ID value is 8086h.

### 2.1.9 Initialization Control Word 2 (Word 0Fh)

This is the second word read by the 82573 and contains additional initialization values that:

- Set defaults for some internal registers.

- Enable or disable specific features.

#### Table 16.Initialization Control Word 2 (Word 0Fh)

| Bit   | Name                                        | Default               | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | APM PME# Enable                             | 1b                    | This bit reflects the initial value of the Assert PME On APM Wakeup bit in the Wake Up Control Register (WUC.APMPME). When it is set to 0b, PME# is de-asserted on wakeup.                                                                                                                                                                                                                                                        |

| 14    | Reserved                                    | 0b                    | This bit is reserved and should be set to 0b.                                                                                                                                                                                                                                                                                                                                                                                     |

| 13:12 | NVMTYPE                                     | OOb                   | These bits indicate the type of NVM present.<br>00b = EEPROM<br>01b = Stand alone Flash<br>10b = SPI Flash<br>11b = Reserved                                                                                                                                                                                                                                                                                                      |

| 11:8  | NVSIZE                                      | 0000b                 | When the NVM is a Flash device, the NVSIZE should be greater than or equal to 9 (the minimum supported Flash size is 64 KB).                                                                                                                                                                                                                                                                                                      |

| 7     | CLK_CNT_1_4                                 | 1b                    | This bit enables the automatic reduction of the DMA frequency. It is mapped to the Status Register bit 30.                                                                                                                                                                                                                                                                                                                        |

| 6     | PHY Power Down<br>Enable                    | 1b                    | When this bit is set, the PHY can enter a low power state.                                                                                                                                                                                                                                                                                                                                                                        |

| 5     | MAC_CSR_MNG                                 | Ob                    | When this bit is set, the mng_mac_csr FSM is reset on IN_BAND PCIe* reset or PERST. When it is cleared, the FSM is reset on a soft reset.                                                                                                                                                                                                                                                                                         |

| 4     | CCM PLL Shutdown<br>Enable                  | 1b                    | When this bit is set, the CCM PLL shuts down in low power states<br>when the PHY is in power down mode (for example, during a link<br>disconnect). When it is cleared, the CCM PLL does not shut down in<br>a low power state.                                                                                                                                                                                                    |

| 3     | DMA Dynamic<br>Gating Enable                | 1b                    | When this bit is set, dynamic clock gating of the DMA and MAC units is enabled.                                                                                                                                                                                                                                                                                                                                                   |

|       |                                             |                       | For the 82573L, a value of 1b indicates that the device supports the removal of any reference clocks when the link is in the L1 and L2/3 ready link states. A value of 0b indicates that the device does not have this capability; therefore, reference clocks must not be removed in these link states.                                                                                                                          |

| 2     | Clock Power<br>Management                   | Ob                    | This feature is only applicable in designs that support the clock request signal (CLKREQ#). For a multi-function device, each function indicates its capability independently. Power management configuration software must only permit reference clock removal if all functions of the multi-function device indicate a 1b in this bit.<br><b>Note:</b> For the 82573E and 82573V, this bit is reserved and should be set to 1b. |

| 1     | Wake DMA Dynamic<br>Clock Gating<br>Disable | 1b                    | When this bit is set, dynamic clock gating of the wake DMA clock is disabled in the D0a state with wakeup enabled or MNG enabled or in the auto-read process.                                                                                                                                                                                                                                                                     |

| 0     | D0a DMA Dynamic<br>Clock Gating<br>Disable  | 0b<br>1b <sup>1</sup> | When this bit is set, dynamic clock gating of the DMA clock in the D0a state is disabled.                                                                                                                                                                                                                                                                                                                                         |

1. 82573E/V only.

## 2.1.10 NVM Word 0: NVM0 (Word 10h)

*Note:* NVMO is used by Intel<sup>®</sup> AMT and is not applicable to the 82573V and 82573L devices.

## Table 17.NVM Word 0 (Word 10h)

| Bit  | Name                                  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | PEND                                  | 00h     | This field defines the end of the protected space plus one. The address is defined as:<br>Protected End Word Address = 4 KB * PEND.<br>A zero value is a null pointer, which means that the space defined by PSTART and PEND is not protected. A value of one is invalid.                                                                                                                                                              |

| 7    | ICH7 (Check for<br>Intel AMT Disable) | Ob      | This firmware configuration bit is only for the A1 stepping of the device and is not accessed by hardware. For the A3 silicon, this bit must be set to 0b.<br>1b = ICH7 check for Intel® AMT mode disable.<br>0b = ICH7 check for Intel® AMT mode enable.                                                                                                                                                                              |

| 6    | Ignore Intel AMT<br>Skew              | Ob      | This firmware configuration bit is only for the A1 stepping of the device and is not accessed by hardware. For the A3 silicon, this bit must be set to 0b.<br>1b = Ignore Intel® AMT SKU.<br>0b = Don't ignore Intel® AMT SKU.                                                                                                                                                                                                         |

| 5    | FW Protect Image                      | 1b      | This bit should be set when the initial programming is done on an external burner. This setting is used in conjunction with bit 4, Firmware Flash Vendor Identification. If bit 4 equals 0b, this bit is ignored.<br>0b = No protection.<br>1b = Firmware enables protection at first power up.                                                                                                                                        |

| 4    | FW Flash Vendor<br>Identification     | Ob      | This bit determines whether the 82573 identifies the Flash and<br>updates the image with appropriate opcodes. This bit should be set<br>when the initial programming is done on an external burner.<br>Ob = 82573 does not perform Flash Identification.<br>1b = 82573 performs Flash Identification at power up.<br>The 82573 automatically clears this bit at the end of the Flash ID<br>sequence so that it is only performed once. |

| 3:2  | MNGM                                  | OOb     | This field selects one of the manageability operation modes.<br>00b = MNG disable mode (clock gated)<br>01b = ASF mode<br>10b = Pass through mode<br>11b = Intel® AMT mode <sup>1</sup>                                                                                                                                                                                                                                                |

| 1:0  | PSTART                                |         | The protected start address field is used in Intel® AMT mode to<br>define the starting address for this mode (PEND ≠ zero).<br>00b = Reserved<br>01b = 4 Kword<br>10b = Reserved<br>11b = Reserved<br>In ASF mode, the PSTART defines the starting address of the ASF<br>space (PEND = Zero).<br>00b = Word 40h<br>01b = Word 80h<br>10b = Reserved<br>11b = Reserved                                                                  |

1. When Intel® AMT is enabled, all MNG functions (KCS, Serial, IDE) should be enabled in word 49h of the NVM.

### 2.1.11 NVM Word 1: NVM1 (Word 11h)

#### Table 18.NVM Word 1 (Word 11h)

| Bit  | Name   | Default        | Description                                                                                                                                               |

|------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | FSECER | 1111b<br>1111b | This field defines the instruction code for the block erase used by<br>the 82573. The erase block size is defined by the SECSIZE field in<br>address 12h. |