# Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Family

**Specification Update**

May 2012

**Notice:** The Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

Document Number: 319974-016

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINCEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

This document contains information on products in the design phase of development.

All products, platforms, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. All dates specified are target dates, are provided for planning purposes only and are subject to change.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Family chipset component may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel<sup>®</sup> Active Management Technology requires activation and a system with a corporate network connection, an Intel® AMT-enabled chipset, network hardware and software. For notebooks, Intel AMT may be unavailable or limited over a host OS-based VPN, when connecting wirelessly, on battery power, sleeping, hibernating or powered off. Results dependent upon hardware, setup and configuration. For more information, see www.intel.com/technology/platform-technology/intel-amt/

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit http://www.intel.com/go/virtualization

No computer system can provide absolute security under all conditions. Intel<sup>®</sup> Trusted Execution Technology (Intel<sup>®</sup> TXT) requires a computer system with Intel Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). The MLE could consist of a virtual machine monitor, an OS or an application. In addition, Intel TXT requires the system to contain a TPM v1.s. For more information, see http://www.intel.com/technology/security

Intel<sup>®</sup> High Definition Audio requires an Intel<sup>®</sup> HD Audio enabled system. Consult your PC manufacturer for more information. Sound quality will depend on equipment and actual implementation. For more information about Intel<sup>®</sup> HD audio, refer to http://www.intel.com/

Intel, Intel logo, Intel SpeedStep, and Intel vPro are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008 - 2012, Intel Corporation. All rights reserved.

# Contents

| Preface                                         | 7  |

|-------------------------------------------------|----|

| Summary Tables of Changes                       | 8  |

| Identification Information                      | 11 |

| Intel® ICH10 Device and Revision Identification |    |

| Errata                                          |    |

| Specification Changes                           |    |

| Specification Clarifications                    |    |

| Document Changes                                |    |

# **Revision History**

| Revision                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                | Date          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

| -016                                                                                                                                                     | Added Item:<br>- Errata: 19- Incorrect IRQ(x) Vector Returned for 8259 Interrupts With RAEOI Enabled<br>- Specification Change: 1- ROAEI options removal for OCW2                                                                                                                                                                                                                                                                          | May 2012      |  |  |

| -015                                                                                                                                                     | Added Items:<br>- Document Changes: 20- Correct OUTSTRMPAY Register information<br>- Document Changes: 21 - Correct INSTRMPAY Register information                                                                                                                                                                                                                                                                                         | December 2011 |  |  |

| -014                                                                                                                                                     | Added Items:<br>- Errata: 18 Intel <sup>®</sup> ICH10 SATA GEN3 Device Detection<br>- Errata: 16 Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family HPET Write Timing                                                                                                                                                                                                                                                                 | February 2011 |  |  |

| -013                                                                                                                                                     | Added Items:<br>- Document Changes: 19-Update Section 8.2 in the Datasheet<br>- Errata: 18 Intel <sup>®</sup> ICH10 SATA GEN3 Device Detection                                                                                                                                                                                                                                                                                             | December 2010 |  |  |

| -012                                                                                                                                                     | Added Items:<br>- Errata: 17 Intel <sup>®</sup> ICH10 Corporate May Not Detect Unsolicited SATA COMINITs<br>- Document Changes: 18 - Correct A20M# Signal Description                                                                                                                                                                                                                                                                      | November 2010 |  |  |

| -011                                                                                                                                                     | Added Items:<br>- Document Changes: 17-Correct Section 13.1.23 Bits 15:2 definition                                                                                                                                                                                                                                                                                                                                                        | May 2010      |  |  |

| -010                                                                                                                                                     | -010       Added Items:         -010       - Errata: 16 Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family HPET Write Timing         - Document Changes: 16- Correct Section 10.1.45 Bit 0 definition         -009         -009         -Errata 15 Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family SATA SYNC Escape                                                                                                           |               |  |  |

| -009                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |  |  |

| -008                                                                                                                                                     | Added Items:<br>- Errata: 14- Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family PCI Express Function Disable<br>-Document Changes: 15- Correct Section 5.13.6.5 Sx-G3-Sx, Handling Power Failures<br>regarding wake events following a power failure                                                                                                                                                                                 | August 2009   |  |  |

| -007                                                                                                                                                     | Added Items:<br>- Errata: 13- Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family SATA Low Power Device Detection<br>-Document Changes: 13 -Correct SMBCLK_CTL bit default value 14 - Correct Table 2-24 Strap<br>selection for Boot BIOS Destination                                                                                                                                                                                  | July 2009     |  |  |

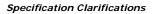

| -006                                                                                                                                                     | Added Items:<br>Corrected Device ID for D30:F0 in Table 2-27 ICH10 Consumer Device and Rev ID Table<br>Document Changes:<br>9- Remove GPI058 from Figure 2-1 Intel <sup>®</sup> ICH10 Interface Signals Block Diagram. 10- Add<br>1.1v for VccDMI in Table 2-24.<br>11-Correct Bit Types for PCI Express UnCorrectable Error Severity register (UEV) Corporate<br>ICH10. 12- Correct PCI Express DSTS register definition for bit 1 (NFED) | April 2009    |  |  |

| -005 Added Items:<br>Document Change: 8- Add foot note for all references to SPI Flash descriptors<br>MCHSTRP0                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                            | February 2009 |  |  |

| -004 Added Items:<br>-004 Document Changes: 6- Make correction to Table 5-40 Causes of Host and Global Resets<br>Update bit definition for SECOND_TO_STS |                                                                                                                                                                                                                                                                                                                                                                                                                                            | January 2009  |  |  |

| Revision | Description                                                                                                                                                                                                                                                       | Date           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -003     | Added Items:<br>Document Changes: 1-Add GPIO Reset Notes, 2- Correct EOIFD bit definition, 3- Correct<br>GPI_INV -GPIO Signal Invert register definition 4- Update TBD defaults. 5 Update GPIO Note<br>#4 in Section 3.2 Output and I/O Signals Planes and States | December 2008  |

| -002     | Added Intel ICH10 Corporate components<br>- Intel 82801JD ICH10 Corporate Base (ICH10D)<br>- Intel 82801JDO ICH10 Digital Office (ICH10DO)<br>Added Errata 7-12.                                                                                                  | September 2008 |

| -001     | Initial Release.                                                                                                                                                                                                                                                  | June 2008      |

ICH10—Revision History

## Preface

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

## **Affected Documents/Related Documents**

| Title                                                             | Document<br>Number |

|-------------------------------------------------------------------|--------------------|

| Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family Datasheet | 319973             |

### Nomenclature

**Errata** are design defects or errors. Errata may cause the ICH10's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present in all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# **Summary Tables of Changes**

The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the ICH10 product family. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables uses the following notations:

## **Codes Used in Summary Tables**

## Stepping

|        | X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|

|        | (No mark)       |                                                                                                               |

|        | or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| Page   |                 |                                                                                                               |

|        | (Page):         | Page location of item in this document.                                                                       |

| Status |                 |                                                                                                               |

|        | Doc:            | Document change or update will be implemented.                                                                |

|        | Plan Fix:       | This erratum may be fixed in a future stepping of the product.                                                |

|        | Fixed:          | This erratum has been previously fixed.                                                                       |

|        | No Fix:         | There are no plans to fix this erratum.                                                                       |

| _      |                 |                                                                                                               |

## Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

| Erratum | Step           | Stepping        |                                              |                                                                                                                                            |

|---------|----------------|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Number  | A0<br>Consumer | B0<br>Corporate | Status                                       | ERRATA                                                                                                                                     |

| 1       | х              |                 | No Fix                                       | Intel $^{\circledast}$ I/O Controller Hub 10 (ICH10) Consumer Family UHCI Hang with USB Reset                                              |

| 2       | х              |                 | No Fix                                       | Intel $^{\textcircled{B}}$ I/O Controller Hub 10 (ICH10) Consumer Family THRM Polarity on SMBus                                            |

| 3       | х              |                 | No Fix                                       | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family High Speed (HS) USB 2.0 D+ and D- Maximum Driven Signal Level             |

| 4       | х              |                 | No Fix                                       | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family PET Alerts on SMBus                                                       |

| 5       | х              |                 | No Fix                                       | Intel $^{\ensuremath{\mathbb{R}}}$ I/O Controller Hub 10 (ICH10) Consumer Family SMBus Host Controller May Hang                            |

| 6       | х              |                 | No Fix<br>(Consumer)<br>Fixed<br>(Corporate) | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family LAN_PHY_PWR_CTRL<br>Functionality                                                  |

| 7       | Х              |                 | No Fix                                       | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family High-speed USB 2.0 $\mathrm{V}_{\mathrm{HSOH}}$                                    |

| 8       | х              |                 | No Fix                                       | Intel $^{\ensuremath{\mathbb{R}}}$ I/O Controller Hub 10 (ICH10) Family 1.5 Gb/s SATA Signal Voltage Level                                 |

| 9       |                | х               | No Fix                                       | Intel $^{\circledast}$ I/O Controller Hub 10 (ICH10) Corporate Family System Reset with $\text{Intel}^{\circledast}$ Anti-Theft Technology |

| 10      |                | х               | No Fix                                       | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Corporate Family LAN_RST#<br>Assertion on Sx/Moff Entry                                   |

| 11      |                | х               | No Fix                                       | Intel $^{\ensuremath{\mathbb{R}}}$ I/O Controller Hub 10 (ICH10) Corporate Family Power Button Override Behavior                           |

| 12      |                | Х               | No Fix                                       | ICH10 Corporate ME SMBus/SMLink Clock Frequency                                                                                            |

| 13      | х              | х               | No Fix                                       | Intel $^{\ensuremath{\mathbb{R}}}$ I/O Controller Hub 10 (ICH10) Family SATA Low Power Device Detection                                    |

| 14      | х              | х               | No Fix                                       | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family PCI Express Function Disable                                                       |

| 15      | Х              | Х               | No Fix                                       | Intel $^{\ensuremath{\mathbb{B}}}$ I/O Controller Hub 10 (ICH10) Family SATA SYNC Escape                                                   |

| 16      | Х              | Х               | No Fix                                       | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family HPET Write Timing                                                                  |

| 17      |                | Х               | No Fix                                       | Intel <sup>®</sup> ICH10 Corporate May Not Detect Unsolicited SATA COMINITs                                                                |

| 18      | Х              | Х               | No Fix                                       | Intel <sup>®</sup> ICH10 SATA GEN3 Device Detection                                                                                        |

| 19      | Х              | Х               | No Fix                                       | Incorrect IRQ(x) Vector Returned for 8259 Interrupts With RAEOI Enabled                                                                    |

# **Specification Changes**

| Spec<br>Change<br>Number | SPECIFICATION CHANGES          |  |

|--------------------------|--------------------------------|--|

| 1                        | ROAEI options removal for OCW2 |  |

# **Specification Clarifications**

| No. | SPECIFICATION CLARIFICATIONS                                                          |  |  |  |  |

|-----|---------------------------------------------------------------------------------------|--|--|--|--|

|     | There are no Specification Clarifications in the revision of the Specification Update |  |  |  |  |

# **Documentation Changes**

| No. | DOCUMENTATION CHANGES                                                                         |  |  |  |

|-----|-----------------------------------------------------------------------------------------------|--|--|--|

| 1   | Add GPIO Reset Notes                                                                          |  |  |  |

| 2   | Correct EOIFD bit Definition                                                                  |  |  |  |

| 3   | Correct GPI_INV -GPIO Signal Invert register definition                                       |  |  |  |

| 4   | Update TBD defaults                                                                           |  |  |  |

| 5   | Update GPIO Note #4 in Section 3.2, Output and I/O Signals Planes and States                  |  |  |  |

| 6   | Make correction to Table 5-40, Causes of Host and Global Resets                               |  |  |  |

| 7   | Update bit definition for SECOND_TO_STS                                                       |  |  |  |

| 8   | Add foot note for all references to SPI Flash descriptors ICHSTRP0 and MCHSTRP0               |  |  |  |

| 9   | Remove GPI058 from Figure 2-1 Intel <sup>®</sup> ICH10 Interface Signals Block Diagram        |  |  |  |

| 10  | Add 1.1v for VccDMI in Table 2-24                                                             |  |  |  |

| 11  | Correct Bit Types for PCI Express UnCorrectable Error Severity register (UEV) Corporate ICH10 |  |  |  |

| 12  | Correct PCI Express DSTS register definition for bit 1 (NFED)                                 |  |  |  |

| 13  | Correct SMBCLK_CTL bit default value                                                          |  |  |  |

| 14  | Correct Table 2-24, Strap selection for Boot BIOS Destination                                 |  |  |  |

| 15  | Correct Section 5.13.6.5, Sx-G3-Sx, regarding possible wake events following a power failure  |  |  |  |

| 16  | Correct Section 10.1.45, Bit 0 definition                                                     |  |  |  |

| 17  | Correct Section 13.1.23, Bits 15:2 definition                                                 |  |  |  |

| 18  | Correct A20M# signal description                                                              |  |  |  |

| 19  | Update Section 8.2 in the Datasheet                                                           |  |  |  |

| 20  | Correct OUTSTRMPAY Register information                                                       |  |  |  |

| 21  | Correct INSTRMPAY Register information                                                        |  |  |  |

# Identification Information

# Markings

| ICH10<br>Stepping | S-Spec | Top Marking | Notes                 |

|-------------------|--------|-------------|-----------------------|

| Consumer          |        |             |                       |

| AO                | SLB8R  | AF82801JIB  | 82801JIB ICH10 (Base) |

| AO                | SLB8S  | AF82801JIR  | 82801JIR ICH10R       |

| Corporate         |        |             |                       |

| BO                | SLG8T  | AF82801JD   | 82801JD ICH10D        |

| BO                | SLG8U  | AF82801JDO  | 82801JDO ICH10DO      |

# Intel<sup>®</sup> ICH10 Device and Revision Identification

## Intel<sup>®</sup> ICH10 Corporate Device and Revision ID Table

| Device<br>Function | Description                                 | Intel <sup>®</sup><br>ICH10Dev<br>ID | ICH10<br>B0 Rev<br>ID | Comments                                                                           |

|--------------------|---------------------------------------------|--------------------------------------|-----------------------|------------------------------------------------------------------------------------|

| D31:F0             |                                             | 3A14h                                | 02h                   | ICH10DO                                                                            |

| D31:F0             | LPC                                         | 3A1Ah                                | 02h                   | ICH10D                                                                             |

|                    |                                             | 3A00h                                | 02h                   | Non-AHCI and Non-RAID Mode (Ports 0,1, 2<br>and 3)                                 |

| D31:F21            | SATA                                        | 3A02h                                | 02h                   | AHCI Mode (Ports 0-5)                                                              |

|                    |                                             | 3A05h <sup>3</sup>                   | 02h                   | RAID 0/1/5/10 Mode                                                                 |

| D31:F51            | SATA                                        | 3A06h                                | 02h                   | Non-AHCI and Non-RAID Mode (Ports 4 and 5)                                         |

| D31:F3             | SMBus                                       | 3A60h                                | 02h                   |                                                                                    |

| D31:F6             | Thermal                                     | 3A62h                                | 02h                   |                                                                                    |

| D30:F0             | DMI to PCI Bridge                           | 244Eh                                | A2h                   |                                                                                    |

| D29:F0             | USB UHCI #1                                 | 3A64h                                | 02h                   |                                                                                    |

| D29:F1             | USB UHCI #2                                 | 3A65h                                | 02h                   |                                                                                    |

| D29:F2             | USB UHCI #3                                 | 3A66h                                | 02h                   |                                                                                    |

| D29:F3             | USB UHCI #6                                 | 3A69h                                | 02h                   | Note: Device and Revision ID is always the same as D26:F2.                         |

| D29:F7             | USB EHCI #1                                 | 3A6Ah                                | 02h                   |                                                                                    |

| D26:F0             | USB UHCI #4                                 | 3A67h                                | 02h                   |                                                                                    |

| D26:F1             | USB UHCI #5                                 | 3A68h                                | 02h                   |                                                                                    |

| D26:F2             | USB UHCI #6                                 | 3A69h                                | 02h                   |                                                                                    |

| D26:F7             | USB EHCI #2                                 | 3A6Ch                                | 02h                   |                                                                                    |

| D27:F0             | Intel <sup>®</sup> High<br>Definition Audio | 3A6Eh                                | 02h                   |                                                                                    |

| D28:F0             | PCI Express* Port 1                         | 3A70h                                | 02h                   |                                                                                    |

| D28:F1             | PCI Express Port 2                          | 3A72h                                | 02h                   |                                                                                    |

| D28:F2             | PCI Express Port 3                          | 3A74h                                | 02h                   |                                                                                    |

| D28:F3             | PCI Express Port 4                          | 3A76h                                | 02h                   |                                                                                    |

| D28:F4             | PCI Express Port 5                          | 3A78h                                | 02h                   |                                                                                    |

| D28:F5             | PCI Express Port 6                          | 3A7Ah                                | 02h                   |                                                                                    |

| D25:F0             | LAN                                         | 3A7Ch <sup>2</sup>                   | 02h                   |                                                                                    |

| D23:F0             | VECI                                        | 3A51h                                | 02h                   | ICH10DO Only                                                                       |

| D22:F01            | SATA                                        | 3A55h                                | 02h                   | Virtualized SATA controller for use by Intel <sup>®</sup><br>Anti-Theft Technology |

#### Notes:

- 1. ICH10 contains multiple SATA devices. The SATA Device ID is dependant upon which SATA mode is selected by BIOS and what RAID capabilities exist in the SKU.

- LAN Device ID is loaded from EEPROM. If EEPROM contains either 0000h or FFFFh in the Device ID location, then 3A7Ch is used. Refer to the 82567 GbE Physical Layer Transceiver (PHY) Datasheet for LAN Device IDs.

- 3. The SATA RAID Controller Device ID may reflect a different value based on Bit 7 of D31:F2:Offset 9Ch

## Intel<sup>®</sup> ICH10 Consumer Device and Revision ID Table

| Device<br>Function | Description                                 | Intel <sup>®</sup><br>ICH10Dev<br>ID | ICH10<br>A0 Rev<br>ID | Comments                                                   |

|--------------------|---------------------------------------------|--------------------------------------|-----------------------|------------------------------------------------------------|

| D31:F0             | LPC                                         | 3A16h                                | 00h                   | ICH10R                                                     |

| D31.FU             | LPC                                         | 3A18h                                | 00h                   | ICH10 (Consumer Base)                                      |

|                    |                                             | 3A20h                                | 00h                   | Non-AHCI and Non-RAID Mode (Ports 0,1, 2<br>and 3)         |

| D31:F21            | SATA                                        | 3A22h                                | 00h                   | AHCI Mode (Ports 0-5)                                      |

|                    |                                             | 3A25h3                               | 00h                   | RAID 0/1/5/10 mode                                         |

| D31:F51            | SATA                                        | 3A26h                                | 00h                   | Non-AHCI and Non-RAID Mode (Ports 4 and 5)                 |

| D31:F3             | SMBus                                       | 3A30h                                | 00h                   |                                                            |

| D31:F6             | Thermal                                     | 3A32h                                | 00h                   |                                                            |

| D30:F0             | DMI to PCI Bridge                           | 244Eh                                | <mark>9</mark> 0h     |                                                            |

| D29:F0             | USB UHCI #1                                 | 3A34h                                | 00h                   |                                                            |

| D29:F1             | USB UHCI #2                                 | 3A35h                                | 00h                   |                                                            |

| D29:F2             | USB UHCI #3                                 | 3A36h                                | 00h                   |                                                            |

| D29:F3             | USB UHCI #6                                 | 3A39h                                | 00h                   | Note: Device and Revision ID is always the same as D26:F2. |

| D29:F7             | USB EHCI #1                                 | 3A3Ah                                | 00h                   |                                                            |

| D26:F0             | USB UHCI #4                                 | 3A37h                                | 00h                   |                                                            |

| D26:F1             | USB UHCI #5                                 | 3A38h                                | 00h                   |                                                            |

| D26:F2             | USB UHCI #6                                 | 3A39h                                | 00h                   |                                                            |

| D26:F7             | USB EHCI #2                                 | 3A3Ch                                | 00h                   |                                                            |

| D27:F0             | Intel <sup>®</sup> High<br>Definition Audio | 3A3Eh                                | 00h                   |                                                            |

| D28:F0             | PCI Express* Port<br>1                      | 3A40h                                | 00h                   |                                                            |

| D28:F1             | PCI Express Port 2                          | 3A42h                                | 00h                   |                                                            |

| D28:F2             | PCI Express Port 3                          | 3A44h                                | 00h                   |                                                            |

| D28:F3             | PCI Express Port 4                          | 3A46h                                | 00h                   |                                                            |

| D28:F4             | PCI Express Port 5                          | 3A48h                                | 00h                   |                                                            |

| D28:F5             | PCI Express Port 6                          | 3A4Ah                                | 00h                   |                                                            |

| D25:F0             | LAN                                         | 3A4Ch2                               | 00h                   |                                                            |

#### NOTES:

- 1. ICH10 contains two SATA devices. The SATA Device ID is dependent upon which SATA mode is selected by BIOS and what RAID capabilities exist in the SKU.

- LAN Device ID is loaded from EEPROM. If EEPROM contains either 0000h or FFFFh in the Device ID location, then 3A4Ch is used. Refer to the 82567 GbE Physical Layer Transceiver (PHY) Datasheet for LAN Device IDs.

- 3. The SATA RAID Controller Device ID may reflect a different value based on Bit 7 of D31:F2:Offset 9Ch.

| 1.           | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family UHCI Hang with USB Reset                                                                                                                                                         |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Problem:     | When SW initiates a Host Controller Reset or a USB Global Reset while concurrent traffic occurs on at least three UHCI controllers, the UHCI controller(s) may hang.                                                                              |  |  |

| Note:        | The issue has only been replicated in a synthetic reset test environment.                                                                                                                                                                         |  |  |

| Implication: | System may hang.                                                                                                                                                                                                                                  |  |  |

| Workaround:  | BIOS workaround available. Contact your Intel field representative for the latest BIOS information.                                                                                                                                               |  |  |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                 |  |  |

| 2.           | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family THRM Polarity on SMBus                                                                                                                                                           |  |  |

| Problem:     | When THRM#_POL (PMBASE+42h: bit0) is set to high, the THRM# pin state as reported to the SMBus TCO unit is logically inverted.                                                                                                                    |  |  |

| Implication: | If the THRM#_POL bit is set to high, an external SMBus master reading the BTI Temperature Event status will not receive the correct state of the THRM# pin. The value will be logically inverted. If THRM#_POL is set to low, value is correct.   |  |  |

| Workaround:  | None.                                                                                                                                                                                                                                             |  |  |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                 |  |  |

| 3.           | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family High Speed<br>(HS) USB 2.0 D+ and D- Maximum Driven Signal Level                                                                                                                 |  |  |

| Problem:     | During Start-of-Packet (SOP)/End-of-Packet (EOP), the ICH10 Consumer may drive D+ and D- lines to a level greater than USB 2.0 spec +/-200mV max.                                                                                                 |  |  |

| Implication: | May cause High Speed (HS) USB 2.0 devices to be unrecognized by OS or may not be readable/writable if the following two conditions are met:                                                                                                       |  |  |

|              | <ul> <li>The receiver is pseudo differential design</li> </ul>                                                                                                                                                                                    |  |  |

|              | <ul> <li>The receiver is not able to ignore SE1 (single-ended) state</li> </ul>                                                                                                                                                                   |  |  |

| Note:        | Intel has only observed this issue with a motherboard down HS USB 2.0 device using pseudo differential design. This issue will not affect HS USB 2.0 devices with complementary differential design or Low Speed (LS) and Full Speed (FS) devices |  |  |

| Workaround:  | None.                                                                                                                                                                                                                                             |  |  |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                 |  |  |

# 4. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family PET Alerts on SMBus

Problem:

When using the ICH Consumer SMBus for Platform Event Trap (PET) alerts on a system with the Intel<sup>®</sup> Management Engine (ME) enabled, the SMBus packet headers may be corrupted if all of the following conditions are met:

- SMBus slave is the target of an external PET generating master on SMBus/SMLink

- The ME is in the middle of MO-M1 transitions

- SMBus slave receives back-to-back PET alerts of which some PET alerts are incomplete (i.e. the packet is truncated to less than 6 bytes)

Note: This issue has only been observed under a synthetic test environment.

Implication: ME firmware may stop functioning, which could cause a system hang.

Workaround: None

Status: No Fix. For steppings affected, see the *Summary Table of Changes*.

## 5. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Consumer Family SMBus Host Controller May Hang

Problem: During heavy SMBus traffic utilization, the ICH10 Consumer SMBus host controller may attempt to start a transaction while the bus is busy.

*Note:* This issue has only been observed under a synthetic test environment.

Implication: May cause the SMBus host controller to hang.

- After boot:

- SMBus host controller transaction may not complete.

- External master transaction in progress targeting ICH10 Consumer SMBus slave may get NACK or timeout.

- There is no impact to any other transaction that was in progress by an external master.

- This issue has not been observed during boot as SMBus utilization tends to be light.

- Workaround: BIOS workaround available. Contact your Intel field representative for the latest BIOS information.

- Status: No Fix. For steppings affected, see the *Summary Table of Changes*.

| 6.           | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family LAN_PHY_PWR_CTRL<br>Functionality                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | LAN_PHY_PWR_CTRL output is driven low by the ICH10 during a host reset with or without power cycle for up to 3 RTC clock cycles due to the pin momentarily being configured as an output GPIO.     |

|              | <ul> <li>LAN_PHY_PWR_CTRL functionality requires a soft strap setting in the SPI descriptor<br/>and use of the integrated LAN controller in ICH10 with the Intel<sup>®</sup> 82567 PHY.</li> </ul> |

| Implication: | Functional failures such as system hangs or link loss with dropped packets have been observed when LAN_PHY_PWR_CTRL is tied to the LAN_DISABLE_N pin on the Intel 82567.                           |

| Note:        | There are no functional implications if the pin is configured as GPIO12.                                                                                                                           |

|              | For ICH10 Consumer based platforms:                                                                                                                                                                |

|              | <ul> <li>Intel ME-Enabled Platforms: An Intel ME FW workaround will be provided in the PC<br/>FW release.</li> </ul>                                                                               |

|              | <ul> <li>Both the Intel ME Disable bits in the SPI flash descriptor (ICHSTRP0<sup>*</sup> bit 0 &amp; MCHSTRP0<sup>*</sup> bit 0) must be set to 0 to enable the ME FW workaround.</li> </ul>      |

|              | <ul> <li>MCHSTRP0<sup>*</sup> bit 7 in the SPI flash descriptor can be set to disable all other ME<br/>FW based features while keeping the Intel ME FW workaround enabled.</li> </ul>              |

|              | <ul> <li>Non Intel ME-Enabled Platforms: Remove LAN_PHY_PWR_CTRL Support on the<br/>Platform.</li> </ul>                                                                                           |

|              | <ul> <li>Isolate the LAN_PHY_PWR_CTRL signal from the LAN_DISABLE_N pin.</li> </ul>                                                                                                                |

|              | <ul> <li>LAN_DISABLE_N has a weak integrated pull-up resistor and the Intel 82567<br/>PHY will always remained enabled with this implementation.</li> </ul>                                        |

| Note:        | ICHSTRP0 <sup>*</sup> and MCHSTRP0 <sup>*</sup> are in the SPI flash descriptor and programmed by <u>O</u> riginal <u>Equipment Manufactures</u> .                                                 |

|              | For ICH10 Corporate based platforms:<br>— None.                                                                                                                                                    |

| Status:      | ICH10 Corporate: Fixed. For steppings affected, see the <i>Summary Table of Changes</i> .                                                                                                          |

|              | ICH10 Consumer: No Fix. One of the proposed workarounds must be implemented. For steppings affected, see the <i>Summary Table of Changes</i> .                                                     |

| 7.           | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family High-speed USB 2.0<br>V <sub>HSOH</sub>                                                                                                    |

| Problem:     | ICH10 High-speed USB 2.0 VHSOH may not meet the USB 2.0 specification                                                                                                                              |

|              | The maximum expected VHSOH is 460 mV.                                                                                                                                                              |

| Implication: | None known. No Fix                                                                                                                                                                                 |

| Workaround:  | None.                                                                                                                                                                                              |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                  |

# 8. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Family 1.5 Gb/s SATA Signal Voltage Level

Problem: The ICH10 1.5 Gb/s SATA transmit buffers have been designed to maximize performance and robustness over a variety of routing scenarios. As a result, the ICH10 SATA 1.5 Gb/s (Gen1i and Gen1m) transmit signaling voltage levels may exceed the maximum motherboard TX connector and device RX connector voltage specifications (Section 7.2.1 of Serial ATA Specification, rev 2.5).

Implication: None Known.

Workaround: None.

Status: No Fix. For steppings affected, see the *Summary Table of Changes*.

- 9. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Corporate Family System Reset with Intel<sup>®</sup> Anti-Theft Technology

- Problem: If Intel Anti-Theft Technology is enabled on a platform, a CF9h write of 06h or 0Eh when the CF9h Global Reset bit is clear (D31:F0:ACh:bit 20) will cause the ICH10 to not complete the reset sequence properly.

- Implication: The ICH10 will complete a global reset after 4 seconds instead of an immediate host partition reset.

- Workaround: For ICH10 Corporate A0/A1 silicon none. For ICH10 Corporate B0 silicon a BIOS workaround must be implemented. See the ICH10 BIOS specification for details.

- Status: No Fix. For steppings affected, see the *Summary Table of Changes*.

#### 10. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Corporate Family LAN\_RST# Assertion on Sx/MOff Entry

Problem: If the integrated LAN controller is powered down (LAN\_RST# is asserted) in Sx/Moff, the SPI controller may not reset completely.

- Platforms that do not support the integrated LAN controller (LAN\_RST# is always asserted) are not impacted.

- Platforms that always power VccLAN3\_3 in S0-S5 are also not impacted.

- Implication: Upon platform wake, the integrated LAN Controller and Intel Management Engine may be unable to initialize or respond to PCI configuration space accesses which can cause the platform to hang with IERR# asserted by the CPU.

- Workaround: For platforms without Intel ME FW, one of the following options maybe be implemented:

- 1. Motherboard design must ensure LAN\_RST# asserts within 500 nanoseconds of SLP\_M# asserting on Sx/Moff entry or

- 2. VccLAN3\_3 must always be powered in S0-S5

Note: ICHSTRP0<sup>\*</sup> Bits 29:27 must be set to 000b if using one of the hardware based workarounds above.

For platforms with Intel ME FW:

This issue is resolved with Intel ME FW 1079 or later and requires ICHSTRP0\* bits 29:27 to be set correctly. See table below for platform configuration specific settings.

#### Table 1. ICHSTRP0 Bits 29:27 Setting Recommendations

| Motherboard LAN Power Configuration                                                            | ICHSTRP0* Bits 29:27 Settings |

|------------------------------------------------------------------------------------------------|-------------------------------|

| VccLAN3_3 is tied to VccSus3_3                                                                 |                               |

| Design ensures LAN_RST# asserts within 500<br>nanoseconds of SLP_M# assertion on Sx/MOff entry | 000b                          |

| VccLAN3_3 is tied to Vcc3_3                                                                    | 001b                          |

| VccLAN3_3 is powered of VccSus3_3 using WOL_EN and SLP_M# Or gate                              | 010b                          |

| Reserved                                                                                       | 011b-111b                     |

*Note:* ICHSTRPO<sup>\*</sup> is in the SPI flash descriptor and programmed by <u>Original Equipment</u> <u>Manufactures</u>.

Status: No Fix. For steppings affected, see the Summary Table of Changes.

#### 11. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Corporate Family Power Button Override

Problem: When in S0/1 after waking from a sleep state (S3-S5), triggering a power button override event will require the ICH10 PWRBTN# pin to be driven low for up to 9-10 seconds.

Note: ICH10 Corporate based platforms always require PWRBTN# to assert for 9-10 seconds to trigger a power button override event when the platform is in S3 or S4. This desired behavior ensures a wake event that is delayed by SLP\_S3# and/or SLP\_S4# stretching can be observed before unintentionally triggering a power button override event.

- Implication: Instead of taking 4-5 seconds to initiate a power button override event from S0/1, ICH10 corporate based platforms may require PWRBTN# to assert for up to 9-10 seconds.

- Workaround: The Intel<sup>®</sup> Management Engine's capability allows for a FW workaround which ensures a power button override event is triggered when PWRBTN# is asserted for 4-5 seconds in S0/1. This workaround has been included in the Intel<sup>®</sup> Management Engine Firmware 5.0 McCreary Production Candidate release.

Note: As long as ME FW (PC or later release) is included in the ME region on the SPI device the FW workaround will always be enabled, even if ME is disabled in the flash descriptor.

A workaround is not available for platforms that do not support ME FW.

Status: No Fix. For steppings affected, see the *Summary Table of Changes*.

#### 12. Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Corporate Family ME SMBus/SMLink Clock Frequency

- Problem: When ICHSTRPO<sup>\*</sup> bits 15:14 for ME SMBus Controller 2 and/or 13:12 for ME SMBus Controller 1 are set to 01 (EDS recommended value), the ME SMBus Controllers will drive the bus at 125 kHz instead of the expected 100 kHz.

- The host SMBus controller is not impacted by this issue. The host SMBus controller when acting as the bus master will drive the SMBus clock at 100 kHz.

- Implication: No known functional failures have been observed or reported to Intel.

Motherboard designers should evaluate the ability of all slave devices on the same interface as the ME SMBus controller to reliable received a 125 kHz clock input to determine impact to their platform.

| Workaround:  | Configure the ME SMBus Controllers to run at 80 kHz by setting ICHSTRP0 <sup>*</sup> bits 15:14 and/or 13:12 to 00 in the flash descriptor.                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:        | ICHSTRPO* is in the SPI flash descriptor and programmed by <u>O</u> riginal <u>E</u> quipment <u>M</u> anufactures.                                                                                                                                               |

| Status:      | No Plan Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                            |

| 13.          | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family SATA Low Power Device Detection                                                                                                                                                                           |

| Problem:     | Intel <sup>®</sup> ICH10 Family SATA Low Power Device Detection (SLPD) may not recognize, or may falsely detect, a SATA hot-plug event during a Partial or Slumber Link Power Management (LPM) state.                                                             |

| Implication: | This issue affects ICH10, ICH10R, ICH10D, and ICH10D0                                                                                                                                                                                                             |

|              | On systems which enable LPM, when a SATA device attached to the ICH10 is configured as External or Hot Plug capable, one of the following symptoms may occur:                                                                                                     |

|              | <ul> <li>Symptom #1: A Hot-Plug or External SATA device removal which is not detected<br/>results in the OS and Intel<sup>®</sup> Matrix Storage Manager console falsely reporting the<br/>device present, or incorrectly identifying an eSATA device.</li> </ul> |

|              | <ul> <li>Symptom #2: A false hot-plug removal detection may occur resulting in OS boot<br/>hang or ODD media playback hang.</li> </ul>                                                                                                                            |

| Workaround:  | A driver workaround is available.                                                                                                                                                                                                                                 |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                                 |

| 14.          | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family PCI Express Function Disable                                                                                                                                                                              |

| Problem:     | Intel <sup>®</sup> ICH10 Family PCI Express [1:16] Disable bit in Function Disable Register may not put the PCI Express Port into a link down state if a PCI Express Device is attached.                                                                          |

| Implication: | ICH10, ICH10R, ICH10D and ICH10D0:                                                                                                                                                                                                                                |

|              | PCI Express Port [1:6] with a PCI Express device attached may remain in L0 State and DMI may not be able to go into L1 State.                                                                                                                                     |

| Workaround:  | A BIOS workaround has been identified                                                                                                                                                                                                                             |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                                 |

| 15.          | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family SATA SYNC Escape                                                                                                                                                                                          |

| Problem:     | When a SYNC Escape by a SATA device occurs on a D2H FIS, the ICH10 does not set the PxIS.IFS bit to '1.' This deviates from Section 6.1.9 of the Rev 1.3 Serial ATA Advanced Host Controller Interface (AHCI)                                                     |

| Implication: | There is no known observable impact. Instead of detecting the IFS bit, software will detect a timeout error caused by the SYNC escape and then respond                                                                                                            |

| Workaround:  | None                                                                                                                                                                                                                                                              |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.§                                                                                                                                                                                                |

| 16.          | Intel <sup>®</sup> I/O Controller Hub 10 (ICH10) Family HPET Write Timing                                                                                                                                                                                         |

| Problem:     | A read transaction that immediately follows a write transaction to the HPET space may return an incorrect value                                                                                                                                                   |

| Implication: | Implementation is dependent on the usage model as noted below:                                                                                                                                                                                                    |

|              | For the HPET TIMn_COMP Timer 0 Comparator Value Register and HPET<br>MAIN_CNT—Main Counter Value Register the issue could result in the software<br>receiving stale data. This may result in undetermined system behavior.                                        |

|                                                                                              | Note: Timers [1:7] are not affected by this issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                              | For TIMERn_VAL_SET_CNF bit 6 in the TIMn_CONF—Timer n Configuration there is no known usage model for reading this bit and there are no known functional implications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                              | A write to a High Precision Timer Configuration (HPTC) register followed by a read to HPET register space may return all OxFFFF_FFFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Workaround:                                                                                  | A workaround is available.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Status:                                                                                      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17.                                                                                          | Intel <sup>®</sup> ICH10 Corporate May Not Detect Unsolicited SATA COMINITs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Problem:                                                                                     | Intel <sup>®</sup> ICH10 Corporate (ICH10D and ICH10DO) may not detect an unsolicited COMINIT from a SATA device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Implication:                                                                                 | The SATA device may not be properly detected and configured resulting in the device not functioning as expected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround:                                                                                  | A BIOS code change has been identified and may be implemented as a workaround for this erratum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Status:                                                                                      | No Plan to Fix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18.                                                                                          | Intel <sup>®</sup> ICH10 SATA 6.0 Gbps Device Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |